The goal of this part of the project is to design the state machine for a single cell in "The Game of Life" and then to connect these cells together into a 4x4 "toroidal" grid. There's a really good description of the game along with a neat applet for exploring the details of the game online at http://www.math.com/students/wonders/life/life.html. The key rules of the game are:

- A dead cell with exactly three living neighbors becomes alive (birth)

- A living cell with two or three neighbors stays alive (survival)

- In all other cases, a cell dies or remains dead (overcrowding or loneliness)

Your single cell has the following function header:

define LifeCell()(node[8] in; node init; node out){ ... }

The node[8] in array represents the status of each of your

neighbors (N,NW,W,SW,S,SE,E,NE): logic 1 means a neighbor is alive, logic

0 means a neighbor is dead. A cell's output node should be high if the

cell is alive and low if the cell is dead. The init input

should be used to determine the state a cell initializes to when the

(global) Reset signal is high. If init is zero the cell should be

initialized in a dead state, otherwise it should be initialized in a

living state. You must implement a life cell as a Moore-style State

Machine! Define your cell in lifecell.cast (the function

header is provided in this file). You should instantiate and test a single

LifeCell to make sure it behaves correctly according to the

rules of the Game of Life.

Once you're satisfied with that your cell is working correctly in

isolation you need to connect up a 4x4 "torroidal" grid of

LifeCells. This just means it's adjacency properties are like

those of a K-map (e.g. the top row is "adjacent" to the bottom row, the

leftmost column is "adjacent" to the rightmost column, and consequently

all corners are "adjacent"...). The definition of the grid is as follows:

define LifeGrid()(node[16] init; node[16] out){...}

The node[16] init vector specifies the initial state of

the grid, and the node[16] out vector should reflect the

state of the grid at any given time. When RESET is high the

LifeCell corresponding to the i-th grid cell should take on

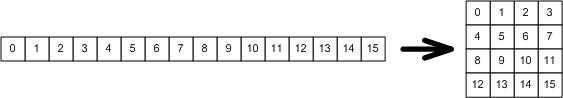

the value designated by init[i]. The vectors map onto the

grid in a "row major" format as shown in the following diagram:

Each generation should be computed in a single clock cycle. That is to

say, after the RESET period the state of the grid will be

well defined and thus the inputs to all state machines will be stable.

Some amount of time (less than a clock cycle) later all cells should

compute whether they should live or die in the next generation. At the

next positive edge, the state of all cells will change concurrently.

Subsequent generations should proceed similarly. Note that the inputs to

all state machines will change with the state (slightly later, actually).

You will need to understand the use of the global signals

CLK and RESET in order to do this part of the

project. Use only positive edge-triggered flip-flops for state-holding

elements. Define the LifeGrid in the provided file

lifegrid.cast (the function header is in this file).

Remember that this is a Moore machine and Reset is an input. If Reset changes during a cycle, it's effect takes place in the next cycle. If the output of your state machine changes within the same cycle as a change to Reset occurs, it isn't a Moore Machine and will lose a lot of points.