# **A** Active Messages Communication Architectures

The communication architecture plays a key role in the design of a parallel machine in that it is part of the interface between the machine designer and its users, in particular the language system developers. As such, the communication architecture must take many influences into account, from concrete constraints imposed by hardware technology to the more abstract requirements of parallel language systems. The central concern in Active Message is to address each of the four key communications issues (data transfer, send failure, synchronization, and network virtualization) at the right level of the system. The Active Messages approach is characterized by a particular choice of which aspects of communication are exposed to the language system and which are hidden within the architecture itself. Active Messages arrives at more efficient and versatile communication architectures that traditional approaches because communication and compiler optimizations are coupled more tightly than before.

It is tempting to solve the key communications issues "once and for all" within the communication architecture and to expose a conceptually simple interface to the language system. As argued in Chapter 5, this is in essence what traditional communication architectures attempt, and, unfortunately, it compromises the efficiency of communication because it requires either the complex general case to be solved at a low level or the programming models to be restricted. Active Messages takes a different approach and explores how the communication architecture can expose the key issues to the compiler such that a combination of low-level primitives (potentially accelerated in hardware) and high-level optimizations can be used.

Exposing more of the communication micro-architecture to the language system requires a change of mind-set in the definition of the communication architecture (in particular with respect to message passing). Active Messages is a framework which defines a *class of communication architectures* joined by a common central mechanism and a common set of trade-offs; Active Messages is specifically not a single standard communication architecture which remains invariant across all platforms, because such a standard cannot offer the desired versatility and efficiency.

The concept of Active Messages as a class of communication architectures is analogous to that of load/store architectures forming a class of instruction set architectures. Load/store architecture are predicated on a layering model very similar to that of Active Messages. In particular, both assume the use of high-level languages which are mapped to the architecture using a compiler and run-time substrate. When porting a HLL from one load/store architecture to another it is assumed that the code generator and run-time substrate require modification, although the essential algorithms, such as register allocation, remain the same. With Active Messages the notion of portability is similar: the algorithms to implement higher-level communication operations, such as fetch&add or a remote task enqueue) are portable while their implementation must be adapted to the peculiarities of the new platform. The le-

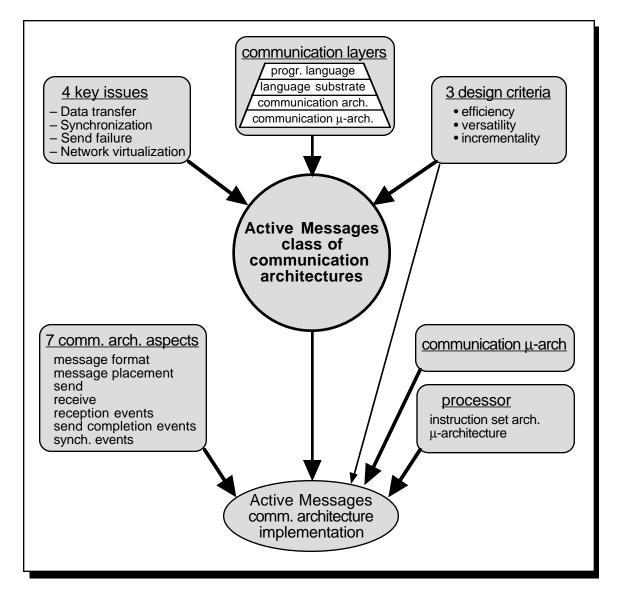

Figure 4-1: Influences on Active Messages communication architectures.

verage offered by Active Messages is a consistent view of communication from higher software layers that is portable and efficient.

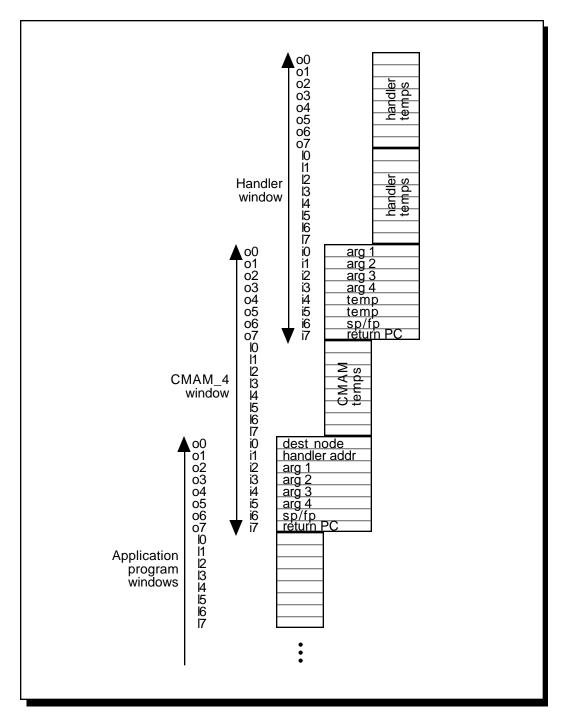

The relationship among the various components and concepts influencing Active Messages is depicted in Figure 4-1. The three design criteria and the communication layering model represent the abstract constraints on Active Messages as a class of communication architectures while the four key issues represent the concrete issues presented by communication micro-architectures in general. A particular instance of Active Messages must take the details of the communication and processor micro-architectures into account and is defined in terms of seven aspects: message format, message placement, send and receive operations, message reception and send completion events, and synchronization events.

The first section of this chapter defines the Active Messages class of communication architectures. Sections 4.2 and 4.3 describe two implementations of Active Messages on the nCUBE/2 and the CM-5, respectively. The two implementations take different positions on several communication architecture aspects to achieve high efficiency and versatility. Besides describing the implementation, the two

sections examine the performance of several micro-benchmarks closely to demonstrate the efficiency of the mapping onto the micro-architectures and to suggest further incremental improvements to support Active Messages better.

# 4.1 Active Messages

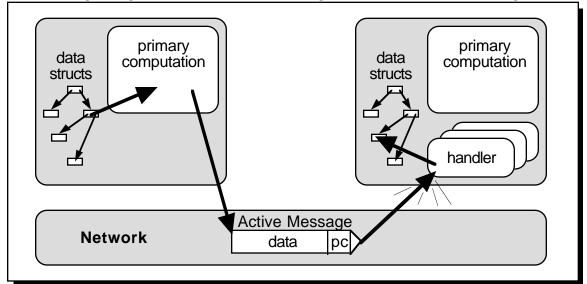

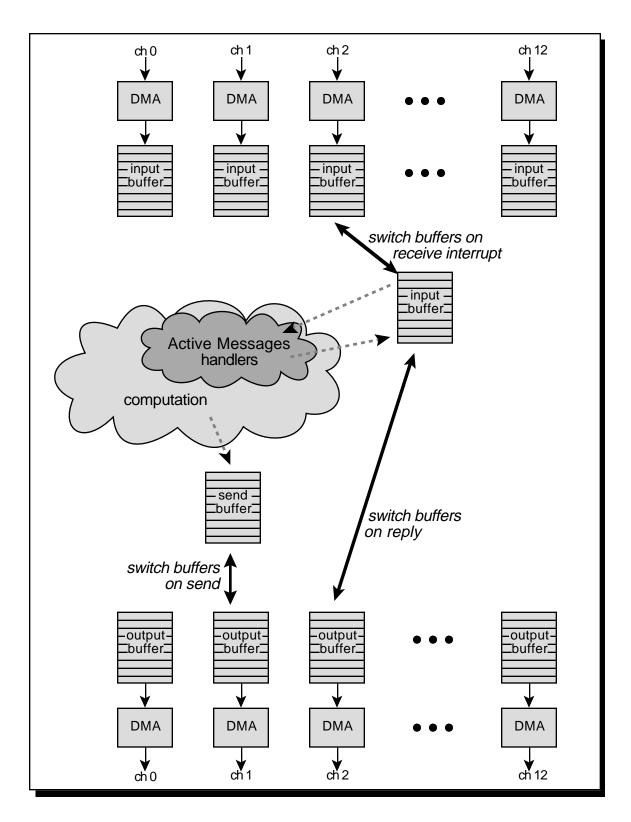

The key to both the versatility and efficiency of Active Messages lies in the ability to associate a small amount of computation in the form of a handler with the reception of each message. The handler is named in the message, typically by a pointer in the first word of the message, and is executed in the user process context immediately on message arrival. The underlying model is that at all times a computation is "going on" on each node and that this computation is interrupted by message arrival. The role of the message handler, illustrated in Figure 4-2, is then to transfer data into the computation's data structures and interact with the scheduling of computation or, alternatively, it may provide a remote service and send a reply message back.

# 4.1.1 Addressing the four key issues

Active Messages takes a strong position on the four key issues formulated in Section 3.3 (data transfer, synchronization, send failure, and network virtualization) with the goal of maximizing communication versatility and efficiency. This position manifests itself on the one hand through a set of micro-architectural characteristics that Active Messages generally exposes to the handlers (and the run-time substrate in general) to enable high-level optimizations. On the other hand, Active Messages imposes a set of restrictions on handlers in order to allow efficient implementation.

The general strategy employed to maximize efficiency is to take a compiled code approach in which message handling code is *directly executed*. This is in contrast to most systems in which messages are generally *interpreted* within the message layer<sup>1</sup>. While it is quite obvious that this direct execution approach provides the ultimate in versatility and efficiency during handler execution, care must be taken to keep the dispatch of handlers efficient as well. In particular, if handlers were allowed to perform arbi-

Figure 4-2: Active Messages model

The core idea in Active Messages is to use custom user-level handlers to dispose of messages quickly and optimally Each message carries at its head the address of the user-level handler which is executed on message arrival. The role of the handler is to get the message out of the network and transfer the data directly into the application data structures. In addition, the handler typically interacts with the scheduling on the node to enable the computation consuming the message data. Handlers may alternatively provide a small remote service and send a reply message back

<sup>&</sup>lt;sup>1.</sup> Active Messages, in some sense, interprets the head of the message as pointing to a handler and allows the handling of the rest of the message to be directly executed.

ACTIVE MESSAGES 47

trary computation the handler dispatch would be equivalent to a full context switch to a new thread of control. To avoid this cost, a crucial aspect of Active Messages is to restrict handlers by limiting the resources available, requiring handlers to execute quickly and to completion, and restricting communication patterns to one-way and request-reply communication to prevent network deadlock (i.e., handlers receiving a reply message are not allowed to send messages themselves).

The remainder of this subsection discusses in detail how Active Messages addresses the four key issues, explaining the advocated general strategy as well as some typical implementation-specific choices. A few related additional restrictions that are particular to Active Messages are also discussed.

#### Data transfer

Active Messages promotes direct access to the network interface from the run-time substrate whenever this is compatible with virtualizing the network. A typical Active Messages implementation exposes the micro-architecture and may even let the compiler manage data held in the network interface itself. This is in contrast with most message layers which prescribe a standard data transfer mechanism. Current micro-architectures differ considerably in their network interface access facilities (user-level vs. kernel-only access, memory mapped FIFOs vs. registers vs. DMA) such that an implementation-specific approach is more appealing. The rationale is that the run-time substrate can transfer the data in and out of the network interface just as fast as the message layer can, but that it can often move the data directly into the application data structures without intermediate buffering.

Active Messages strives to eliminate the buffering common in other message layers. While buffering is useful to absorb rate variations, this particular function is best done within the micro-architecture where efficient VLSI structures can be used. Buffering in software does not yield good performance and can easily lead to unbounded storage resources hidden within the message layer. In cases where the runtime substrate requires queueing of messages, the message handlers can allocate and manage the required buffers more efficiently than the message layer. They possess more information on the purpose of the queueing and can use a customized allocator. In addition, the allocation automatically occurs within the application's address space.

#### **Synchronization**

The Active Message handlers provide a very flexible means of synchronizing communication and computation in that a handler encodes an arbitrary interaction between the message and the ongoing computation. Beyond this versatility, the custom Active Message handlers also offer high efficiency. The synchronization mechanism can be tailored as part of the implementation of a parallel execution model and the compiler can special-case each handler to include only the synchronization operations required for the particular type of message received. These possibilities are used extensively in the compilation of TAM, discussed in Section 6.2.

Support for efficient atomic updates to scheduling data structures are key to enabling a close interaction between handlers and the computation. Active Messages ensures that updates within handlers are atomic by keeping handler execution atomic relative to the computation and relative to other handlers, e.g., if additional messages arrive during the execution of a handler their respective handlers are not started until the current one terminates. This implies that there is no notion of a handler "suspending" and "resuming" later. Scheduling events in the computation are made atomic relative to handlers either by using appropriate atomic instructions (if provided in the processor's instruction set) or by efficiently disabling handler execution during such updates. The details are implementation specific, but every Active Messages implementation must support such atomic primitives.

## Send failure

When attempting to send a message, the Active Messages implementation must be prepared to dispatch handlers for incoming messages to avoid deadlock. While this does not pose a problem for sends within the computation, it does imply that handlers attempting to send a reply message may have to be interrupted to allow the execution of nested handlers. This is the only exception to the atomicity of handler

execution: an attempt to reply breaks the atomicity. Typically this problem is dealt with by moving the reply to the end of the handler such that all critical operations occur before the reply. The alternate approach of buffering the received messages and executing the handlers later may require an unbounded amount of memory.

In order to prevent uncontrolled handler nesting, Active Messages limits communication patterns to requests and replies and distinguishes the two types of messages. Messages sent from the computation are *requests* and handlers receiving them may send *replies* back. Handlers receiving replies, however, may not send any messages. If a nested handler were allowed to reply, an arbitrary number of handlers could have to be nested. This situation can lead to a stack overflow or, from a different point of view, to a livelock of the lower handlers.

The solution adopted in Active Messages of limiting communication patterns relies on having (at least) two levels of priority in the network hardware, either using virtual channels to implement different message priorities or simply using two disjoint networks. This allows the deadlock/livelock problems to be solved by using the lower priority for request messages and the higher priority for replies and by dictating that a request handler can only send a reply message and a reply handler cannot send any message. This restriction ensures that:

- the communication graph is acyclic (computation  $\rightarrow$  request handler  $\rightarrow$  reply handler),

- when a request handler sends a reply it is required to accept incoming reply (i.e., high-priority) messages, but can ignore request (i.e., low-priority) messages, and

- a sequence of reply handlers can nest within a request handler one after another but request handlers are never nested within other handlers.

While Active Messages requires at least two priority levels to ensure deadlock/livelock free request-reply communication patterns, it is perfectly possible to provide additional priority levels to allow more flexibility.

## **Network virtualization**

Active messages lead to a relatively simple protection model: the destination handler address can be viewed as a global address which must be checked at the originating node for a valid destination and which is used at the receiving node to dispatch the correct handler within the appropriate address space. Typically this global address consists of a node address, a process id, and the handler start address.

Active Messages is targeted at closely coupled parallel systems and therefore assumes that the scheduling of communicating processors is coupled. In such systems, the communication latencies are several orders of magnitude smaller than the scheduling quantum and coordinating context switches among the processors ensures that the computation corresponding to arriving messages is currently running. On platforms where the micro-architecture can compare the process id of the message with that of the currently running process the scheduling coordination can be relaxed such that message arrival for a suspended process may occur. It is assumed that this remains infrequent enough such that it can be dealtwith using a bounded amount of queueing in the message layer.

#### Processor and storage resource restrictions

Given that handlers are executed atomically one after another it is important to keep their execution short enough to keep up with the network. For this reason the maximum execution time of a handler should be less than the reception time of its message. Note, however, that this is not an absolute requirement: in certain situations a handler may have to take special actions which take more time. This is acceptable as long as it remains an infrequent event and does not represent a communication bottle-neck.

An important issue is what storage resources should be made available to handlers. In particular, which processor registers can be used in handlers. The general Active Messages approach is to keep handler dispatch simple and to avoid unnecessary saving of processor state. Thus, handlers typically have access

ACTIVE MESSAGES 49

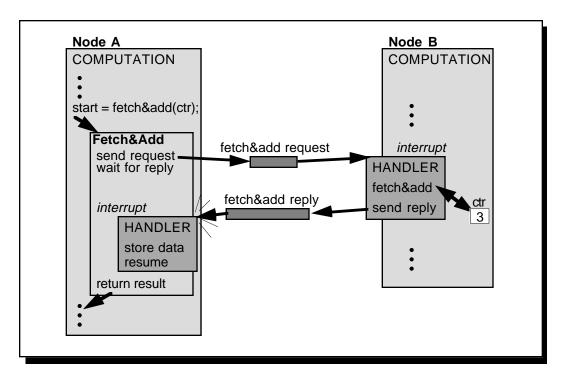

Figure 4-3: Components of a fetch&add implementation.

The computation on the initiating node formats a request Active Message and sends it to the fetch&add handler or the remote node. The request message consists of the remote address, the addend, and the information necessary to send the reply message. The execution of the handler interrupts the ongoing (and in this case typically unrelated) computation, performs the fetch&add, and sends a reply message with the result value back to the fetch&add reply handler. That handler saves the result value and signals the completion of the operation which causes the computation to pick-up the value and continue.

only to a few registers which are saved and restored as part of the dispatch. Handlers requiring additional resources may save and restore registers explicitly or, alternatively, the run-time substrate may permanently reserve a set of registers for handlers by not allocating these registers in the compilation process.

Regarding storage in memory, handlers can, in principle, dynamically allocate memory, but it is generally unwise to do so. Not only does this require the memory allocator to be made atomic relative to handlers, but also, if the memory allocation fails it is difficult to take corrective action within the handler. In particular, saving the message data is impossible (memory being full) such that the only remaining recourse is to send the message back with an error. The preferred approach is to preallocate the storage required by the handler and to pass a pointer to it in the message. The designs of Split-C and of TAM (described in Section 6.1 and Section 6.2, respectively) demonstrate how this preallocation can occur with very little overhead in the context of appropriately designed run-time substrates.

# 4.1.2 Active Messages example: Fetch&add

In this subsection, a simple fetch&add example shows the typical use of Active Messages in implementing simple higher-level communication operations.

The components involved in an implementation of a remote fetch&add primitive are depicted in Figure 4-3. The computation on the initiating node formats a request message and sends it to the fetch&add handler on the remote node. The request message consists of the remote address, the addend, and the information necessary to send the reply message. The execution of the handler interrupts the ongoing (and in this case typically unrelated) computation, performs the fetch&add, and sends a reply message with the result value back to the fetch&add reply handler. That handler saves the result

value and signals the completion of the operation which causes the computation to pick-up the value and continue.

In this simple example the computation on the source node busy-waits until the fetch&add completes. A more advanced implementation could suspend the current thread and switch to some unrelated computation while the fetch&add is in progress. In this case the reply handler would reenable the suspended computation by adding it to an appropriate scheduling queue.

An implementation of this simple fetch&add example would consist of the request and reply handlers, and of the code sending the request message. The latter can be a library function or it could be directly generated by the compiler. Concrete implementations on the nCUBE/2 and the CM-5 are presented in  $\S 4.2.3.3$  and  $\S 4.3.3.3$ , respectively.

# 4.2 Active Messages Architecture on the nCUBE/2

The send&receive architecture implemented in nCUBE/s Vertex system takes about 160µs end-to-end to transmit an 8-byte message among neighbor nodes. Yet, the message injection time and the routing accounts for only 14µs of these. Assuming an execution rate of about 5 MIPS the remaining 146µs represent over 700 instructions of overhead which, contrasted to the hardware description in Section 3.1, seems outrageously high: sending a message should involve entering the kernel, setting up the outgoing DMA and returning to the user, and receiving should involve a similar path through the kernel with possibly an additional interrupt routine. All in all, it seems that at most a few dozen instructions might be involved in transmitting a message!

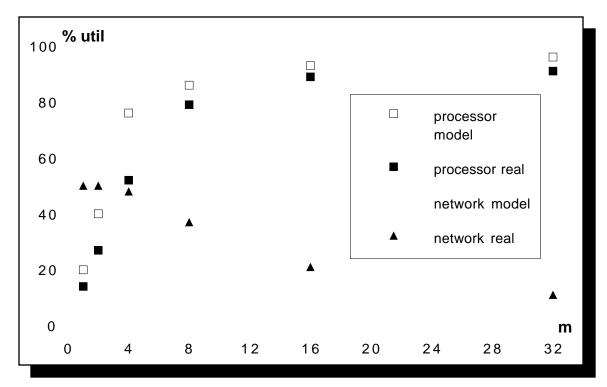

The goal of the Active Messages implementation is develop a message layer with the minimal possible communication overhead. The desire to integrate this implementation into the existing nCUBE/2 software environment presents a number of constraints summarized in Subsection 4.2.1. The highlights of the nCUBE/2 implementation, in particular its handling of the four key issues, is presented in Subsection 4.2.2. Subsection 4.2.3 describes the nCUBE/2 Active Messages communication architecture interface, and illustrates its use with an implementation of fetch&add. Subsection 4.2.4 follows with several micro-benchmarks measuring the performance of individual Active Message operations and demonstrating a five-fold reduction in communication overhead over Vertex's send&receive. Subsection 4.2.5 describes the implementation and shows that the performance of Active Messages is very close to the absolute limit of the hardware: a few dozen instructions indeed suffice and the resulting Active Messages layer succeeds in achieving low overhead and low latency communication with small messages. Measurements of the implementation reveal the bottlenecks in the current hardware and suggest avenues for further improvements. Subsection 4.2.6 measures the performance of two larger benchmarks based on matrix operations and Subsection 4.2.7 concludes the nCUBE/2 section.

While this section focuses exclusively on Active Messages, Section 5.1 contrasts Active Messages with send&receive such as implemented in Vertex and explains why send&receive is inherently a more expensive communication architecture.

# 4.2.1 Design constraints

On the nCUBE/2, the network can only be accessed via the on-chip DMA channels and the instructions to control DMA operation are privileged (refer to Section 3.1 for details). This means that all communication must involve the kernel which is also responsible for multiplexing network access between itself and all user processes. nCUBE's Vertex operating system allows multi-user operation using a space-sharing paradigm in which each parallel program is assigned to a power-of-two sub-cube and, in essence, owns that sub-cube for the duration of the program execution. While each node thus executes a single program at a time, the program can fork multiple processes on each node. Consequently, the responsibilities of the kernel are to enforce protection boundaries around each sub-cube and to potentially multiplex the network among multiple processes on each node.

To facilitate debugging, the Active Messages implementation is designed to coexist with, rather than replace, Vertex's send&receive communication architecture. At start-up, a user process has only access to the Vertex send&receive message passing primitives and must initialize Active Messages explicitly. From then on both sets of communication primitives are available.

Achieving this coexistence required careful integration of Active Messages into the existing kernel architecture and ultimately required certain compromises to be made. The most severe is the elimination of multitasking on nodes using Active Messages. This restriction was chosen for practical reasons: the Active Messages implementation as such already stresses the existing kernel architecture beyond its limits and nodal multitasking as implemented in Vertex is not of much use in parallel programs anyway (it was mainly designed to support transaction processing systems in which each node handles independent transactions and uses multiple processes per node to cover I/O latencies). A kernel redesign could allow multitasking with Active Messages at little overhead, but such a redesign was beyond the scope of the prototype effort discussed here.

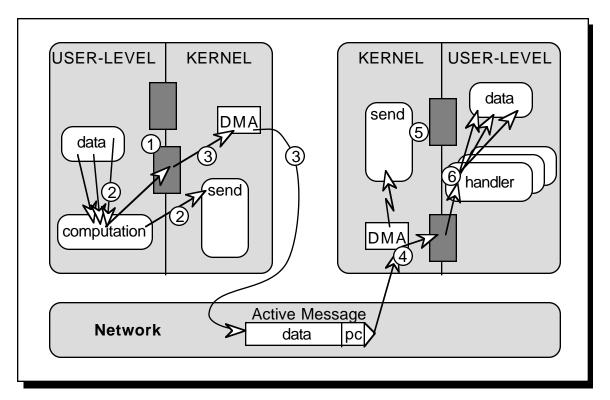

Figure 4-4: Steps involved in sending and handling an Active Message.

#### Implementation overview

Sending and handling an Active Message on the nCUBE/2 involves the following steps, illustrated in Figure 4-4:

- 1. the kernel provides a message buffer to the user process in user address space,

- 2. the user process composes the message in this buffer and calls Amsend which traps to the kernel,

- 3. the kernel verifies message destination and length, starts the appropriate DMA, sets-up a new message buffer, and returns to the user process,

- 4. the message arrives at the destination node into a DMA buffer and causes an interrupt,

- 5. the kernel re-initializes the input DMA to a new buffer, creates a stack frame for the Active Message handler in the user process' stack and returns—thereby starting the Active Message handler, and

- 6. the handler consumes the message, possibly sends a reply, and returns to the interrupted computa-

The implementation consists of the following parts:

- new kernel traps to send request and reply Active Messages,

- new message reception interrupt handlers to launch Active Message handlers,

- a user-level library interface between the kernel and Active Message handlers, and

- various modifications to the kernel, in particular to the scheduler, to accommodate Active Messages.

# 4.2.2 Design highlights

The major design issues in the Active Messages communication layer revolve around addressing the four key issues of Section 3.3. In addition, due to the fact that all communication has to involve the kernel, streamlining the user-kernel interface is of prime importance.

# 4.2.2.1 Streamlining the user-kernel interface

To keep the cost of Active Messages low the number of interrupts and traps must be kept to a minimum. This raises the question whether the nCUBE/2's facility of sending the message header and the data in separate message segments (cf. Subsection 3.1.3, page 29) is worth it. The benefit would be that on the receiving end the information in the header can be used to set-up the DMA for the data. If the headers are kept small, preallocating their buffer space is simple and the data itself can potentially be transferred directly into the application memory, e.g., buffer allocation costs can be kept low or eliminated altogether. The problem, however, is that the arrival of the header causes an interrupt (to set-up the DMA for the data). Unless the kernel busy-waits for that DMA to complete—which can take a long time for large messages—another interrupt must be signaled at the end of the data DMA. On the sending side the problem is similar and typically requires one trap to send the header and one interrupt to initiate the data DMA. (Note, however, that if the outgoing channel is idle the kernel can conceivably busy-wait for the header to be sent.) The bottom line is that using two message segments requires twice as many traps and interrupts than using a single segment.

The Active Messages implementation avoids interrupts completely on the sending side by sending only single-segment messages and by not queueing outgoing messages if the network is backed-up. The send kernel trap simply busy-waits for the previous message to go out and then sets-up the new DMA. The result of the efforts to minimize the number of privilege level switches is that, in the normal case:

- a message send never involves more than one kernel trap,

- · a message reply involves one trap, and

- a message reception involves one interrupt or trap.

If the network is backed-up a reply from within a handler can involve several traps (as explained in more detail below). In addition, the first of a series of messages arriving during handler execution involves both, an interrupt and a kernel trap.

## 4.2.2.2 Data transfer

The Active Messages implementation reduces buffering to a minimum. On the nCUBE/2, it is not possible to forego intermediate buffering because all DMA data transfer has to be initiated by the kernel. Exposing the network interface to user-level is therefore impossible. The necessary DMA buffers are pre-allocated and buffer allocation and de-allocation is reduced to interchanging two pointers.

The DMA buffers are directly mapped into the user process address space in order to avoid copying of the message data from a system buffer into user space. With the simplistic memory management scheme supported by the nCUBE/2—only four contiguous data segments per user process—it is not practical to map individual buffers into the user address space. Instead a shared buffer area is pre-allocated in the data segment of the user process and used for all buffers.

The Active Messages implementation limits the message size and uses fixed-size buffers. The size is chosen such that the overhead of splitting-up larger messages is small compared to the message injection time, i.e., such that the message size limit does not affect peak communication bandwidth significantly.

To determine the minimal number of buffers required it is important to remember that Active Messages guarantees, by definition, that buffers of arriving messages can be re-used immediately after handler execution, and that the message layer blocks the sender until the outgoing network port is available, i.e., no queueing of outgoing messages occurs. Thus the minimal number of buffers is:

each input DMA requires a buffer set-up for reception,

- each outgoing DMA has one buffer being sent<sup>2</sup>,

- one output buffer is "being filled" by the computation, and potentially

- one input buffer is "being consumed" by an Active Message handler,.

Figure 4-5 shows the resulting buffer system with it three possible state transitions:

- on message reception the incoming DMA input buffer is switched with the user input buffer,

- on message send the user output buffer is switched with the outgoing DMA output buffer, and

- on message reply the user input buffer is switched with the outgoing DMA output buffer.

The last point implies that a handler must compose a reply message in its input buffer as the output buffer may already contain a partial message. Using the input buffer to compose the reply message has the benefit that information from the request message that is returned to the sender (e.g., to identify the reply) does not need to be copied if the message formats are designed appropriately.

## 4.2.2.3 Virtualizing the network

Given the strict space-sharing used by the Vertex operating system, virtualizing the network simply consists of ensuring that user messages are confined to the process' subcube. This requires a simple destination node check. In addition, the message length must be limited to the size of the buffers to avoid overrun at the destination.

Unlike traditional message passing systems where the user process controls message buffers and indicates to the kernel which buffer to send or receive next, the Active Message buffering scheme lets the kernel control the buffers and dictate which one the user process must consume and in which one it must compose the next message. This role reversal has the benefit that the user process never passes a pointer to the kernel which the latter would have to validate. The kernel can pre-translate all buffer addresses to user virtual addresses when the buffers are initially allocated such that it can pass these pre-translated addresses to the user process whenever necessary.

The disadvantage of this scheme is that the user process cannot send from its data structures without copying the data. Given that it is only rarely practical to add the Active Message headers in-place in front of the data to be sent this does not seem to be a severe restriction. Moreover, adding the capability of sending an arbitrary buffer for the cases where the advantage of eliminating the data copy outweighs the costs would be straightforward. Note that the overhead not only consists of the required buffer address validation, but also of the send completion interrupt required to notify the user process that the data has been sent and can be modified again. Such a direct send would validate the buffer addresses and set-up the outgoing DMA engine without changing the normal buffer associated with that DMA engine and without otherwise interfering with normal operation.

#### 4.2.2.4 Send failure

On the nCUBE/2, the kernel and the user process must cooperate to deal with send failure within reply handlers. This need arises from the fact that the nCUBE/2 does not provide multiple priority levels for messages which would allow a straightforward implementation of deadlock/livelock-free request-reply communication patterns. The Active Messages implementation distinguishes between request and reply messages and uses separate kernel traps for each category. When sending a reply, the kernel attempts to inject the message into the network. If it is unsuccessful after a short period of time it simply returns to the handler with an error indication. At that point the handler is expected to free the reply message buffer and trap back to the kernel to accept incoming messages and nest their respective handlers onto the user stack. Eventually these nested handlers terminate and the original request handler can attempt to send the reply message again. Unfortunately the nesting depth cannot be limited, thus a stack over-

<sup>&</sup>lt;sup>2.</sup> The strict minimum would be one buffer for all outgoing DMA channels, but that does not bear any significant advantage.

Figure 4-5: nCUBE/2 Active Messages buffer management scheme.

The buffering scheme minimizes buffer management. All buffers are pre-allocated and mapped into user-space. Or send, buffer management consists of exchanging the buffer holding the message with the DMA engine buffer. Or receive, the DMA buffer is switched with the buffer of the previously received message.

flow could cause termination of the program. It is recommended that handlers issuing reply messages use as small a stack frame as  $possible^3$ .

The solution of returning an error to the handler and have *it* free the reply message buffer was chosen to avoid user memory allocation within the kernel. In addition, the handler can decide whether it is best to save the reply message itself, or whether it is better to save a descriptor of the request. For example, while it is preferable to save the acknowledgment reply of a block-write it is probably better to save a descriptor for a block-read request.

## 4.2.2.5 Synchronization

In order to allow atomic sections in the computation, the kernel must somehow be notified when the program enters and leaves such a critical section so it can prevent Active Message handlers from interrupting. In addition, while the kernel must manage the DMA buffers it does not get notified of all the buffers state transitions. In particular, the kernel does not automatically know when an output DMA completes and thus the corresponding buffer becomes available again. It also does not know when an Active Message handler completes at which point its buffer becomes available and the next handler can be dispatched. While all these events could simply be signalled via kernel traps and interrupts, the Active Messages implementation uses a sophisticated user-kernel handshake in order to avoid the high cost of the straightforward solution.

The user-kernel handshake is based on a set of flags in a memory region shared by the user process and the kernel (the same region as for the DMA buffers is used). The user process controls two atomicity flags indicating the execution of an Active Message handler or of a critical section. If messages arrive while one of these flags is set the kernel ignores the message, sets a message pending flag and lets the user process proceed. At the end of the handler or critical section the user process checks the message pending flag and traps into the kernel if it is set. This scheme eliminates kernel traps to enable or disable interrupts which would be necessary in a more traditional approach.

Another difficulty arises from the fact that Active Message handlers are executed "at interrupt time" and that to guarantee the atomicity of handlers further interrupts must be prevented. In order to avoid deadlock in the case of a non-terminating Active Message handler the kernel starts a short timer whenever it disables message interrupts. Should the timer be exhausted without the user process having made any progress (e.g., completing the handler or leaving the critical section) the user process is considered to violate the protocol and is aborted. Given that all user-level communication is restricted to within the sub-cube "owned" by the parallel program slow handlers cannot hurt the performance of other programs. Setting the timer to a generous value (e.g., several hundred microseconds) is therefore acceptable as it really only needs to prevent a node from becoming unreachable to the point where it is impossible to force termination of the program.

<sup>&</sup>lt;sup>3.</sup> In hindsight, a different implementation strategy which deals with the reply failure problem using flow-control should have been used.

#### User-kernel handshake details

The user-kernel handshake uses three variables in memory shared between the user process and the kernel:

| RetPC  | PC of interrupted computation, set by kernel  |                                                              |  |  |  |  |  |

|--------|-----------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| RetPSW | PSW of interrupted computation, set by kernel |                                                              |  |  |  |  |  |

| Flags  | Handshake flags:                              |                                                              |  |  |  |  |  |

|        | inHandler:                                    | handler currently executing,<br>set by kernel, reset by user |  |  |  |  |  |

|        | inCritical:                                   | critical section currently executing, set/reset by user      |  |  |  |  |  |

|        | msgPending:                                   | additional message(s) pending,<br>set/reset by kernel        |  |  |  |  |  |

On message reception, the interrupt handler starts the Active Message handler only if both inHandler and inCritical flags are clear. If either one is set the interrupt handler delays the message by turning off the DMA to clear the interrupt cause, starting the time-out, setting the msgPending flag, and returning to the user. When an Active Message handler or a critical section completes it checks the msgPending flag and traps back into the kernel to pick-up the pending message.

## 4.2.3 Communication architecture interface

From the description of the design highlights it may seem that the Active Messages communication architecture is very complicated and requires its users to thoroughly understand the kernel-level implementation. Fortunately this is not the case: part of the implementation is a user-level library that hides the details of the user-kernel handshakes and presents a simple interface. This Subsection describes this interface to the nCUBE/2 Active Messages communication architecture. It is intended as a self-contained unit and therefore repeats some information presented above.

#### **4.2.3.1** Overview

The nCUBE/2 Active Message layer implements an Active Messages communication architecture optimized for moderate sized messages with low-latency. On message arrival the handler referenced by the message is executed at interrupt time.

## Message format

The maximum message size is fixed at boot time and on the order of one Kbyte. The first word of the message holds the address of the handler and the remainder is available for data.

#### Message placement

Messages are composed in memory in the outgoing buffer whose address is indicated by a global variable set by the message layer. Similarly, during handler execution, a global variable points to the memory buffer holding the received message. Replies are composed in the same buffer that the request message was received in. The rationale is that a request typically contains information to be returned in the reply. Using the same buffer can avoid copying this return information.

# Message send and receive operations

The Amsend call sends the request message held in the outgoing buffer. Amreply similarly send the reply message held in the incoming buffer. No particular receive operation is provided as the handler is invoked automatically and is passed the address of the received message.

## Message reception events

Handlers interrupt the ongoing computation and are nested on the normal execution stack, i.e., appear as if a spontaneous function call had been executed. The message buffer address is passed as an argument and is also available in a global variable. The message length is unknown; it may be placed in the message if the handler needs to know. The handler must "consume" the message quickly and return; as soon as the handler terminates, the message buffer is reused by the message layer.

## **Synchronization**

Handler execution is atomic in that a message arriving during the execution of a handler is delayed until the handler terminates. To delay a message the message layer disables network interrupts in hardware. To safeguard from network deadlock, a timer is started when interrupts are disabled and the user process is aborted if the Active Message handler does not complete within a millisecond. Critical sections in the computation can be formed by setting a flag in memory to disable message reception.

# **Send completion**

In principle Active Messages restricts communication patterns to requests and replies and expects the micro-architecture to provide some form of message priorities so that such patterns can be implemented deadlock and livelock free. While the nCUBE/2 does not support priorities of any form in hardware and there is little advantage to this restriction, the implementation still distinguishes between request and reply messages to help avoid stack overflow due to excessive handler nesting. This allows applications to guarantee that no overflow can occur by limiting the number of requests outstanding to any one processor at the same time and allocating enough stack space.

When sending a request message the message layer accepts incoming messages and dispatches the appropriate handlers. When sending a reply message, i.e., from within a handler, the message layer does not accept incoming messages. If the reply message cannot be injected into the network because of congestion the message layer returns an error to the handler. At that point the handler is expected to free the reply buffer and call the message layer to accept incoming messages, nesting the respective handlers.

#### 4.2.3.2 Interface definition

Send request and reply Active Messages

Amsend sends the message pointed-to by AmsendBuf and sets AmsendBuf to a new free buffer for the next message. At the destination the first word of the message is interpreted as the Active Message handler.

AMreply attempts to send the message pointed-to by AMreplyBuf and sets the latter to a new free buffer for another message. At the destination the first word of the message is interpreted as the Active Message handler. AMreply returns 0 if the message injection succeeds and a non-zero result otherwise. In case of failure, the handler must save the message buffer contents and call AMrecv to initiate handling of pending messages. When AMrecv returns the handler may attempt another AMreply. Note that AMrecv should only be called when a reply fails.

#### Handler execution

```

typedef void AMhandler(void *buffer);

inline void AMdisable(void) { AMflags |= inCritical; }

void AMenable(void);

```

The handler is called as if a spontaneous function call had been executed with the first argument pointing to the received message (AMreplyBuf points to the message as well). The message length is unknown. After "consuming" the message the handler simply returns at which point the message buffer is reused by the message layer. Critical sections in the computation can be formed by using AMdisable and Amenable to control handler execution.

# 4.2.3.3 Example of use: Fetch&add

The fetch&add example introduced in Subsection 4.1.2 is easily implemented with Active Messages on the nCUBE/2. Figure 4-6 shows the complete implementation consisting of an internal synchronization variable, a stub to format and send a fetch&add request message, the request handler performing the fetch&add and sending a reply message back, and the reply handler completing the operation. In this simple implementation the processor busy-waits after launching the request message awaiting the reply. A more sophisticated version could continue computing, possibly launching additional fetch&adds and only checking the flag when the result is actually needed. In such a case the message would have to contain an synchronization identifier so that each reply can be matched with the correct request.

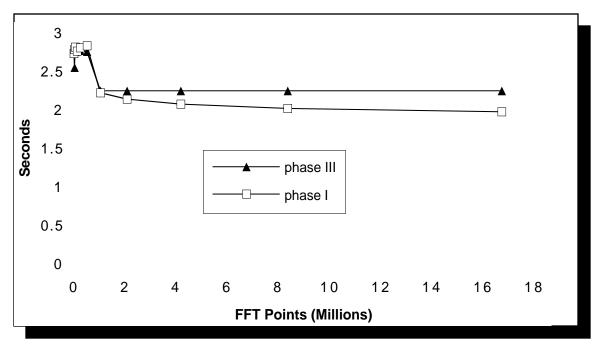

#### 4.2.4 Micro-benchmarks

The objective of the micro-benchmarks is to obtain detailed best-case timings of the various Active Messages operations. The benchmarks are organized around a simple *signal* primitive which sends an Active Message to a handler incrementing a counter whose address is passed in the message. The message length can be varied from 1 to 256 words although no data is moved in and out of the buffer. The benchmark operates in four phases:

- 1. Node 0 sends N4-word signal messages back-to-back to node 1. The total time divided by N gives the message handling overhead<sup>4</sup>.

- 2. Node 0 sends *N*4-word signal messages back-to-back to node 1 and node 2, alternating between the two. The total time divided by *N* gives the sending overhead.

- 3. Node 0 sends one 4-word message to node 1 which replies immediately, this is repeated N times. The total time divided by N gives the round-trip delay. This phase is repeated for nodes  $2^{i}$ -1,  $\not=1..10$  and serves to verify the parameters of the network hardware.

- 4. Node 0 sends N256-word signal messages back-to-back to node 1. The total time divided by N allows to verify the network injection time.

The results of running these benchmarks on a 1024-node nCUBE/2 system are shown in Table 4-1 and demonstrate that the Active Messages implementation achieves almost a 7-fold reduction in overhead over send&receive from 194 $\mu$ s to 28 $\mu$ s! Phase 3 shows an average increase in the round-trip delay of 4.5 $\mu$ s per extra hop which (divided by 2 to account for the round-trip) corresponds to the 2.2 $\mu$ s routing time claimed by the manufacturer. The per-byte injection time is also as expected.

The minimal round-trip time of  $76.2\mu s$  is unfortunately not easily explained. The overhead of one message (28µs) plus the injection time (5.9µs for 3 words with an end-of-message byte) yields a round-trip time of  $67.8\mu s$ . The missing  $8.4\mu s$  are probably due to a combination of delays in the DMA start-up and the memory system. The memory cycles stolen by the DMA are relatively expensive because they cannot use the single cycle DRAM page mode access.

<sup>&</sup>lt;sup>4.</sup> Really: the maximum of the sending and handling overheads. It turns out that handling is more expensive.

```

# Synchronization variable

1: typedef struct { volatile int flag, value; } fetch_add_sync;

# Message format

2: typedef union {

3:

struct {

request message

4:

request handler

handler;

void

fetch_add_sync *sync;

synchronization variable

5:

int *addr, incr;

6:

address to increment

7:

int

ret_node;

node to send reply to

8:

} req;

9:

struct { reply message

10:

reply handler

handler;

void

11:

fetch_add_sync *sync;

sync. variable (same location as in request message)

12:

fetch&add result

int.

value;

13:

} repl;

14: } fetch_add_msg;

# Initiate fetch&add request, wait for completion and return result

15: int fetch_add(int node, int *addr, int incr) {

16:

fetch_add_sync sync;

synchronization variable

17:

fetch_add_msg *msg = AMsendBuf;

compose request message

18:

msg->req.handler = fetch_add_h;

msg->req.sync = &sync;

19:

20:

msg->req.addr = addr; msg->req.incr = incr;

21:

msg->req.ret_node = MYPROC;

22:

init synchronization flag

sync.flag = 0;

23:

AMsend(node, sizeof(fetch_add_msg.req)); send request

24:

busy-wait for completion

while(sync.flag != 1) ;

25:

return sync.value;

return result

26: }

# Handler for fetch&add request

27: void fetch_add_h(fetch_add_msg *msg) {

fetch_add_msg temp;

... in case of reply failure

29:

int ret_node = *msg->req.ret_node;

30:

int value = *msg->req.addr + msg->req.incr; perform fetch&add

31:

*msg->req.addr = value;

32:

msg->repl.handler = fetch_add_rh;

compose reply message

33:

msg->repl.value = value;

34:

while(AMreply(ret_node, sizeof(fetch_add_msg.repl))){

35:

temp.repl = msq->repl; msq = &temp; reply failure: save message

36:

AMrecv();

... handle incoming messages

37:

... and try again

38: }

# Handler for fetch&add reply

39: void fetch_add_rh(fetch_add_msg *msg) {

40: msg->repl.sync->value = msg->repl.value;

41:

msg->repl.sync->flag = 1;

42: }

```

Figure 4-6: Fetch&add implementation with nCUBE/2 Active Messages.

| Phase | Metric                         | Active Messages time | Send&receive<br>time |  |  |

|-------|--------------------------------|----------------------|----------------------|--|--|

| 1     | receive overhead               | 15.0µs               | 102μs                |  |  |

| 2     | send overhead                  | 13.1µs               | 92µs                 |  |  |

| 3     | round-trip node 0 to node 1    | 76.2µs               | 328µs                |  |  |

|       | round-trip node 0 to node 3    | 80.7µs               | 334µs                |  |  |

|       | round-trip node 0 to node 7    | 85.2µs               | 337µs                |  |  |

|       | round-trip node 0 to node 15   | 89.1µs               | _                    |  |  |

|       | round-trip node 0 to node 31   | 94.0µs               | _                    |  |  |

|       | round-trip node 0 to node 63   | 98.5µs               | _                    |  |  |

|       | round-trip node 0 to node 127  | 102.8µs              | _                    |  |  |

|       | round-trip node 0 to node 255  | 106.9µs              | _                    |  |  |

|       | round-trip node 0 to node 511  | 111.6µs              | _                    |  |  |

|       | round-trip node 0 to node 1023 | 116.3µs              | _                    |  |  |

| 4     | per-byte injection time        | 0.45μs               | 0.45µs               |  |  |

Table 4-1. Micro-benchmark results for Active Messages on the nCUBE/2.

## 4.2.4.1 Performance modeling

The timings gathered with the micro-benchmarks can be expressed more conveniently using the performance models introduced in Section 2.3. Converting  $\mu s$  to clock cycles yields around 700 CPM (clocks per message) for small messages. The message start-up cost  $\alpha$  is 28 $\mu s$  and the per byte cost  $\beta$  is 0.45 $\mu s$ . The maximum communication throughput  $R_{\infty}$  is 2.2Mb/s and half this throughput is achieved with a message length  $N_{1/2}$  of 62 bytes. Table 4-2 expresses the performance in terms of the LogP model. Given that LogP assumes fixed size messages, the table shows two sets of values, one for short 8-word messages and one for long 1Kbyte messages.

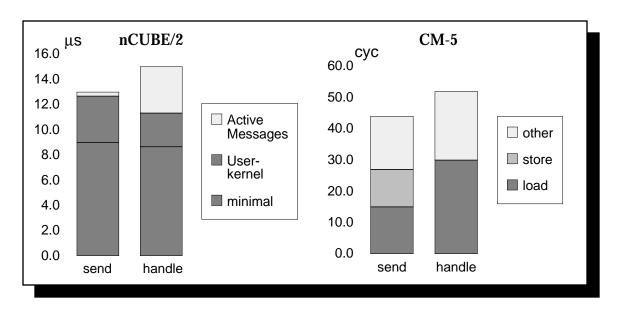

# 4.2.5 Active Messages implementation

While the micro-benchmarks show an impressive performance improvement of Active Messages over send&receive, it is not immediately obvious why Active Messages are not even faster: the entire path to send a signal message, as used in the micro-benchmark above, is only 24 instructions long. How can these take 260 clock cycles (13µs at 20Mhz) for a CPI of almost 11 when the average CPI is close to 4? The situation on message reception is similar: 37 instructions take 300 clock cycles (15µs at 20Mhz) for a CPI of over 8. The paragraphs below discuss the interesting phenomena in the micro-architecture that explain the observed performance and that point out simple hardware fixes that would increase the performance substantially. Given that the relevant parts of the implementation are short they can be shown here.

| Sho | Short 8-word (32-byte) messages |                                                                                                                                                                |  |  |  |  |

|-----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| L   | = 25µs                          | Injection for 8 word message + 5 hops = 14.4μs+10μs (5 hops is avg. distance for <i>P</i> =1024)                                                               |  |  |  |  |

| o   | $= 14 \mu s$                    | (Send overhead + Recv overhead) / $2 = (15\mu s + 13\mu s)/2$                                                                                                  |  |  |  |  |

| g   | = 14μs                          | <i>g</i> =0, possibly a bit larger On avg. the network volume is 2 messages per node, given that $L \approx 20$ there should be little contention              |  |  |  |  |

| P   | = 21024                         |                                                                                                                                                                |  |  |  |  |

| Lo  | ng 256-word (                   | (1K-byte) messages                                                                                                                                             |  |  |  |  |

| L   | = 471µs                         | Injection for 256 word message + 5 hops = $461\mu s + 10\mu s$ (5 hops is avg. distance for $P=1024$ )                                                         |  |  |  |  |

| o   | $= 14 \mu s$                    | (Send overhead + Recv overhead) $/ 2 = (15\mu s + 13\mu s)/2$                                                                                                  |  |  |  |  |

| g   | ≥ 236µs                         | $g \ge L/2$ , probably significantly larger On avg. the network volume is 2 messages per node, but $g$ should be even larger to account for routing contention |  |  |  |  |

| P   | = 21024                         |                                                                                                                                                                |  |  |  |  |

Table 4-2. LogP parameters for nCUBE/2 Active Messages

#### 4.2.5.1 Message send

The 15-instruction path taken through the kernel when sending an Active Message is shown in Figure 4-7 with Table 4-3 defining the kernel variables used. Noteworthy details are:

- The first 4 instructions adjust the destination node address for the sub-cube origin and store it at the front of the message buffer. The message length is limited in instruction 6 through a simple mask.

- A difficulty with the nCUBE/2 routing is that the message must be initially sent out on the correct network port. Furthermore, while the DMA instructions require the register number corresponding to the chosen port, the information in status registers has one bit per port and thus must be masked appropriately. In order to determine all the required values quickly, the kernel maintains a table mapping the node number to a port index into several tables, one for each type of value needed (lines 5, 8, 10, 11, 12, and 14).

- The entire instruction sequence contains only a single conditional branch (instruction 9). This branch is nominally taken if the output DMA engine is busy. However, the node mapping tables are set-up such that the local node address and the addresses of nodes beyond the user processes' sub-cube are mapped into bits of the status register which are always zero. Thus the branch is also taken for messages which should be looped-back on the local node and for messages causing an error.

- Buffer management is reduced to flipping two pointers in instructions 12 and 14.

- The physical-to-virtual address adjustment for the message buffer addresses is precomputed and can be applied in a single instruction (line 13).

From the code it becomes clear that one of the factors contributing to the observed CPI for this instruction sequence is the high frequency of complex addressing modes and of operands in memory. To help the analysis, Table 4-4 breaks the instruction count down into categories representing the functions performed<sup>5</sup> and shows the number of memory accesses performed. The 18 memory accesses shown, however, explain only part of the cost. As it turns out (and only a run on the hardware simulator at nCUBE could confirm the details) a large fraction of the cycles is lost in pipeline bubbles in the instruc-

```

# AMsend: Active Message send system call interface

1: inline void AM_send(int dest_node, int length)

#

-> R0=dest_node, R1=length

2: {

3:

asm("trap #SEND");

4: }

# Active Message send system call

adjust destination for sub-cube origin

1: SEND: addw3 cubase, r0, r2

2:

limit destinations to machine size

andw

#cumask,r2

3:

send_buf,r3

buffer to be sent

movw

4:

r2,(r3)

store dest in message

movw

5:

xlate node to output port offset

mvub

out_port(r2),r2

6:

limit message length

andw

#lenmask,r1

get output DMA status register

7:

#outtrr,r4

stpr

8:

bitmsk(r2),r4

test for channel ready

bitw

9:

not ready: busy-wait

be

s1

10: s0:

load dma pointer

lptr

r3,out_reg(r2)

11:

load dma count

r1,out_reg(r2)

lcnt

out_buf(r2),send_buf set new user output buff

12:

movw

13:

segoff, send_buf, send_usrbuf xlate to virtual user addr

addw3

14:

set new channel buffer

movw

r3,out_buf(r2)

15: s4:

return to user

reti

# channel not ready, first test if send to self or send beyond sub-cube

compare node to local node id

nodeid,(r3)

1: s1:

cmph

send to self (not shown)

be

snd_self

3:

check for node beyond sub-sube

cusize,(r3)

cmph

4:

error, drop message

ble

s4

wait for previous message to go out

5:

enable vertex's output interrupts

ldpr

#mskin, #psw

get input DMA status reg.

6: s2:

stpr

#inrdy,r4

7:

just recv'd a msg? service it (not shown)

bne

snd_recv

8:

get output DMA status register

#outtrr,r4

stpr

9:

bitw

bitmsk(r2),r4

wait for prev msg to go out

10:

ready, send message

bne

```

Figure 4-7: Send system call implementation for nCUBE/2 Active Messages.

The Active Message send system call interface uses the calling convention to load the destination node and the message length into registers R0 and R1 and traps to the kernel. The typical path through the kernel is 15 instructions long and includes protection checks, DMA set-up, and buffer management. If the outgoing DMA channel is busy the kernel busy-waits and allows handlers for incoming messages to be dispatched.

prefetch pipeline. The reason is that these instructions are implemented in the prefetch unit. This prevents any prefetching from occurring during their execution, which takes almost a "dozen cycles". (The exact details remain company confidential, but do not provide further insights anyhow.) The interesting observation is that the hardware designers did not feel compelled to particularly optimize the network access instructions given that normally (i.e., in the send&receive implementation) they are

<sup>&</sup>lt;sup>5.</sup> It obviously would be more precise to break the costs down into cycles instead of instructions. Unfortunately the CISC nature of the instruction set and the lack of precise information on the operations of the micro-engines prevents precise accounting of clock cycles.

| Kernel variables and constants         |                                                             |  |  |  |  |  |

|----------------------------------------|-------------------------------------------------------------|--|--|--|--|--|

| cubase                                 | origin of sub-cube current program runs in                  |  |  |  |  |  |

| cumask                                 | cube mask: 2 <sup>(machine size)</sup> -1                   |  |  |  |  |  |

| culimit                                | number of nodes in the subcube                              |  |  |  |  |  |

| nodeid                                 | number of local node                                        |  |  |  |  |  |

| lenmask                                | mask to limit message length                                |  |  |  |  |  |

| segoff                                 | user data segment physical to virtual offset                |  |  |  |  |  |

| usrstk                                 | user stack base (where the PC/PSW is saved on kernel entry) |  |  |  |  |  |

| usrint                                 | PC and PSW of handler stub                                  |  |  |  |  |  |

| tstamp                                 | time stamp when interrupts disabled                         |  |  |  |  |  |

| send_buf                               | current user send buffer address                            |  |  |  |  |  |

| recv_buf                               | current user receive buffer address                         |  |  |  |  |  |

| out_port                               | table of output port number indexed by destination node     |  |  |  |  |  |

| bitmsk                                 | table of channel bit mask indexed by port number            |  |  |  |  |  |

| in_reg                                 | table of input DMA register offsets indexed by port number  |  |  |  |  |  |

| in_buf                                 | table of input DMA buffers indexed by port number           |  |  |  |  |  |

| out_reg                                | table of output DMA register offsets indexed by port number |  |  |  |  |  |

| out_buf                                | table of output DMA buffers indexed by port number          |  |  |  |  |  |

| User-kernel shared handshake variables |                                                             |  |  |  |  |  |

| send_usrbuf                            | current user send buffer user virtual address               |  |  |  |  |  |

| recv_usrbuf                            | current user receive buffer user virtual address            |  |  |  |  |  |

| flags                                  | handshake flags                                             |  |  |  |  |  |

| usrret                                 | PC and PSW of computation interrupted by handler            |  |  |  |  |  |

Table 4-3. Kernel variables for nCUBE/2 Active Messages implementation.

| Instruction category     | instructions | memory<br>accesses |

|--------------------------|--------------|--------------------|

| kernel trap              | 2            | 6                  |

| check destination+length | 4            | 2                  |

| determine output port    | 1            | 4                  |

| check port ready         | 3            | 0                  |

| set-up DMA               | 2            | 0                  |

| buffer management        | 4            | 6                  |

| total                    | 16           | 18                 |

Table 4-4. Instruction breakdown by category for nCUBE/2 Active Message send.

```

# Input DMA interrupt handler (for channel 0)

push user reg onto stack

1: intr0: movd

r15,stk

load DMA buffer pointer

movw

in_buf+0*16,r15

3:

xorb

flags, 3(r15)

4:

test msg type and handshake flags

cmpb

#0x40,3(r15)

5:

bne

bsy0

user busy or vertex message

6:

7:

set new DMA input buffer

recv_buf,#0

lptr

start DMA (count is ignored)

lcnt

#0,#0

8:

orb

#inHandler,flags

set inHandler bit

9:

recv_buf,in_buf+0*16 swap buffers

movw

10:

r15,recv_buf

movw

11:

addw3

segoff, r15, recv_usrbuf set user's pointer

12:

where to find user's PC

movw

usrstk,r15

13:

save user's interrupted PC and PSW

(r15),usrret

movd

set user's int. handler PC and PSW

14:

movd

usrint,(r15)

15:

restore user reg

stk,r15

movd

16:

return to user to handler

reti

17: bsy0:

user busy or vertex message

vertex message (code not shown)

18:

vtx0

bg

19:

flags, 3(r15)

unfizzzz

xorb

20:

disable input ints

#0x80000000, #inen

ldpr

21:

#timlo,tstamp

take time-stamp

stpr

22:

set msgPending flag

orb

#msgPending,flags

23:

movd

stk,r15

restore user reg

24:

return to user

reti

```

Figure 4-8: Input DMA interrupt handler for nCUBE/2 Active Messages.

hidden among 100's of instructions and do not contribute a significant fraction of the communication overhead.

Besides highlighting the need to optimize the DMA instructions, the instruction category breakdown in Table 4-4 shows that a few simple additional hardware features could cut down the communication overhead dramatically. The checks on the destination node address and on the message length could be performed in hardware easily. The selection of the correct output port could be simplified or eliminated altogether by multiplexing the DMA engines onto a single set of interface registers. Given the small volume of the network, it is actually not clear whether multiple DMA engines are of great benefit. Reducing the buffer management further is somewhat difficult without eliminating the DMA altogether. For small messages, such as the ones used in the fetch&add example, this may well be worthwhile.

#### Message reception

The reception of Active Messages occurs in two phases: first the kernel interrupt handler switches buffers, re-initializes the DMA for the next message, and starts a user-level stub which, in a second phase, dispatches the Active Message handler proper, checks for additional messages, and finally returns to the computation.

Figure 4-7 shows the path through the kernel interrupt handler. The code is straightforward with two exceptions:

• An otherwise uninterpreted bit of the destination node address word is used to flag Vertex messages allowing Active Messages to coexist with Vertex's send&receive. The only conditional (lines 3-5) combines this "vertex bit" with the user-kernel handshake flags (the bit encod-

| instruction entogony               | instr  | uctions   | memory accesses |           |  |

|------------------------------------|--------|-----------|-----------------|-----------|--|

| instruction category               | kernel | user stub | kernel          | user stub |  |

| interrupt                          | 2      | _         | 7               | _         |  |

| check for Vertex message           | 1      | _         | 1               | _         |  |

| buffer management                  | 4      | _         | 6               | _         |  |

| restart DMA                        | 2      | _         | 1               | _         |  |

| start user-level interrupt handler | 3      | _         | 5               | _         |  |

| handler atomicity handshake        | 3      | 2         | 4               | 2         |  |

| dispatch Active Message handler    | _      | 3         | _               | 3         |  |

| return to computation              | _      | 7         | _               | 6         |  |

| save registers                     | 2      | 6         | 2               | 6         |  |

| total                              | 17     | 18        | 26              | 17        |  |

Table 4-5. Instruction breakdown for nCUBE/2 Active Message reception

ings were chosen to allow this) and simultaneously checks both with a single compare and branch.

• In order to start the user-level stub the interrupt handler substitutes the PC and PSW of the stub for those of the interrupted computation. A precomputed pointer points to the base of the kernel stack to allow the quick location of the saved PC and PSW.

The user-level stub is shown in Figure 4-9. Besides saving a few registers and dispatching to the actual Active Message handler, the stub implements the user-kernel handshake and simulates a reti (return from interrupt) instruction to return to the interrupted computation. The difficulty in returning to the computation lies in restoring the PSW. The condition codes in the PSW must be shifted before being set with a load condition codes instruction (ldflg), there is no direct way to restore the IEEE rounding mode, and, worst of all, the repeat mode (used to emulate vector instructions) cannot be restored. The solution adopted in the implementation is to check the PSW for the default setting of the rounding and repeat mode bits and to break out to a special restore sequence which traps to the kernel to execute a real reti if necessary.

Note that in order to perform the user-kernel handshake the stub must atomically clear the inHandler flag and check the msgPending flag. Thanks to the powerful CISC instruction set and to an appropriate bit encoding this is possible with a single and instruction (line 13) which clears the flag and compares the resulting byte against zero.

Table 4-5 shows the breakdown of instructions into categories by the function performed. Again, the interrupt is expensive in terms of memory accesses and the DMA instructions take many cycles each. However, the numbers also show that the Active Messages dispatch does not come for free. Passing the interrupt through to user-level is not cheap and the second dispatch to the Active Message handler adds to it. The difficulty of returning to the interrupted computation is also out of proportion. If restoring the PSW were simple it could be incorporated directly into the Active Message handler together with the user-kernel handshake, eliminating the stub as such altogether. The kernel could then dispatch the Active Message handler directly saving a significant number of cycles.

#### **Summary**

The instruction sequences implementing Active Messages are very short. A major part of the execution cost stems from the privilege level crossings and from the DMA instructions which any message layer must include. Only a few instructions could hypothetically be eliminated by another message layer and would not affect performance dramatically. The precise cost breakdown possible due to the simplicity

```

# User-Kernel handshake variables, in user space

1: outbuf .equ

0x80000000

output buffer pointer

\it 2: inbuf \it .equ

uoutbuf+8

input buffer pointer

save area for interrupted PC

3: iret

.equ

uoutbuf+12

save area for interrupted PSW

4: ipsw

.equ

uoutbuf+16

user-kernel handshåke flags

5: flags .equ

uoutbuf+20

# Bits in uflags

6: inHandler

in handler

.equ 1

additional message(s) pending

7: msgPending .equ 2

8: up_crit.equ 4

in critical section

# Active Messages handler stub

1:_AM_hstub:

2:

movw

iret, stk

push the interrupted PC

3:

movd

r0,stk

save caller-saves registers

4:

movd

r1,stk

5:

r2,stk

movd

6:

movd

r3,stk

7:

movd

r4,stk

8:

movd

r5,stk

9:

push int. PSW, ready for restore

rotw3 #2,ipsw,stk

get input buffer address

10:

movw

inbuf,r0

get Active Messages handler addr

11:

(r0), r1

movw

12:

dispatch to handler

call

(r1)

13:

clr up_hand&up_crit, check up_pend

andb

#~inHandler,flags

14:

stub_more

oops, another message is pending

bne

pop interrupted PSW

15:

movw

stk,r0

16:

#0x0c000003,r0

test if rounding control or repeat mode bits set

bitw

yes, play tricks (not shown)

17:

bne

stub_special

18:

restore PSW: load CC and RC=0

ldflg r0

restore saved user registers

19:

movd

stk,r5

20:

stk,r4

movd

21:

movd

stk,r3

22:

movd

stk,r2

23:

stk,r1

movd

24:

movd

stk,r0

25:

return to interrupted computation

ret

# More messages arrived while servicing this one

26: stub_more:

27:

set up_hand flag again

orb

#inHandler,flags

28:

trap

#RECV

trap to get next message

29:

got one?

bitb

#msgPending,flags

30:

be

stub_m2

nope

got one: ... handler dispatch code similar to above elided...

#

31: stub_m2:

none: return to user code similar to above elided...

32: stub_special:

play special tricks to deal with repeat-mode and rounding-mode

```

Figure 4-9: User-level interface to interrupt handler in nCUBE/2 Active Messages.

of the implementation suggests a number of evolutionary hardware changes that could further reduce the overhead dramatically.

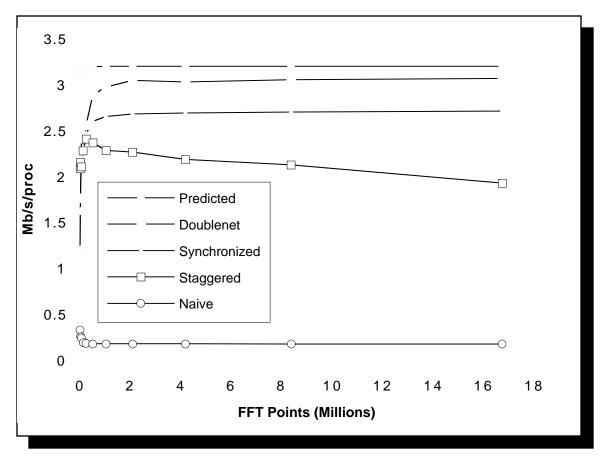

# 4.2.6 Macro-benchmarks

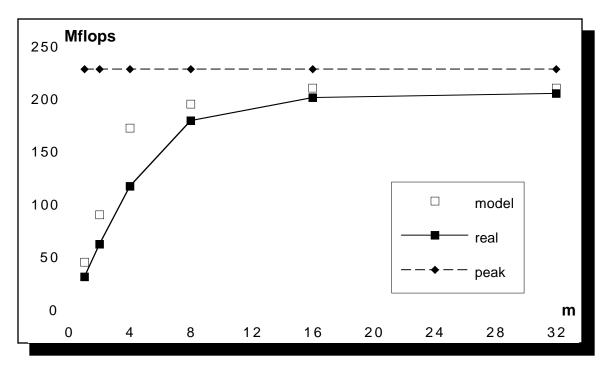

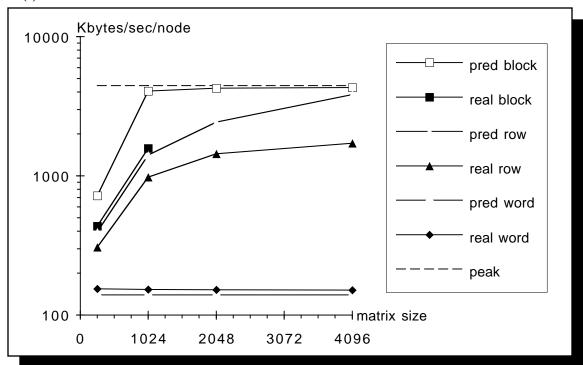

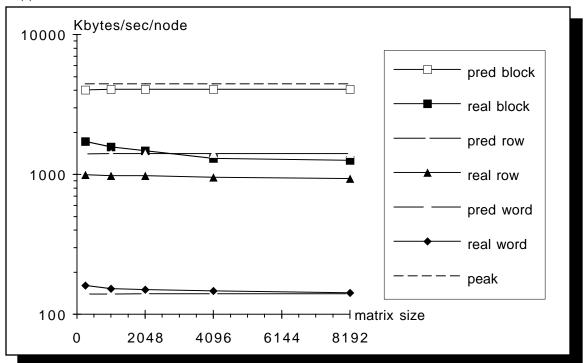

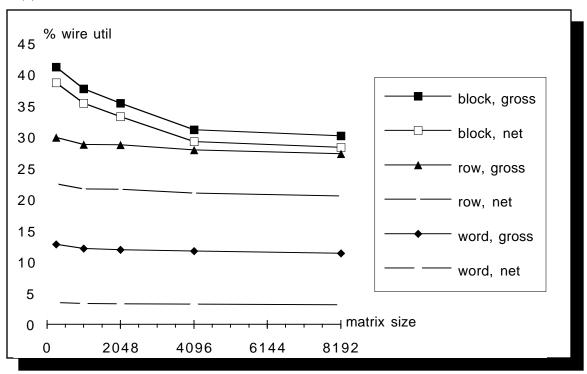

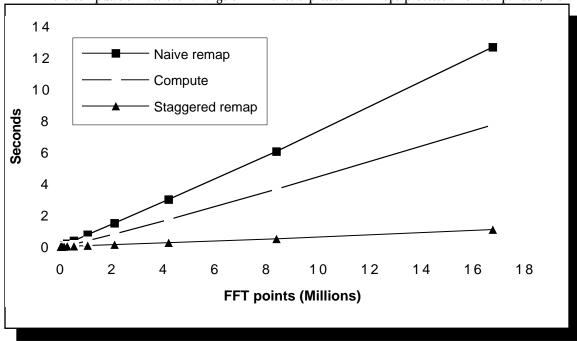

The micro-benchmarks have shown that Active Messages are capable of high peak performance. But does this performance level carry through to real programs? The following two simple benchmarks suggest that meaningful higher-level communication abstractions can be layered on top of Active Messages without compromising performance.

# 4.2.6.1 Matrix multiply

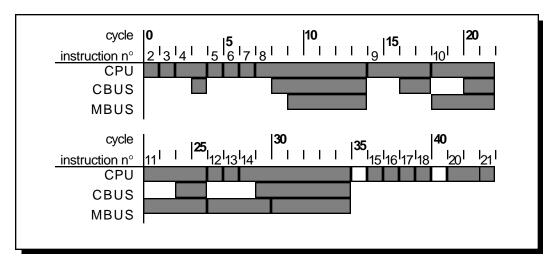

The first benchmark implements a simple version of matrix multiply using split-phase remote memory fetches. The benchmark shows that it is possible to obtain close to peak performance using the small Active Messages. The design decision to concentrate on small messages in order to provide the lowest possible overhead is shown to pay off.

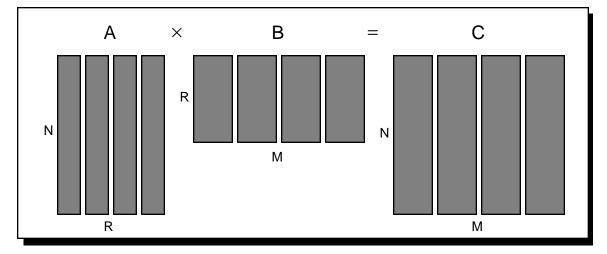

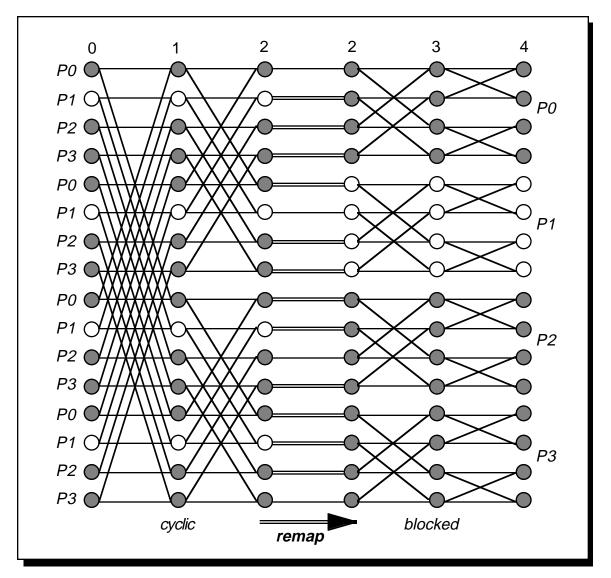

The benchmark program multiplies two 64-bit floating-point matrices stored as blocks of columns per processor as shown in Figure 4-10. For NxR and RxM input matrices A and B spread across P processors, each processor starts with R/P and M/P columns and ends up with M/P columns of C (the benchmark code assumes that M and R are multiples of P).

# Algorithm

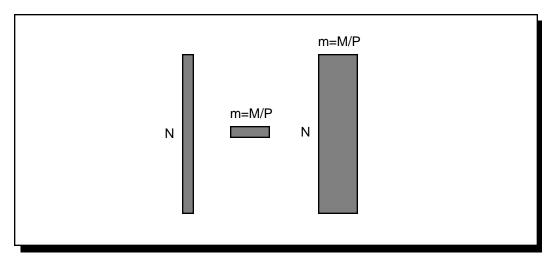

In the inner loop shown in Figure 4-11, each processor fetches one, typically remote, column of A and multiplies it (outer product) by a local sub-row of B, summing the result into the local part of C. The program is derived from a simple uniprocessor version using an outer product formulation:

```

1: for k = 0 to R-1 do

2: for j = 0 to M-1 do

3: for i = 0 to N-1 do

4: C[i,j] = C[i,j] + A[i,k] + B[k,j]

```

An efficient method to access the remote values of A is to fetch a column of A in one block before operating on it. The following matrix multiply sample code uses a get to fetch remote memory. The se-

Figure 4-10: Matrices layout in blocks of columns for matrix multiply.

Figure 4-11: Matrix multiply inner loop.

mantics of get are described in detail as part of the Split-C language in Section 6.1. In summary, get fetches a remote memory block described by memory address and length. It is split-phase in that it only initiates a request Active Message and immediately returns. The handler for the reply stores the data in memory and increments a flag which can be used by the computation to determine that the get has completed.

The straight-forward multiprocessor version shown below is adapted from the uniprocessor code. It initiates the fetch for a column of A and immediately busy-waits for it to complete. In addition, the iteration order of the outer loop is shifted such that processor i-starts with its columns of A, the fetches from processor i-1, and so forth. This staggering of the communication pattern avoids that processors 1 through P-1 start by requesting a column from processor 0 which would create a hot-spot.

```

1: for dk = 0 to R-1 do

2: k = (k0+dk) % R

3: get(k/P, A[*,k%P], V, flag); get column into temp vector V

4: wait(flag, 1); wait for column to arrive

5: for j = 0 to M/P-1 do

6: for i = 0 to N-1 do

7: C[i,j] = C[i,j] + V[i] + B[k,j]

8:

```

This simple version can be optimized by taking advantage of the split-phase nature of get to pipeline the remote fetches. The final version uses two temporary vectors and prefetches the column used in the next iteration. This prefetching permits the processor to continue computing while communication oc-