## Lab 5 Worksheet

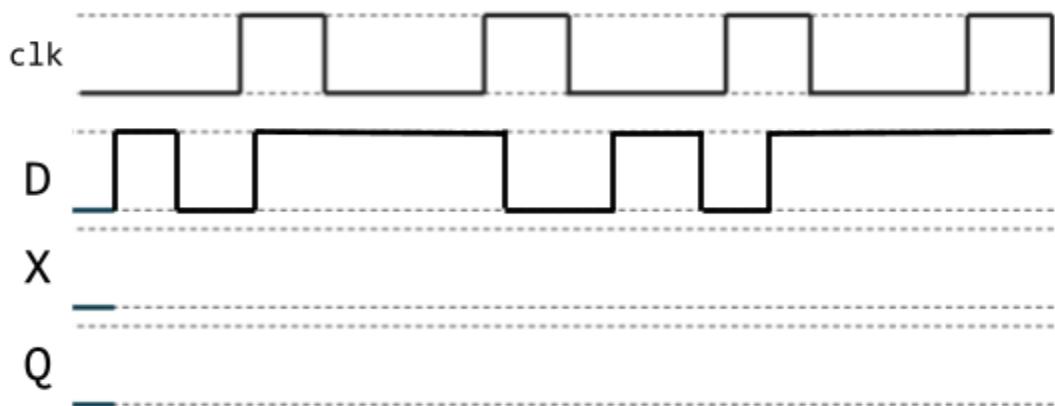

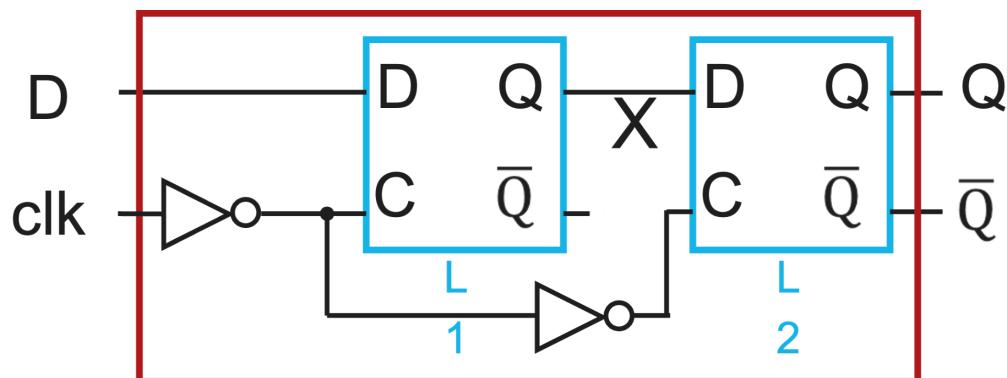

## 1. D Flip-Flop Waveform

Complete the following waveform diagram for a positive edge triggered D flip-flop.

## 2. CPU Stages

a. Fill in the table below based on your knowledge of instructions and CPU stages (add has been done for you as an example)

|           | add | xori | sra | beq | sw | ld |

|-----------|-----|------|-----|-----|----|----|

| FETCH     | ✓   |      |     |     |    |    |

| DECODE    | ✓   |      |     |     |    |    |

| EXECUTE   | ✓   |      |     |     |    |    |

| MEMORY    |     |      |     |     |    |    |

| WRITEBACK | ✓   |      |     |     |    |    |

b. Fill in the table below specifying which stage does the CPU read/write (**Memory** has been done for you as an example)

|           | READ FROM REGISTER | WRITE TO REGISTER | READ FROM MEMORY | WRITE TO MEMORY | NONE |

|-----------|--------------------|-------------------|------------------|-----------------|------|

| FETCH     |                    |                   |                  |                 |      |

| DECODE    |                    |                   |                  |                 |      |

| EXECUTE   |                    |                   |                  |                 |      |

| MEMORY    |                    |                   | ✓                | ✓               |      |

| WRITEBACK |                    |                   |                  |                 |      |

### 3. Decoding and Encoding

a. Given these binary strings, decode them into RISC-V assembly

000001000000 | 00100 | 000 | 00011 | 0010011

00000000 | 00111 | 00000 | 010 | 00100 | 0100011

b. Given these lines of RISC-V assembly code, encode them into binary strings.

lui x5, 24

beq x8, x9, -16