#### State

# Prof. Hakim Weatherspoon CS 3410

Computer Science Cornell University

[Weatherspoon, Bala, Bracy, and Sirer]

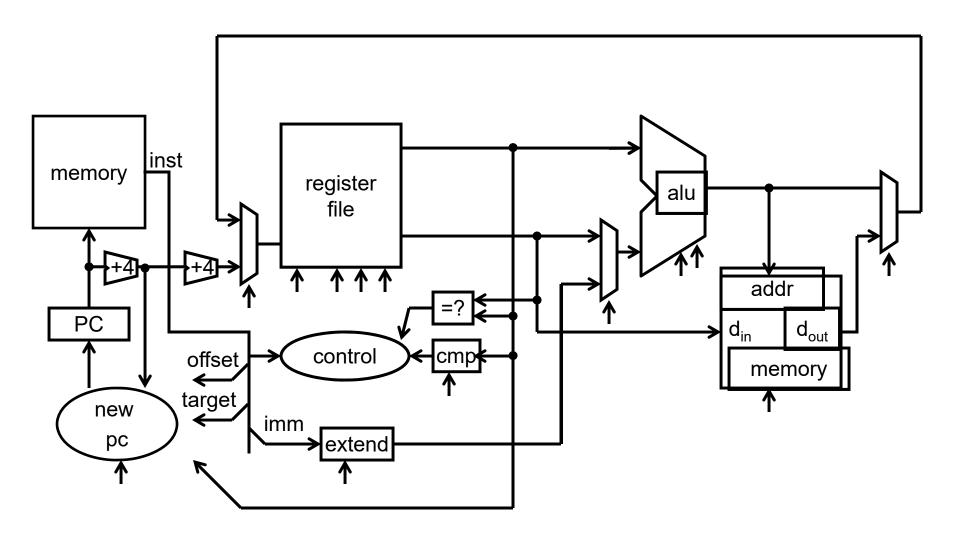

# Big Picture: Building a Processor

A single cycle processor

#### Review

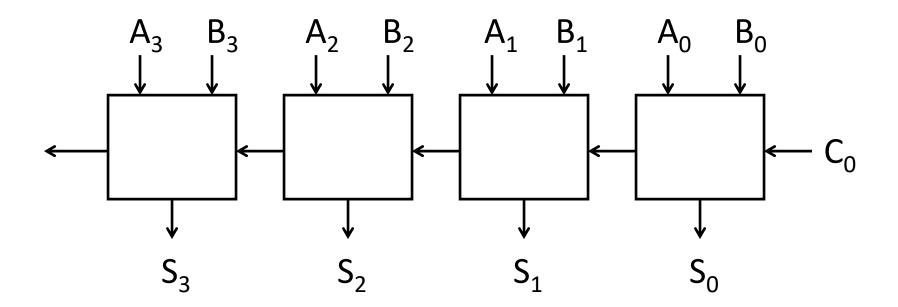

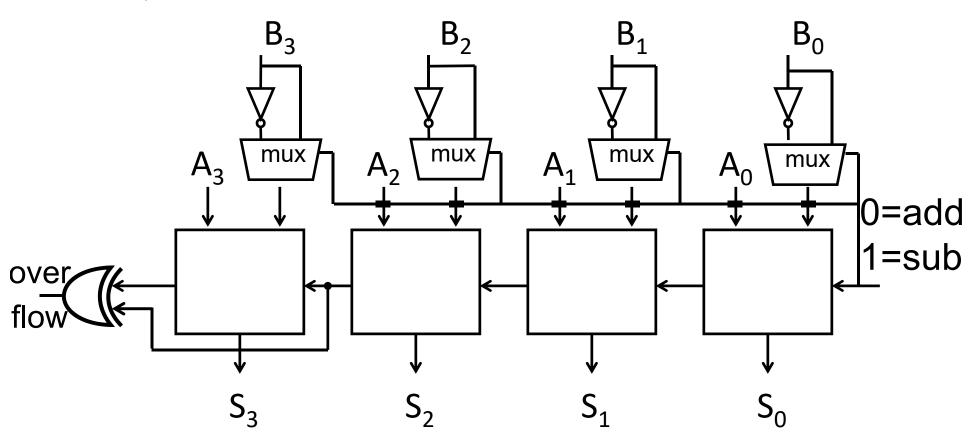

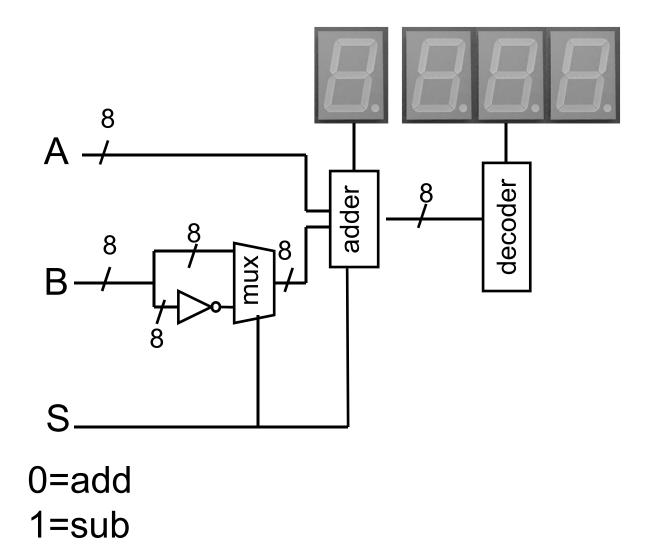

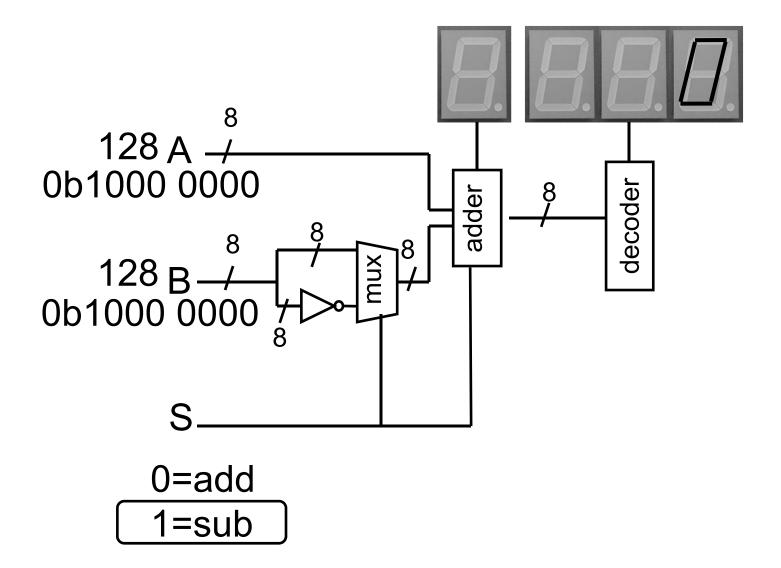

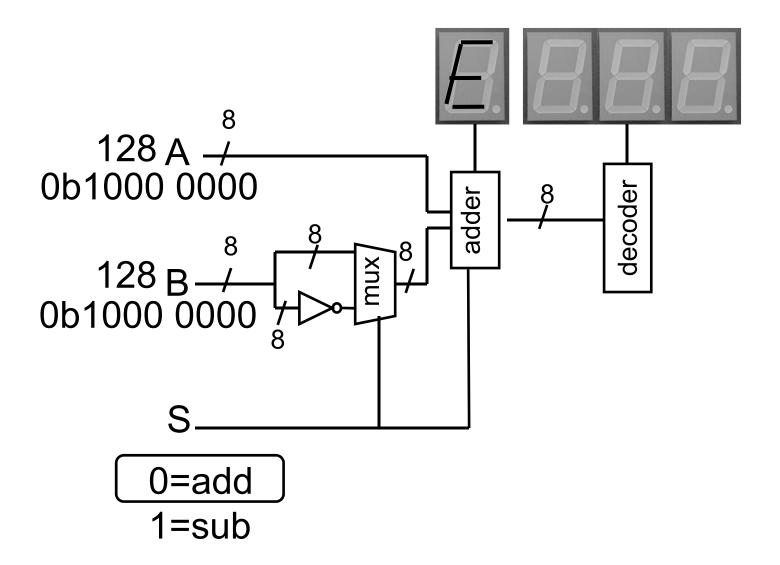

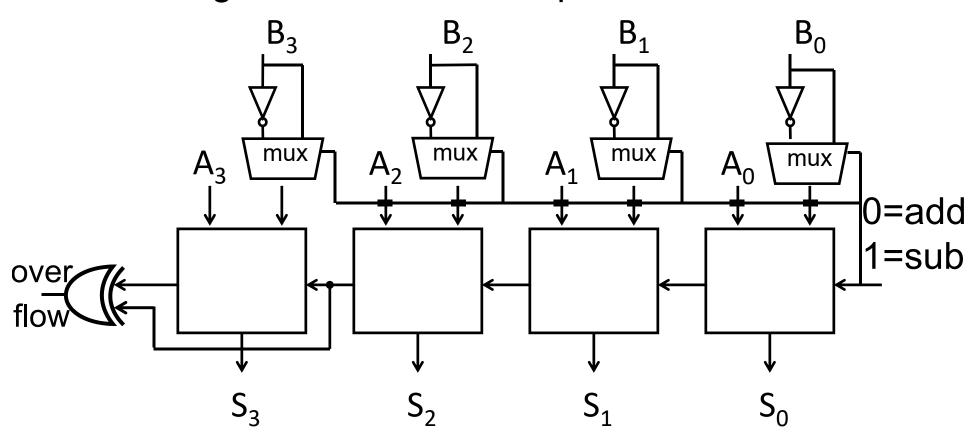

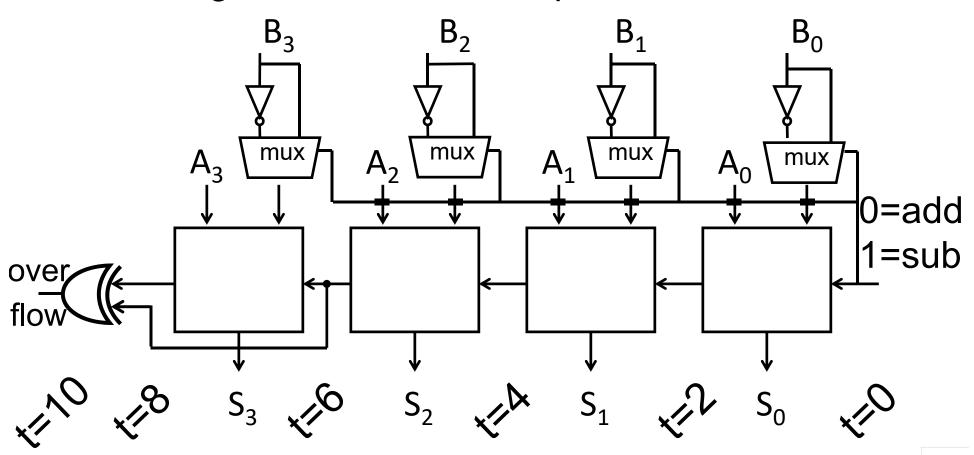

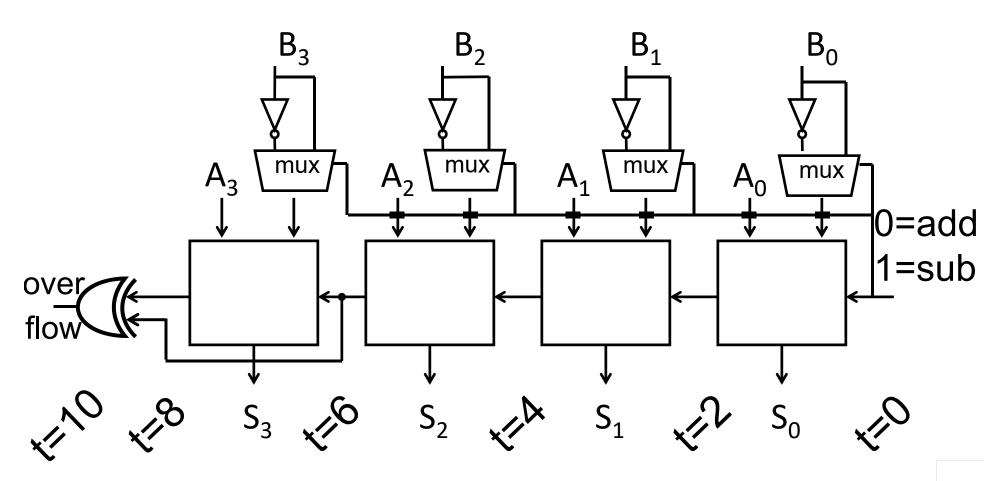

• We can generalize 1-bit Full Adders to 32 bits, 64 bits ...

#### Review

We can generalize 1-bit Full Adders to 32 bits, 64 bits ...

S\_\_\_\_

0=add

1=sub

We can generalize 1-bit Full Adders to 32 bits, 64 bits

How long does it take to compute a result?

- We can generalize 1-bit Full Adders to 32 bits, 64 bits

- How long does it take to compute a result?

- A) 2 ns

- B) 2 gate delays

- C) 10 ns

- D) 10 gate delays

- E) 8 gate delays

We can generalize 1-bit Full Adders to 32 bits, 64 bits

How long does it take to compute a result?

- We can generalize 1-bit Full Adders to 32 bits, 64 bits ...

- How long does it take to compute a result?

- Can we store the result?

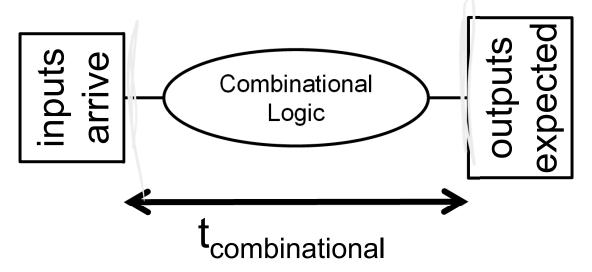

#### Performance

Speed of a circuit is affected by the number of gates in series (on the *critical path* or the *deepest level of logic*)

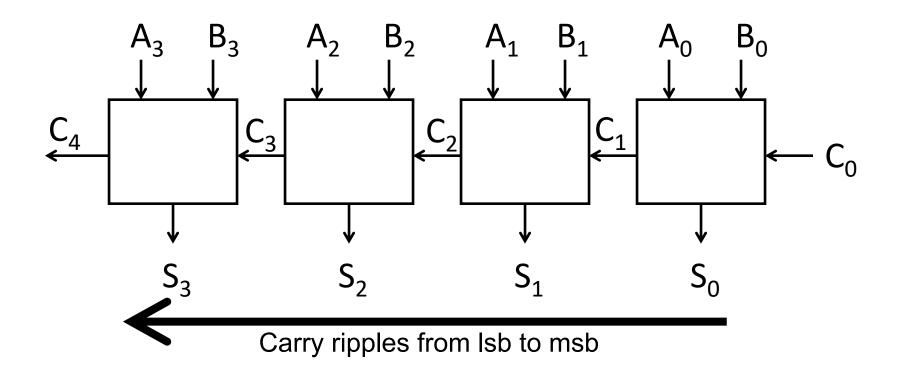

## 4-bit Ripple Carry Adder

- First full adder, 2 gate delay

- Second full adder, 2 gate delay

•

#### Stateful Components

Until now is combinationial logic

- Output is computed when inputs are present

- System has no internal state

- Nothing computed in the present can depend on what happened in the past!

Need a way to record data Need a way to build stateful circuits Need a state-holding device

#### Goals for Today State

- How do we store one bit?

- Attempts at storing (and changing) one bit

- Set-Reset Latch

- D Latch

- D Flip-Flops

- Master-Slave Flip-Flops

- Register: storing more than one bit, N-bits

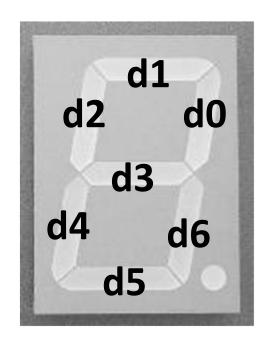

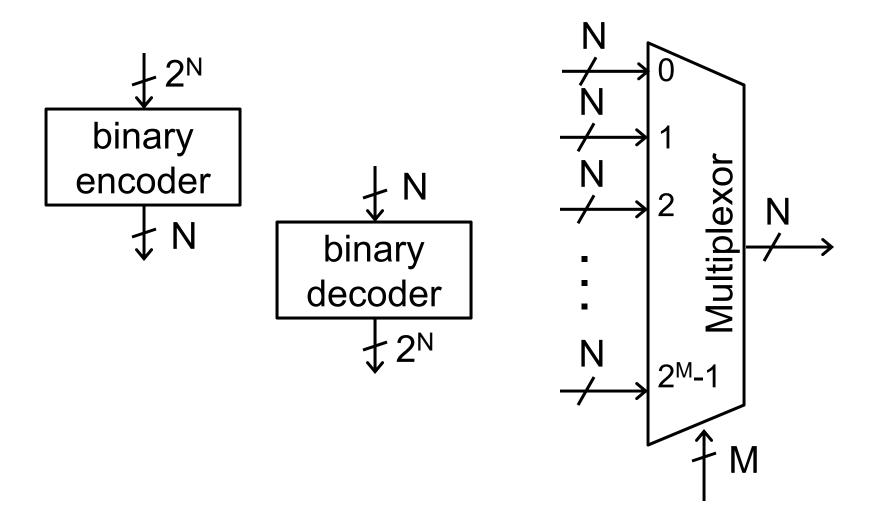

#### **Basic Building Blocks**

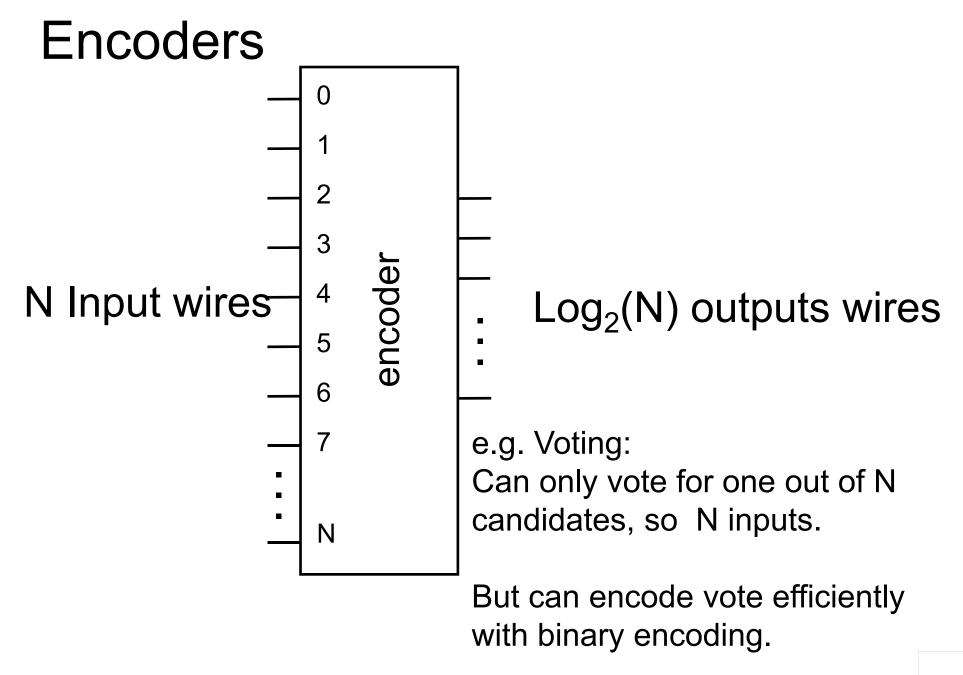

Decoders and Encoders

#### Goal

How do we store store one bit?

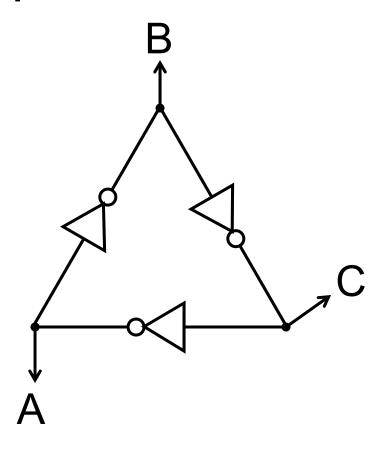

## First Attempt: Unstable Devices

## First Attempt: Unstable Devices

Does not work!

- Unstable

- Oscillates wildly!

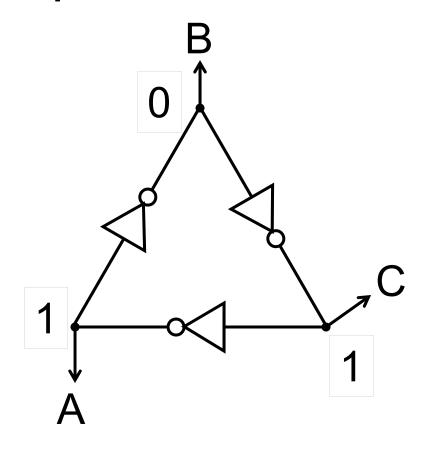

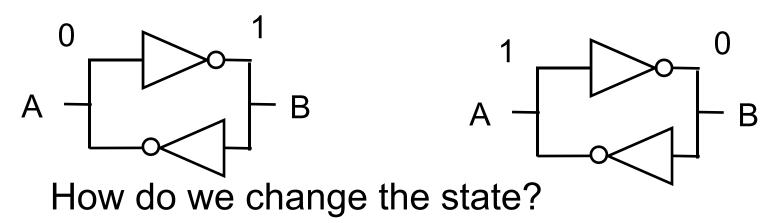

#### Second Attempt: Bistable Devices

Stable and unstable equilibria?

In stable state, A = B

| A | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| \$ <sub>S</sub> | $R_{R}$ | <b>Q</b> | $\overline{\mathbb{Q}}_{\overline{\mathbb{Q}}}$ |

|-----------------|---------|----------|-------------------------------------------------|

| 00              | 00      |          |                                                 |

| 00              | 11      |          |                                                 |

| 11              | 00      |          |                                                 |

| 11              | 11      |          |                                                 |

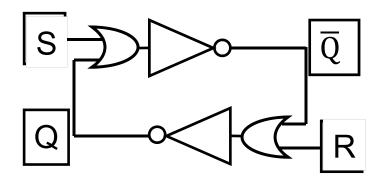

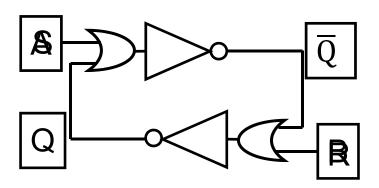

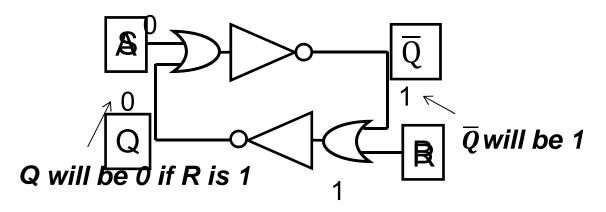

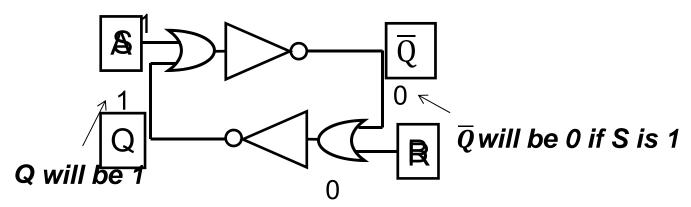

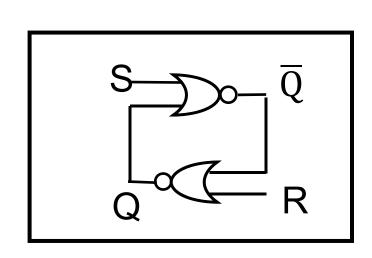

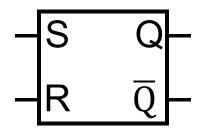

Set-Reset (S-R) Latch

Stores a value Q and its complement

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| 9 | S |   | R              | Q | <u> </u> | φ |  |

|---|---|---|----------------|---|----------|---|--|

|   | 0 |   | 0              |   |          |   |  |

|   | 0 |   | <sup>L</sup> 1 | C | )        | 1 |  |

|   | 1 |   | 0              |   |          |   |  |

|   | 1 | - | <sup>1</sup> 1 |   |          |   |  |

| + |   |   |                |   |          |   |  |

Set-Reset (S-R) Latch

Stores a value Q and its complement

Set-Reset (S-R) Latch Stores a value Q and its complement

|   | Α | В | OR | NOR |

|---|---|---|----|-----|

|   | 0 | 0 | 0  | 1   |

|   | 0 | 1 | 1  | 0   |

| • | 1 | 0 | 1  | 0   |

|   | 1 | 1 | 1  | 0   |

| S | R | Q | $\overline{\mathbb{Q}}$ |

|---|---|---|-------------------------|

| 0 | 0 |   |                         |

| 0 | 1 | 0 | 1                       |

| 1 | 0 | 1 | 0                       |

| 1 | 1 |   |                         |

What are the values for Q and  $\overline{Q}$ ?

- a) 0 and 0

- b) <u>0 and 1</u>

- c) 1 and 0

- d) 1 and 7

iClicker Question

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | ~ | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| S | R | Q | $\overline{\mathbf{Q}}$ |

|---|---|---|-------------------------|

| 0 | 0 | Q | $\overline{\mathbb{Q}}$ |

| 0 | 1 | 0 | 1                       |

| 1 | 0 | 1 | 0                       |

| 1 | 1 |   |                         |

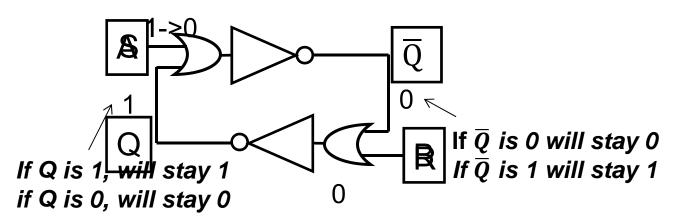

Set-Reset (S-R) Latch

Stores a value Q and its complement

| A | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| S | R | Q | $\overline{\mathbf{Q}}$ |

|---|---|---|-------------------------|

| 0 | 0 | Q | $\overline{\mathbf{Q}}$ |

| 0 | 1 | 0 | 1                       |

| 1 | 0 | 1 | 0                       |

| 1 | 1 | ? | ?                       |

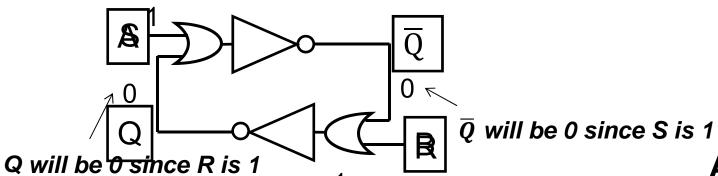

Set-Reset (S-R) Latch

Stores a value Q and its complement

What happens when S,R changes from 1,1 to 0,0?

#### iClicker Question

What's wrong with the SR Latch?

- A. Q is undefined when S=1 and R=1 (That's why this is called the forbidden state.)

- B. Q oscillates between 0 and 1 when the inputs transition from 1,1 → 0,0

- C. The SR Latch is problematic b/c it has two outputs to store a single bit.

- D. There is nothing wrong with the SR Latch!

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | ~ | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| S | R | Q     | $\overline{\overline{Q}}$ |

|---|---|-------|---------------------------|

| 0 | 0 | Q     | $\overline{\mathbb{Q}}$   |

| 0 | 1 | 0     | 1                         |

| 1 | 0 | 1     | 0                         |

| 1 | 1 | forbi | dden                      |

Set-Reset (S-R) Latch 1 1 1 1 Stores a value Q and its complement

What happens when S,R changes from 1,1 to 0,0?

Q and  $\overline{Q}$  become unstable and will oscillate wildly between values 0,0 to 1,1 to 0,0 to 1,1 ...

| S | R | Q         | $\overline{\mathbf{Q}}$ |       |

|---|---|-----------|-------------------------|-------|

| 0 | 0 | Q         | $\overline{\mathbf{Q}}$ | hold  |

| 0 | 1 | 0         | 1                       | reset |

| 1 | 0 | 1         | 0                       | set   |

| 1 | 1 | forbidden |                         |       |

Set-Reset (S-R) Latch Stores a value Q and its complement

## Takeaway

Set-Reset (SR) Latch can store one bit and we can change the value of the stored bit. But, SR Latch has a forbidden state.

#### **Next Goal**

How do we avoid the forbidden state of S-R Latch?

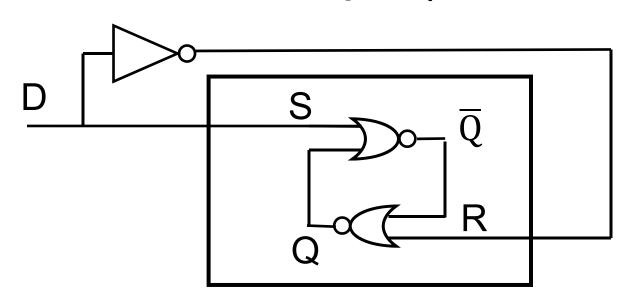

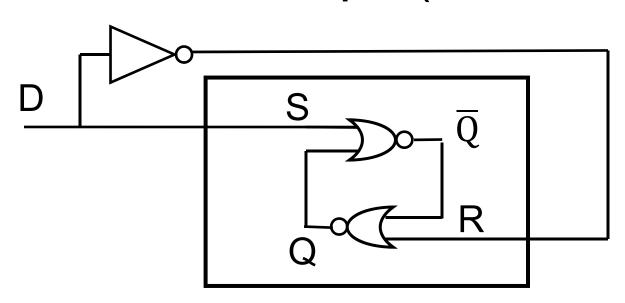

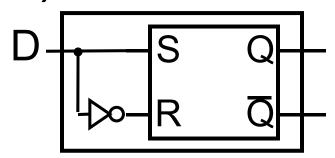

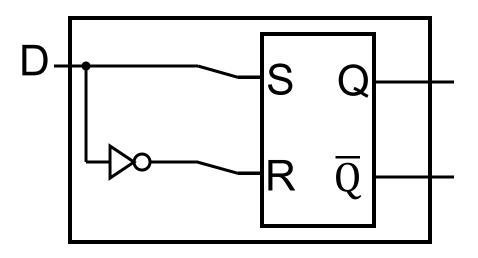

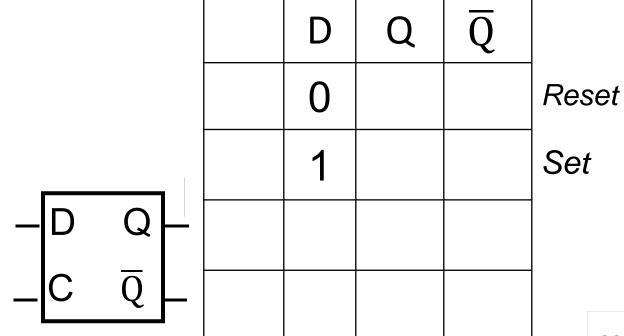

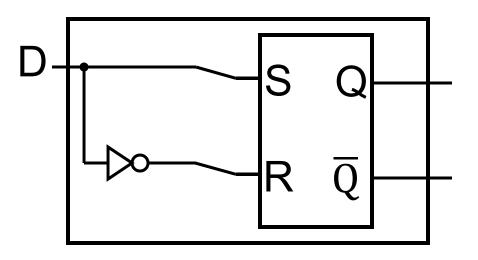

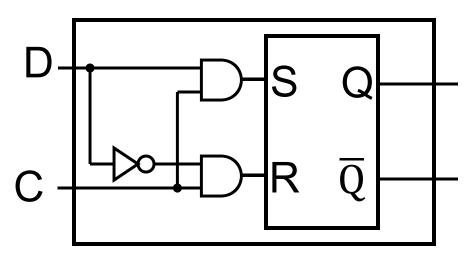

## Fourth Attempt: (Unclocked) D Latch

Fill in the truth table?

| D | Q | $\overline{\mathbf{Q}}$ |

|---|---|-------------------------|

| 0 |   |                         |

| 1 |   |                         |

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

## Fourth Attempt: (Unclocked) D Latch

0 0 1

Fill in the truth table?

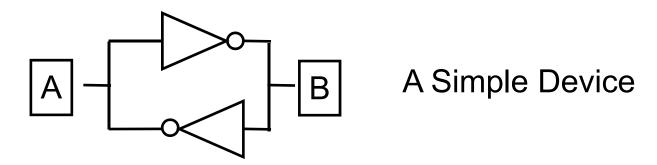

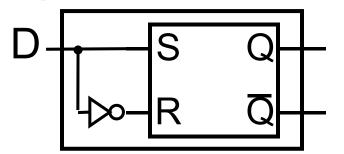

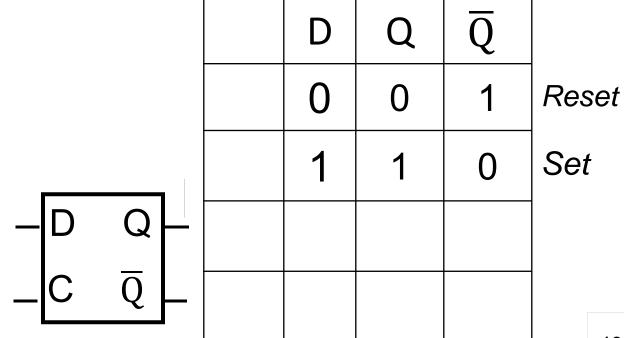

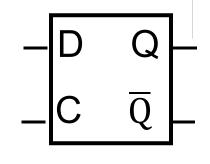

#### Data (D) Latch

- Easier to use than an SR latch

- No possibility of entering an undefined state

#### When D changes, Q changes

- ... immediately (...after a delay of 2 Ors and 2 NOTs)

Need to control when the output changes

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

#### Takeaway

Set-Reset (SR) Latch can store one bit and we can change the value of the stored bit. But, SR Latch has a forbidden state.

(Unclocked) D Latch can store and change a bit like an SR Latch while avoiding the forbidden state.

#### **Next Goal**

How do we coordinate state changes to a D Latch?

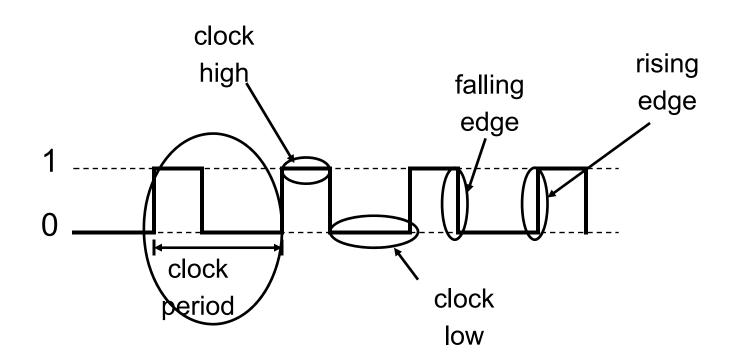

#### Aside: Clocks

#### Clock helps coordinate state changes

- Usually generated by an oscillating crystal

- Fixed period

- Frequency = 1/period

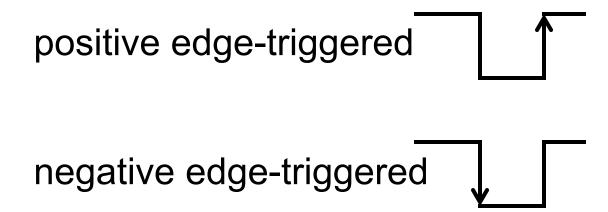

### Clock Disciplines

#### Level sensitive

State changes when clock is high (or low)

#### Edge triggered

State changes at clock edge

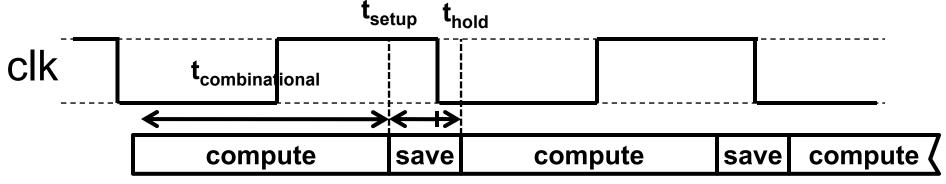

### Clock Methodology

#### Clock Methodology

Negative edge, synchronous

Edge-Triggered → signals must be stable near falling edge

"near" = before and after

$$t_{setup}$$

$t_{hold}$

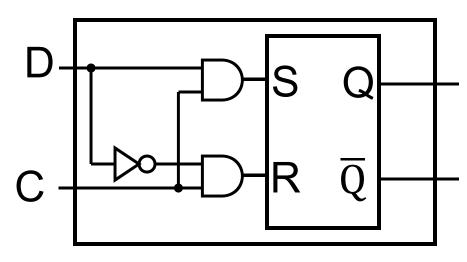

Inverter prevents SR Latch from entering 1,1 state

Inverter prevents SR Latch from entering 1,1 state

- Level sensitive

- Inverter prevents SR Latch from entering 1,1 state

- C enables changes

keep state (ignore D)

| С | D | Q | $\overline{\mathbf{Q}}$ |              |

|---|---|---|-------------------------|--------------|

| 0 | 0 |   |                         | No           |

| 0 | 1 |   |                         | No<br>Change |

| 1 | 0 |   |                         | Reset        |

| 1 | 1 |   |                         | Set          |

- Level sensitive

- Inverter prevents SR Latch from entering 1,1 state

- C enables changes

C = 1, D Latch *transparent*: set/reset (according to D)

C = 0, D Latch *opaque*:

keep state (ignore D)

| S | R | Q         | $\overline{\mathbf{Q}}$ | , ,   |  |  |

|---|---|-----------|-------------------------|-------|--|--|

| 0 | 0 | Q         | $\overline{\mathbb{Q}}$ | hold  |  |  |

| 0 | 1 | 0         | 1                       | reset |  |  |

| 1 | 0 | 1         | 0                       | set   |  |  |

| 1 | 1 | forbidden |                         |       |  |  |

| С | D | Q | $\overline{\mathbf{Q}}$ |              |

|---|---|---|-------------------------|--------------|

| 0 | 0 | Q | $\overline{\mathbf{Q}}$ | No           |

| 0 | 1 | Q | $\overline{\mathbf{Q}}$ | No<br>Change |

| 1 | 0 | 0 | 1                       | Reset        |

| 1 | 1 | 1 | 0                       | Set 42       |

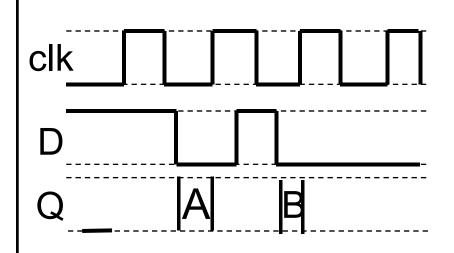

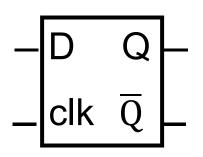

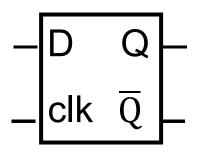

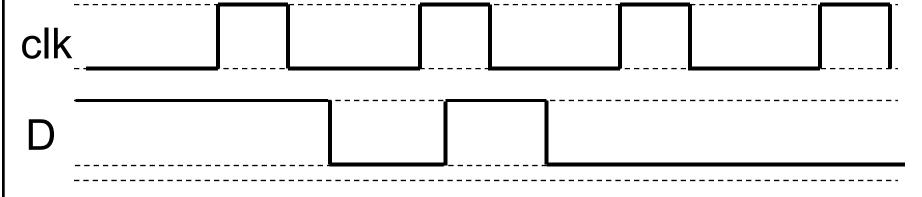

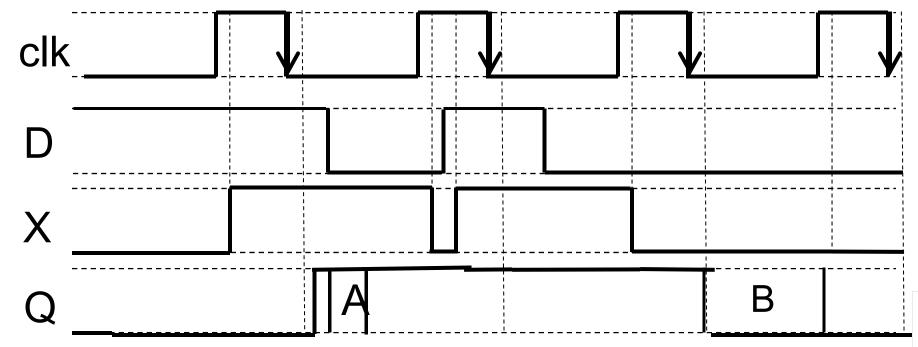

#### iClicker Question

What is the value of Q at A & B?

- a) A = 0, B = 0

- b) A = 0, B = 1

- c) A = 1, B = 0

- d) A = 1, B = 1

| clk | D | Q | $\overline{\mathbf{Q}}$ |

|-----|---|---|-------------------------|

| 0   | 0 | Q | $\overline{\mathbf{Q}}$ |

| 0   | 1 | Q | $\overline{\mathbf{Q}}$ |

| 1   | 0 | 0 | 1                       |

| 1   | 1 | 1 | 0                       |

#### iClicker Question

What is the value of Q at A & B?

- a) A = 0, B = 0

- b) A = 0, B = 1

- c) A = 1, B = 0

- (d) A = 1, B = 1

| clk | D | Q | $\overline{\mathbf{Q}}$ |

|-----|---|---|-------------------------|

| 0   | 0 | Q | $\overline{\mathbf{Q}}$ |

| 0   | 1 | Q | $\overline{\mathbf{Q}}$ |

| 1   | 0 | 0 | 1                       |

| 1   | 1 | 1 | 0                       |

### iClicker Question

Level Sensitive D Latch

Clock high:

set/reset (according to D)

Clock low:

keep state (ignore D)

| clk | D | Q | $\overline{\mathbf{Q}}$ |

|-----|---|---|-------------------------|

| 0   | 0 | Q | $\overline{\mathbf{Q}}$ |

| 0   | 1 | Q | $\overline{\mathbf{Q}}$ |

| 1   | 0 | 0 | 1                       |

| 1   | 1 | 1 | 0                       |

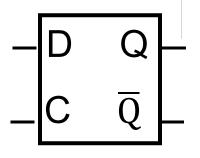

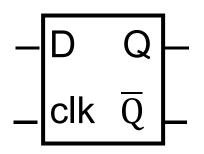

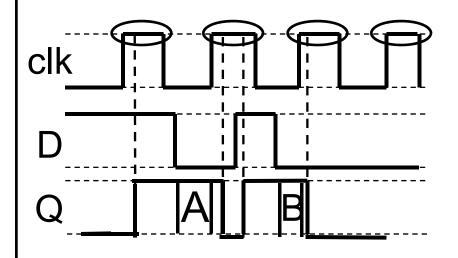

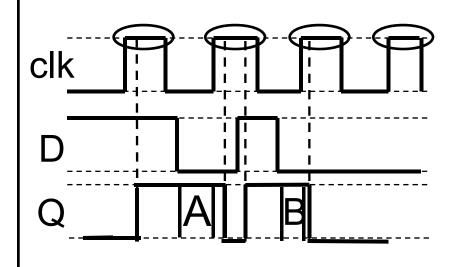

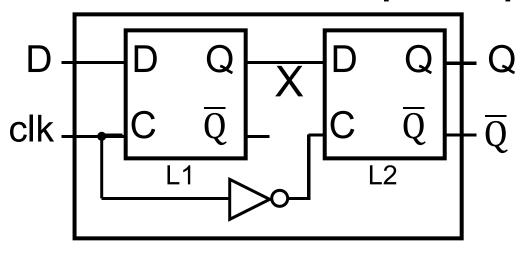

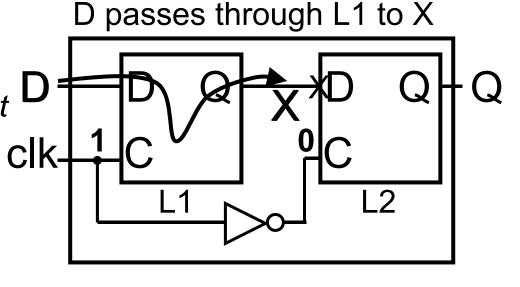

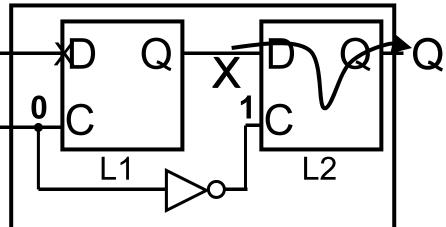

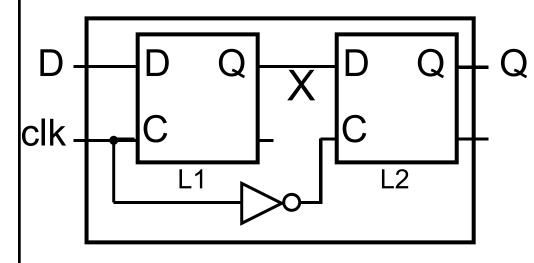

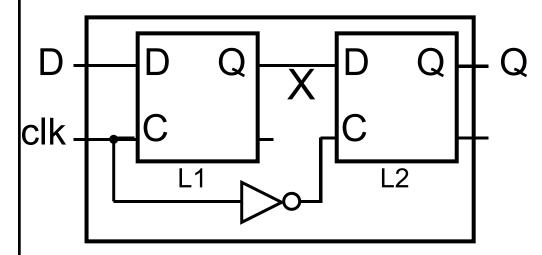

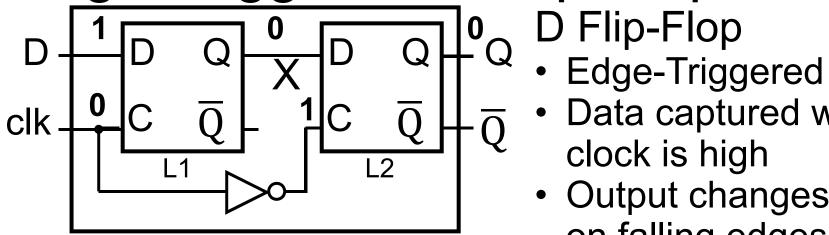

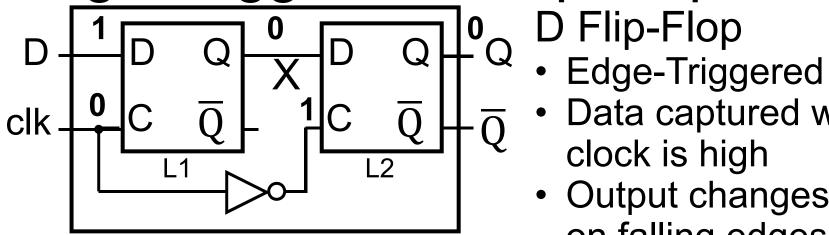

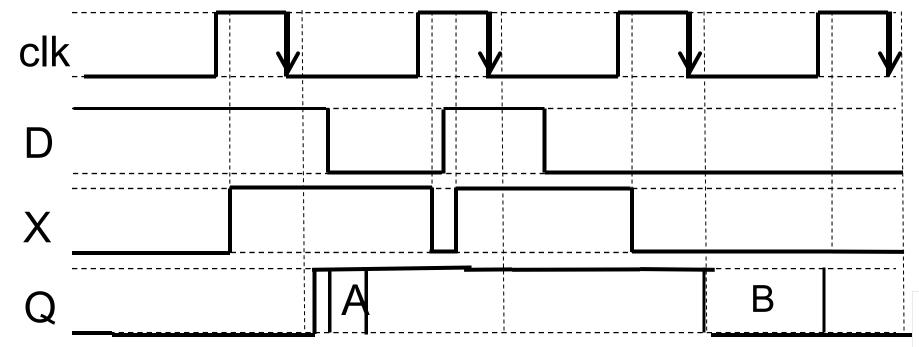

### Round 3: D Flip-Flop

- Edge-Triggered

- Data captured when clock high

- Output changes only on falling edges

### Round 3: D Flip-Flop

Clock = 1: L1 transparent L2 opaque

When CLK rises (0→1), now X can change, Q does not change

X passes through L2 to Q

Clock = 0: L1 opaque L2 transparent<sub>Clk</sub>.

When *CLK* falls  $(1\rightarrow 0)$ ,

Q gets X, X cannot change

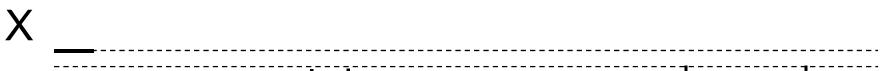

### iClicker Question - start here

What is the value of Q at A & B?

- a) A = 0, B = 0

- b) A = 0, B = 1

- c) A = 1, B = 0

- d) A = 1, B = 1

X

Q

Д

F

### iClicker Question - start here

What is the value of Q at A & B?

- a) A = 0, B = 0

- b) A = 0, B = 1

- $\bigcirc$  A = 1, B = 0

- d) A = 1, B = 1

D \_\_\_\_\_

# Edge-Triggered D Flip-Flop

- Data captured when clock is high

- Output changes only on falling edges

# Edge-Triggered D Flip-Flop

- Data captured when clock is high

- Output changes only on falling edges

## Takeaway

Set-Reset (SR) Latch can store one bit and we can change the value of the stored bit. But, SR Latch has a forbidden state.

(Unclocked) D Latch can store and change a bit like an SR Latch while avoiding a forbidden state.

An Edge-Triggered D Flip-Flip (aka Master-Slave D Flip-Flip) stores one bit. The bit can be changed in a synchronized fashion on the edge of a clock signal.

#### **Next Goal**

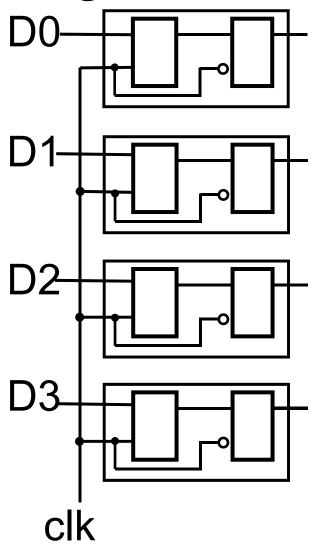

How do we store more than one bit, N bits?

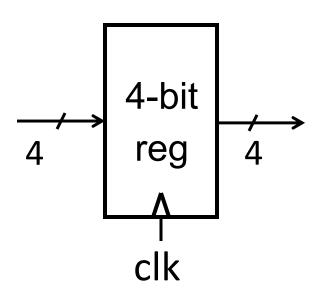

## Registers

#### Register

- D flip-flops in parallel

- shared clock

- extra clocked inputs:

write enable, reset, ...

## Takeaway

Set-Reset (SR) Latch can store one bit and we can change the value of the stored bit. But, SR Latch has a forbidden state.

(Unclocked) D Latch can store and change a bit like an SR Latch while avoiding a forbidden state.

An Edge-Triggered D Flip-Flip (aka Master-Slave D Flip-Flip) stores one bit. The bit can be changed in a synchronized fashion on the edge of a clock signal.

An *N*-bit **register** stores *N*-bits. It is created with *N* D-Flip-Flops in parallel along with a shared clock.

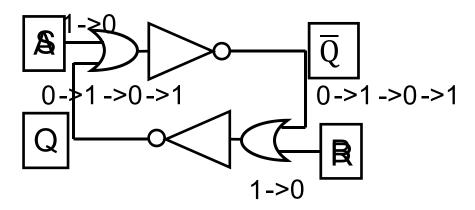

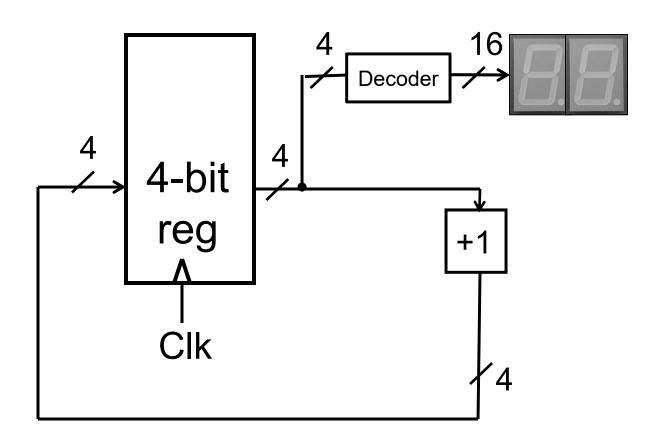

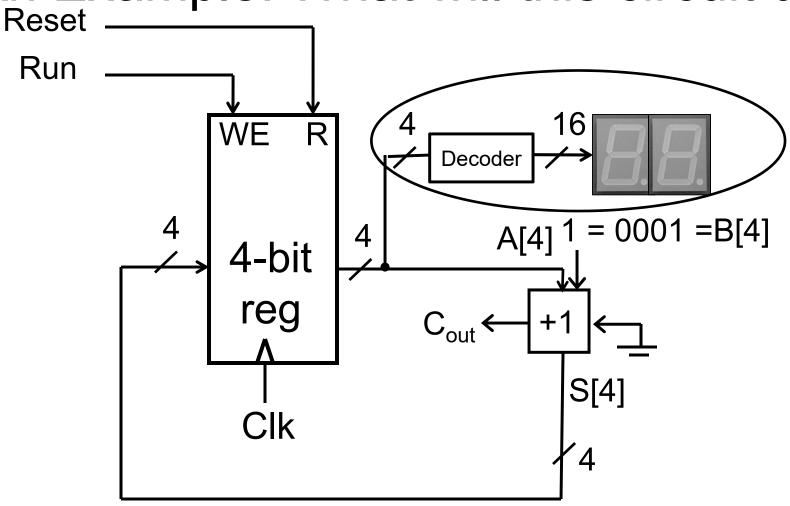

## An Example: What will this circuit do?

An Example: What will this circuit do?

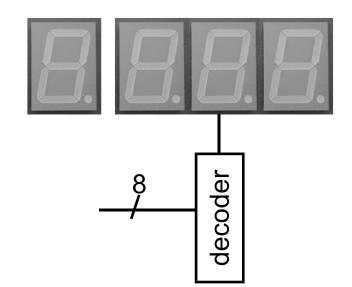

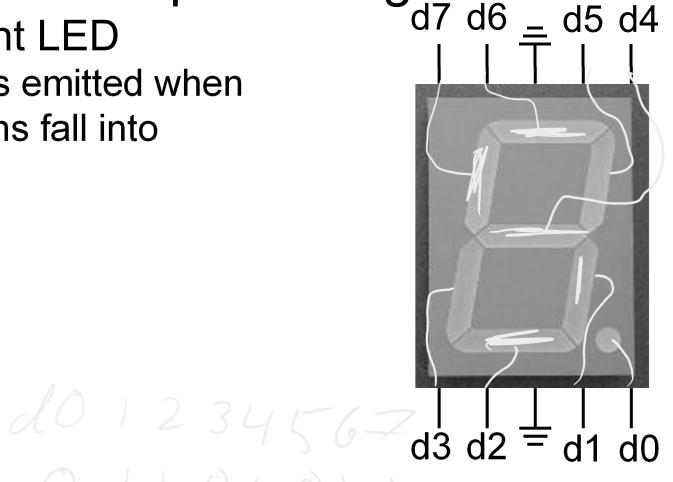

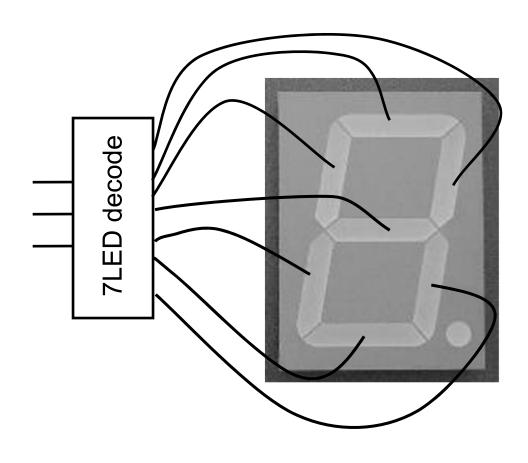

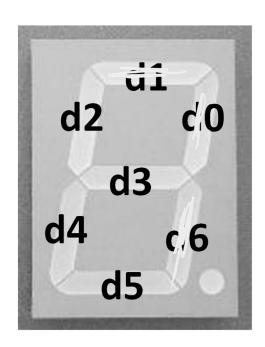

Decoder Example: 7-Segment LED d7 d6 \_ d5 d4

7-Segment LED

· photons emitted when electrons fall into holes

Decoder Example: 7-Segment LED d7 d6 \_ d5 d4

7-Segment LED

· photons emitted when electrons fall into holes

#### Decoder Example: 7-Segment LED Decoder

- 3 inputs

- encode 0 7 in binary

- 7 outputs

- one for each LED

### 7 Segment LED Decoder Implementation

| <b>b2</b> | b1 | b0 | d6 | d5 | d4 | d3 | <b>d2</b> | d1 | d0 |

|-----------|----|----|----|----|----|----|-----------|----|----|

| 0         | 0  | 0  |    |    |    |    |           |    |    |

| 0         | 0  | 1  |    |    |    |    |           |    |    |

| 0         | 1  | 0  |    |    |    |    |           |    |    |

| 0         | 1  | 1  |    |    |    |    |           |    |    |

| 1         | 0  | 0  |    |    |    |    |           |    |    |

| 1         | 0  | 1  |    |    |    |    |           |    |    |

| 1         | 1  | 0  |    |    |    |    |           |    |    |

| 1         | 1  | 1  | 1  | 0  | 0  | 0  | 0         | 1  | 1  |

### 7 Segment LED Decoder Implementation

| <b>b2</b> | b1 | b0 | d6 | <b>d5</b> | d4 | d3 | d2 | d1 | d0 |

|-----------|----|----|----|-----------|----|----|----|----|----|

| 0         | 0  | 0  | 1  | 1         | 1  | 0  | 1  | 1  | 1  |

| 0         | 0  | 1  | 1  | 0         | 0  | 0  | 0  | 0  | 1  |

| 0         | 1  | 0  | 0  | 1         | 1  | 1  | 0  | 1  | 1  |

| 0         | 1  | 1  | 1  | 1         | 0  | 1  | 0  | 1  | 1  |

| 1         | 0  | 0  | 1  | 0         | 0  | 1  | 1  | 0  | 1  |

| 1         | 0  | 1  | 1  | 1         | 0  | 1  | 1  | 1  | 0  |

| 1         | 1  | 0  | 1  | 1         | 1  | 1  | 1  | 1  | 0  |

| 1         | 1  | 1  | 1  | 0         | 0  | 0  | 0  | 1  | 1  |

### Basic Building Blocks We have Seen

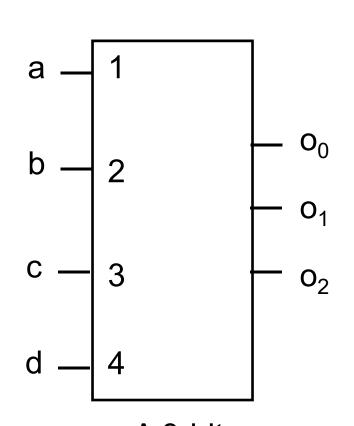

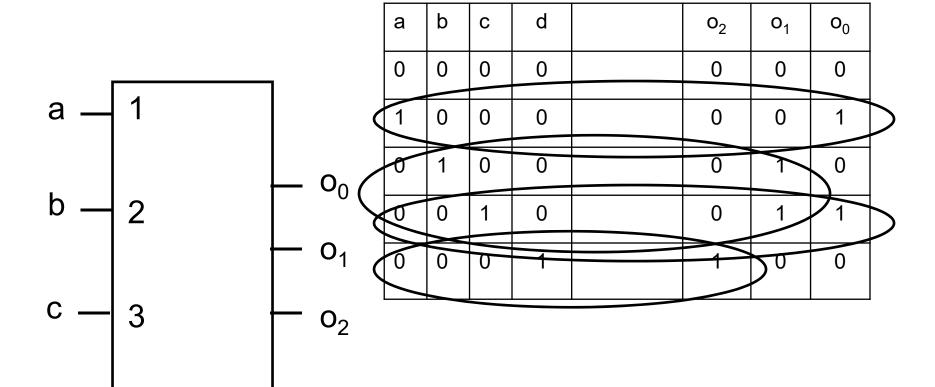

## Example Encoder Truth Table

| а | b | С | d |  |  |

|---|---|---|---|--|--|

| 0 | 0 | 0 | 0 |  |  |

| 1 | 0 | 0 | 0 |  |  |

| 0 | 1 | 0 | 0 |  |  |

| 0 | 0 | 1 | 0 |  |  |

| 0 | 0 | 0 | 1 |  |  |

A 3-bit encoder

with 4 inputs for simplicity

## Example Encoder Truth Table

A 3-bit encoder with 4 inputs

for simplicity

•

$$o_2 = \overline{abc}d$$

•

$$o_1 = abcd + abcd$$

•

$$o_0 = a\overline{b}\overline{c}d + a\overline{b}\overline{c}d$$

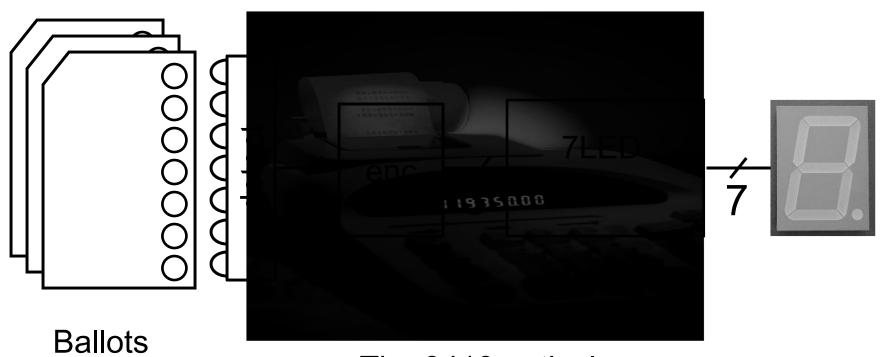

### Basic Building Blocks Example: Voting

The 3410 optical scan vote reader machine

### Basic Building Blocks We have Seen

### Recap

We can now build interesting devices with sensor

Using combinational logic

We can also store data values (aka Sequential Logic)

- In state-holding elements

- Coupled with clocks

## Summary

We can now build interesting devices with sensor

Using combinational logic

#### We can also store data values

- Stateful circuit elements (D Flip Flops, Registers, ...)

- Clock to synchronize state changes