## CS 316: Pipelining Hazards

#### Kavita Bala Fall 2007

Computer Science Cornell University

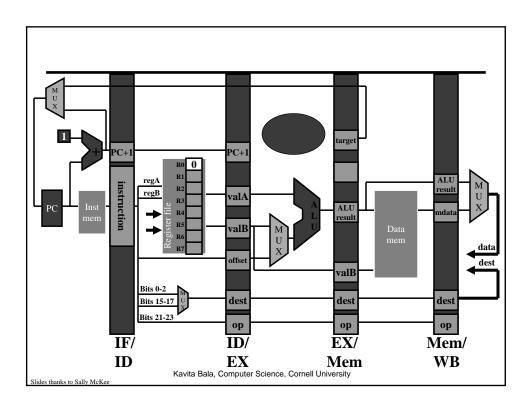

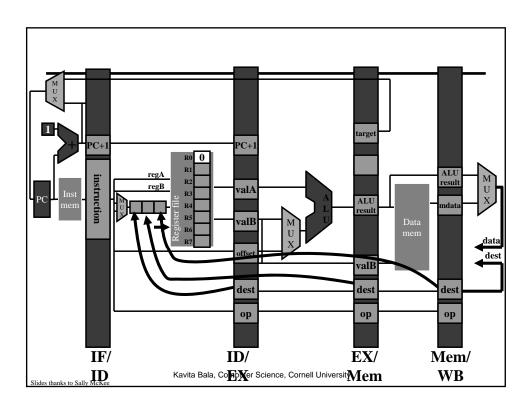

## **Basic Pipelining**

#### Five stage "RISC" load-store architecture

- 1. Instruction fetch (IF)

- get instruction from memory

- 2. Instruction Decode (ID)

- translate opcode into control signals and read regs

- 3. Execute (EX)

- perform ALU operation

- 4. Memory (MEM)

- Access memory if load/store

- 5. Writeback (WB)

- update register file

Following slides thanks to Sally McKee

# Pipelining Recap

- Powerful technique for masking latencies

- Logically, instructions execute one at a time

- Physically, instructions execute in parallel

- Instruction level parallelism

- Decouples the processor model from the implementation

- Interface vs. implementation

- BUT dependencies between instructions complicate the implementation

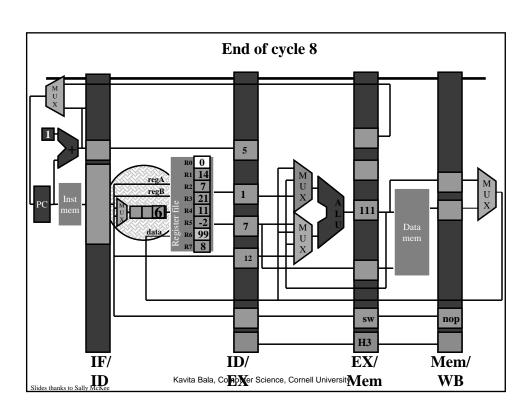

| Time Graphs                                       |       |        |         |         |           |           |           |           |           |

|---------------------------------------------------|-------|--------|---------|---------|-----------|-----------|-----------|-----------|-----------|

|                                                   |       |        |         |         |           |           |           |           |           |

| Time: 1                                           |       | 2      | 3       | 4       | 5         | 6         | 7         | 8         | 9         |

| add                                               | fetch | decode | execute | memory  | writeback |           |           |           |           |

| nan                                               | i     | fetch  | decode  | execute | memory    | writeback |           |           |           |

| lw                                                |       |        | fetch   | decode  | execute   | memory    | writeback |           |           |

| add                                               |       |        |         | fetch   | decode    | execute   | memory    | writeback |           |

| sw                                                |       |        |         |         | fetch     | decode    | execute   | memory    | writeback |

| Kavita Bala, Computer Science, Cornell University |       |        |         |         |           |           |           |           |           |

## What can go wrong?

#### Structural hazards

Two instructions in the pipeline try to simultaneously access the same resource

#### Data hazards

- A required operand is not ready

- Usually because a previous instruction in the pipeline has not committed it to the register file yet

#### Control hazards

- The next instruction to fetch cannot be determined

- Usually because a jump or branch instruction has not determined the next PC yet

Kavita Bala, Computer Science, Cornell University

Slides thanks to Sally McKe

#### What Can Go Wrong?

- Data hazards

- register reads occur in stage 2

- register writes occur in stage 5

- could read the wrong value if is about to be written

- · Control hazards

- branch instruction may change the PC in stage 4

- what do we fetch before that?

Kavita Bala, Computer Science, Cornell University

Slides thanks to Sally McKe

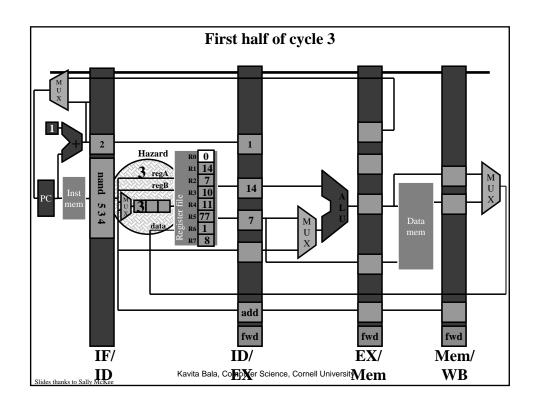

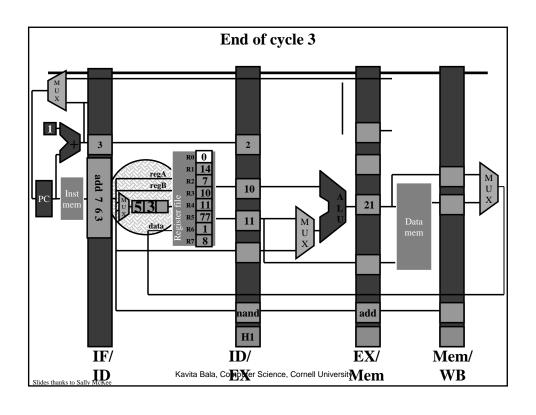

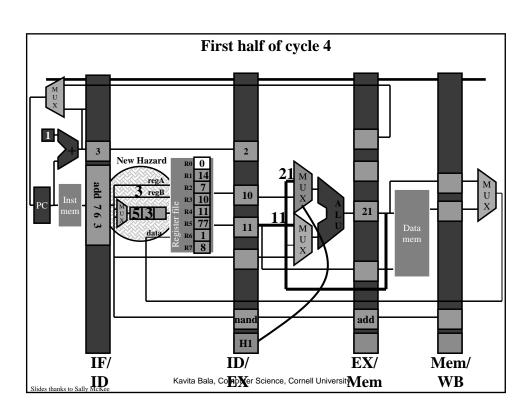

#### Different type of Hazards

Use register value in subsequent instruction

add 3 1 2

nand 5 3 4

or 6 3 1

sub 6 3 1

Kavita Bala, Computer Science, Cornell University

Slides thanks to Sally McKe

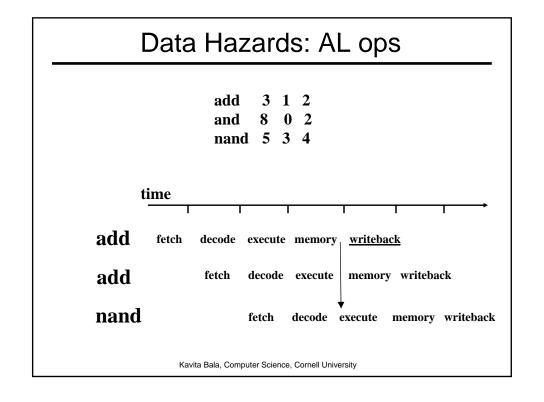

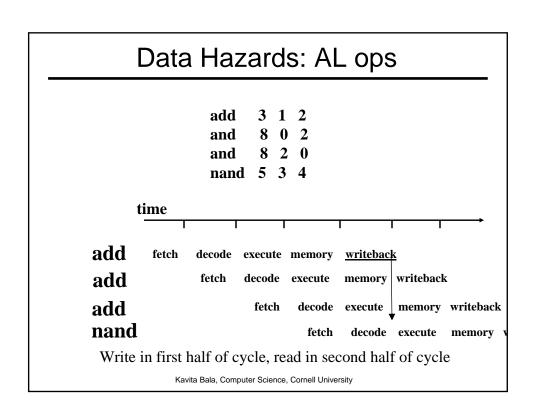

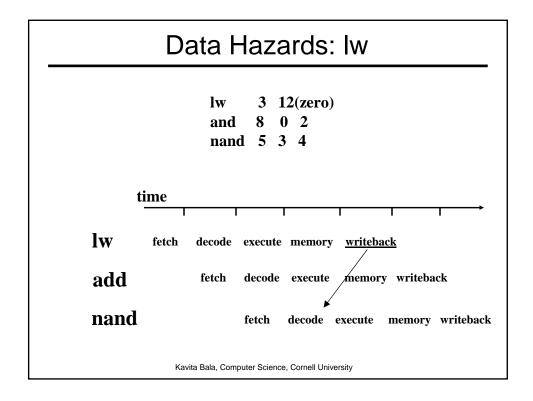

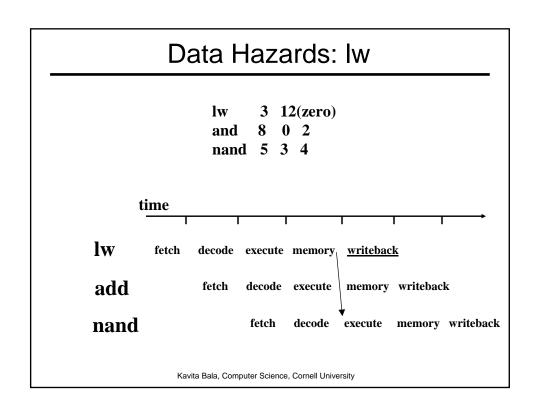

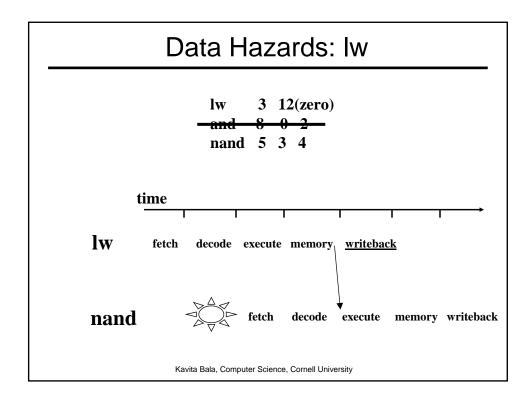

## Data Hazards: AL ops

add 3 1 2 nand 5 3 4

add fetch decode execute memory writeback

nand fetch decode execute memory writeback

If not careful, you read the wrong value of R3

Kavita Bala, Computer Science, Cornell University

# Data Hazards: AL ops

add 3 1 2 nand 5 3 4

time

add fetch decode execute memory writeback

nand dec

If not careful, you read the wrong value of R3

## Data Hazards: AL ops

add 3 1 2 nand 5 3 4

time

add fetch decode execute memory writeback

nand decode exc

If not careful, you read the wrong value of R3

Kavita Bala, Computer Science, Cornell University

# Data Hazards: AL ops

add 3 1 2 nand 5 3 4

time

add fetch decode execute memory writeback

nand decode execute memory writeback

If not careful, you read the wrong value of R3

# add 3 1 2 nand 5 3 4 time add fetch decode execute memory writeback nand fetch decode execute memory writeback

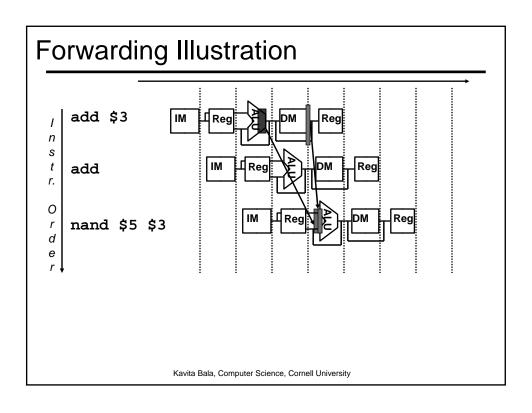

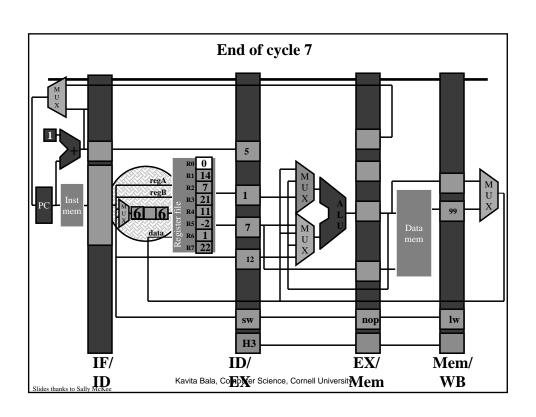

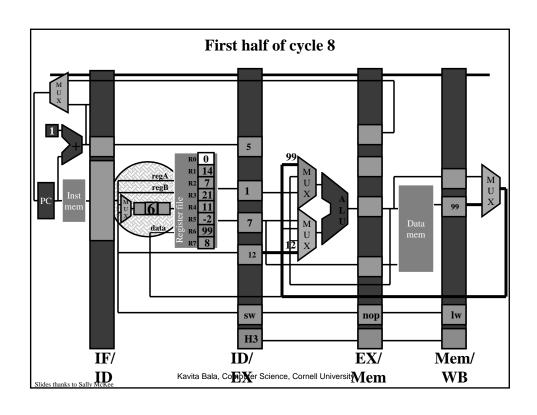

#### Handling Data Hazards: Summary

- Forward:

- New bypass datapaths route computed data to where it is needed

- Beware: Stalling may still be required even in the presence of forwarding

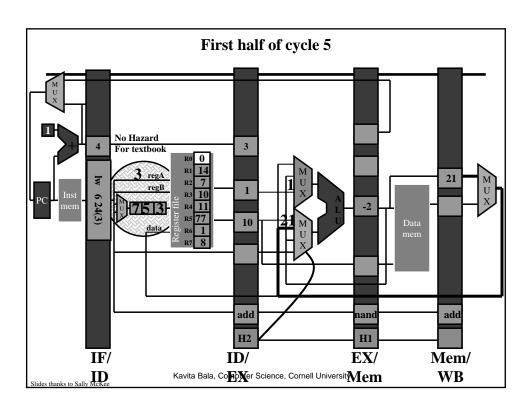

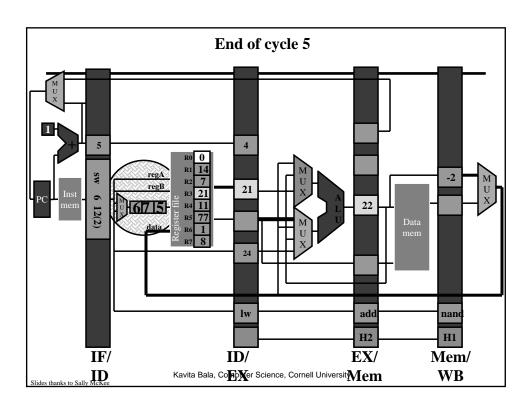

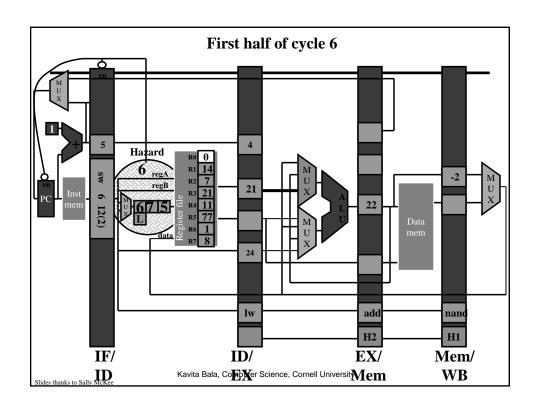

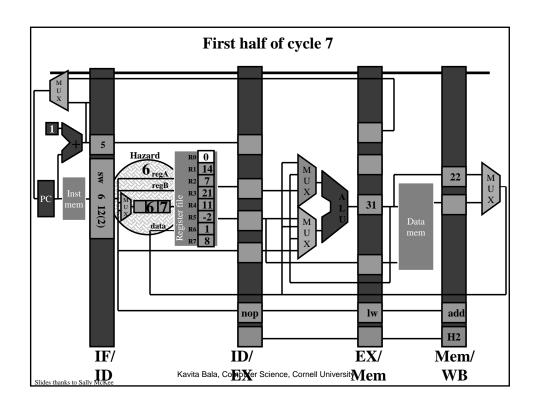

## Handling Data Hazards: Detection

- Detection

- Compare regA with previous DestReg (5 bits in MIPS)

- Compare regB with previous DestReg (5 bits in MIPS)

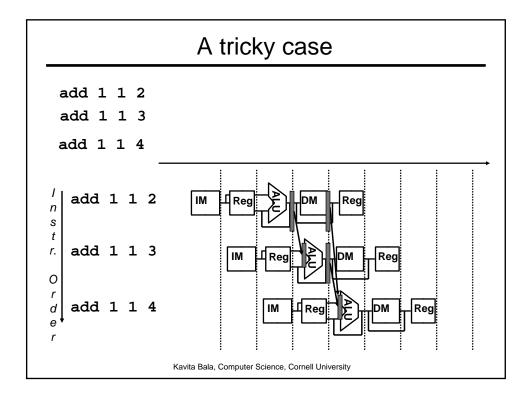

# Another tricky case

#### Handling Data Hazards: Forwarding

- No point forwarding to decode

- Forward to EX stage

- From output of ALU and MEM stages

Kavita Bala, Computer Science, Cornell University

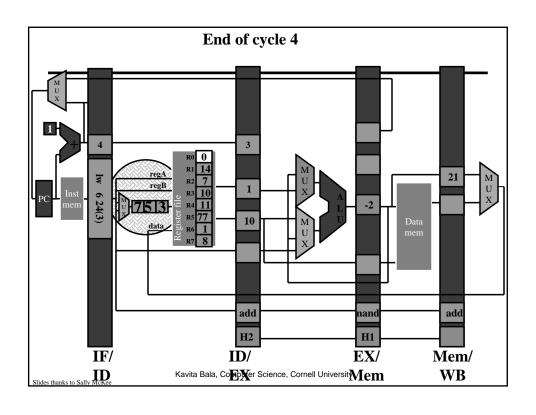

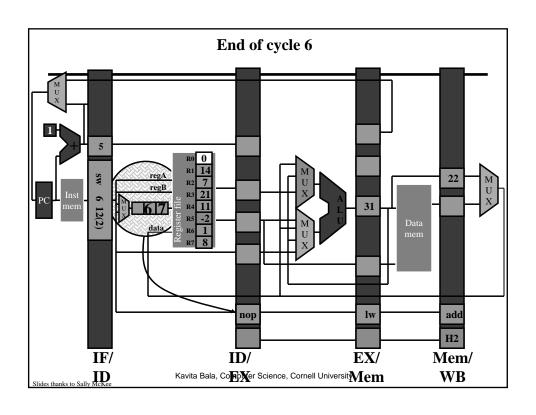

#### Sample Code

Which data hazards do you see?

add 312

nand 5 3 4

add 763

lw 6 24(3)

sw 6 12(2)

Kavita Bala, Computer Science, Cornell University

Slides thanks to Sally McKe

#### Sample Code

Which data hazards do you see?

# Handling Data Hazards: Stalling

#### **Control Hazards**

#### Stall

- Inject NOPs into the pipeline when the next instruction is not known

- Pros: simple, clean; Cons: slow

#### Delay Slots

- Tell the programmer that the N instructions after a jump will always be executed, no matter what the outcome of the branch

- Pros: The compiler may be able to fill the slots with useful instructions; Cons: breaks abstraction boundary

#### Speculative Execution

- Insert instructions into the pipeline

- Replace instructions with NOPs if the branch comes out opposite of what the processor expected

- Pros: Clean model, fast; Cons: complex

Kavita Bala, Computer Science, Cornell University