Combinational Logic

From lecture, we have seen the design of a 1-bit full adder. Now, let's try to add a carryin bit to the input:

| A | В | Cin | Sum | Cout |

|---|---|-----|-----|------|

| 0 | 0 | 0   | 0   | 0    |

| 0 | 0 | 1   | 1   | 0    |

| 0 | 1 | 0   | 1   | 0    |

| 0 | 1 | 1   | 0   | 1    |

| 1 | 0 | 0   | 1   | 0    |

| 1 | 0 | 1   | 0   | 1    |

| 1 | 1 | 0   | 0   | 1    |

| 1 | 1 | 1   | 1   | 1    |

The equations can be derived immediately as:

$$Sum = \underline{a} \underline{b} c + \underline{a} \underline{b} \underline{c} + \underline{a} \underline{b} \underline{c} + \underline{a} \underline{b} \underline{c} + \underline{a} \underline{b} \underline{c}$$

$$Cout = \underline{a} \underline{b} c + \underline{a} \underline{b} c + \underline{a} \underline{b} \underline{c} + \underline{a} \underline{b} \underline{c}$$

To simplify the equations, Karnot Maps should be used:

Sum:

|          | <u>b</u> <u>c</u> | <u>b</u> c | bс | b <u>с</u> |

|----------|-------------------|------------|----|------------|

| <u>a</u> | 0                 | 1          | 0  | 1          |

| a        | 1                 | 0          | 1  | 0          |

Cout:

|          | <u>b</u> <u>c</u> | <u>b</u> c | bс | b <u>с</u> |

|----------|-------------------|------------|----|------------|

| <u>a</u> | 0                 | 0          | 1  | 0          |

| а        | 0                 | 1          | 1  | 1          |

While Sum cannot be reduced further, Cout can be reduced to:

$$Cout = a c + a b + b c$$

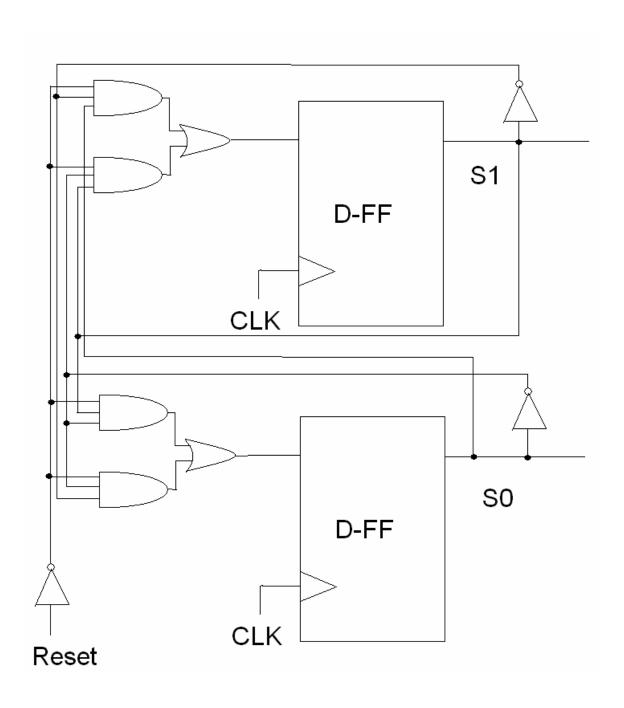

## Sequential Logic

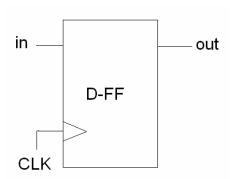

State holding element: D Flip-flop

On a positive edge of the clock signal, the D Flip-flop passes the input value to the output.

Now, let's implement a 2-bit counter:

| Reset | <b>S</b> 1 | <b>S</b> 0 | S1' | S0' |

|-------|------------|------------|-----|-----|

| 0     | 0          | 0          | 0   | 1   |

| 0     | 0          | 1          | 1   | 0   |

| 0     | 1          | 0          | 1   | 1   |

| 0     | 1          | 1          | 0   | 0   |

| 1     | 0          | 0          | 0   | 0   |

| 1     | 0          | 1          | 0   | 0   |

| 1     | 1          | 0          | 0   | 0   |

| 1     | 1          | 1          | 0   | 0   |

The equations of S0' and S1' can be derived as:

$$S1' = \underbrace{Reset}_{S0} \underbrace{S1}_{S0} + \underbrace{Reset}_{S1} \underbrace{S1}_{S0}$$

$$S0' = \underbrace{Reset}_{S1} \underbrace{S1}_{S0} + \underbrace{Reset}_{S1} \underbrace{S1}_{S0}$$

$$S0' = Reset S1 S0 + Reset S1 S0$$

And here's a gate diagram of the circuit: