## MINI-GRAPH PROCESSING

## Anne Weinberger Bracy

#### A DISSERTATION

in

## Computer and Information Science

Presented to the Faculties of the University of Pennsylvania in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

2008

Amir Roth Supervisor of Dissertation

Rajeev Alur Graduate Group Chairperson

## COPYRIGHT

Anne Weinberger Bracy

2008

## Acknowledgements

"It was the best of times, it was the worst of times, it was the age of wisdom, it was the age of foolishness, it was the epoch of belief, it was the epoch of incredulity, it was the season of Light, it was the season of Darkness, it was the spring of hope, it was the winter of despair, we had everything before us, we had nothing before us...." – Charles Dickens

Enough of the worst! Let me reflect only on the best. My graduate career led me to the best of all possible friends, professors, and colleagues. My mind is sharper, my life richer, and my heart fuller thanks to the years I spent at Penn, learning, living, and loving more than any stretch of time prior to graduate school.

I thank Amir Roth, whose passion for teaching and computer architecture converted me from a forced pupil in a required class to an inspired, budding researcher with a thirst for more knowledge and an empowering feeling that anything is possible in hardware. You have been a father and a friend. Thank you for setting the bar high and then helping me reach it.

I thank my committee chair, Milo Martin, for always having an open door and wise council. I also thank the members of my committee (past and present)—E Christopher Lewis, David Albonesi, Andre DeHon, and Insup Lee—for your expertise, advice, and encouragement.

My academic siblings—Vlad Petric, Tingting Sha, and Drew Hilton—have been the truest of friends. They are the ying to my yang, my one and only *Mei Mei*, and my knight in shining armor, respectively. My office mates—Marc Corliss, Colin Blundell, Prashant Prahlad, Joe Devietti, and Arun Raghavan—have been a source of strength and hilarity throughout my years at Penn. I will never forget the many late nights, early mornings, happy hours, and the wide variety of humor we shared in the most colorful, chaotic, and decked out office in Levine. J. Adam Butts generously made his degree of use framework available to me, for which I am very grateful.

I met many dear friends in graduate school: Ryan McDonald, Ameesh Makadia, Andrew McGregor, Tania Patsialou, Nick Montfort, Boulos Harb, Sid Suri, John Blitzer, Margaret DeLap, Aaron Evans, Katie Candland, and Jennifer Plummer. Christie Avraamides was hands down the best roommate I could ever have hoped for in my graduate school experience. Thanks for always reminding me to put jobs on the cluster before we went out at night. Patrick Coffman, Matt Ginzton, and Gabriel Adauto kept the Bay Area home fires burning for me. Erica Robles, Ethan Schuchman, and Hanna Wallach saved me hundreds of hours and thousands of dollars in therapy.

I am grateful to many people at Penn. Mike Felker has been a source of care and an administrative lifesaver from day one. Rita Powell nurtured the women in the department in countless ways and was always my personal cheerleader. Benjamin Pierce is a friend whose art and friendship I appreciated both in Levine and throughout Philadelphia. Dan Widyono kept our clusters up and running.

I thank my colleagues at the Microarchitectural Research Lab at Intel (past and present)—Hong Wang, Quinn Jacobson, John Shen, Drew Alduino, Joe Schutz, and Shekhar Borkar—for showing me the light at the end of the tunnel. Thanks also for the great confidence you had in me so early in my career.

Thanks to my family—Mom, Dad, Layne, Amy, Seth, Becca, Kevin, Andrew, Akiko, and Andy—for reminding me of the things that truly matter most. Mom and Dad, I could not have made it this far without your unconditional love and support. Thanks to the Weinberger clan—Anna Maria, Sabine, Lorenz, Fabian, Katharina, Bastian, and Suzanne—for encouraging me all these years. I am honored to have become a Weinberger in the middle of my graduate career.

A special thanks to my little Timo Quilliam Weinberger (my Mini-Graf?) for putting up with my dissertating for your entire thus-far mini-existence.

Finally, and most importantly, I thank my companion, husband, and best friend, Kilian Quirin Weinberger. You cheered me on; you cheered me up. You believed in me. In you I have found love, peace, laughter, and excitement for what lies ahead.

## ABSTRACT MINI-GRAPH PROCESSING Anne Weinberger Bracy Amir Roth

For years, single-thread performance was the most dominant force driving processor development. In recent years, however, the poor scaling of single-thread super-scalar performance and power concerns coupled with the ever-increasing number of transistors available on chip has changed the focus from single-thread performance to thread-level parallelism running on multi-core designs. The trend is for these cores to be narrower with smaller windows. This dissertation addresses the question of how to maintain—and, ideally, improve—single-thread performance under such constraints.

Mini-graph processing is a form of instruction fusion — the grouping of multiple operations into a single processing unit — that increases the instruction-per-cycle (IPC) throughput of dynamically scheduled superscalar processors in an efficient way. *Mini-graphs* are compiler-identified aggregates of multiple instructions that look and behave like singleton instructions at every pipeline stage, except for execute — there the constituent operations are retrieved and performed serially micro-code style. A mini-graph processor exploits instruction fusion to increase the efficiency of pipeline stages and structures that perform instruction book-keeping.

This dissertation describes a mini-graph architecture and evaluates it using cyclelevel simulation. A superscalar processor enhanced with mini-graphs can match the performance otherwise achieved with a wider, deeper superscalar processor. Experiments show that across four benchmark suites, the addition of mini-graph processing allows a dynamically scheduled 3-wide superscalar processor to match the IPC of a 4-wide superscalar machine.

## Contents

### Acknowledgements

| 1        | Intr | roduction                                    | 1 |

|----------|------|----------------------------------------------|---|

|          | 1.1  | Efficient Uniprocessors                      | 2 |

|          | 1.2  | Instruction Fusion                           | 3 |

|          | 1.3  | Mini-Graph Processing                        | 8 |

|          |      | 1.3.1 Maximizing Coverage                    | 9 |

|          |      | 1.3.2 Maximizing Amplification               | 2 |

|          |      | 1.3.3 Supporting Limited Latency Reduction   | 5 |

|          |      | 1.3.4 Minimizing Design Impact               | 6 |

|          |      | 1.3.5 Providing Robust Performance           | 6 |

|          | 1.4  | Results Summary                              | 8 |

|          | 1.5  | Contributions                                | 1 |

| <b>2</b> | Mir  | ni-Graph Architecture 24                     | 4 |

|          | 2.1  | Mini-Graph Criteria                          | 0 |

|          | 2.2  | Mini-Graph Encoding                          | 1 |

|          | 2.3  | Mini-Graph Execution                         | 8 |

|          |      | 2.3.1 ALU Pipelines                          | 8 |

|          |      | 2.3.2 Interlock-collapsing ALU Pipelines     | 6 |

|          |      | 2.3.3 Execution on multiple functional units | 0 |

iii

|   | 2.4 | Mini-(  | Graph Scheduling                                 |

|---|-----|---------|--------------------------------------------------|

|   |     | 2.4.1   | Reserving Result Busses and Register Write Ports |

|   |     | 2.4.2   | Reserving Functional Units                       |

|   |     | 2.4.3   | Coordinating Memory Instructions                 |

|   | 2.5 | Mini-0  | Graph Pre-Processing                             |

|   | 2.6 | Manag   | ging the Mini-Graph Table                        |

|   | 2.7 | ISA Is  | sues                                             |

|   | 2.8 | Archit  | ectural Issues                                   |

|   | 2.9 | Summ    | ary                                              |

| 3 | Min | ni-Grap | ph Selection 83                                  |

|   | 3.1 | Basic   | Coverage Maximizing Selection                    |

|   |     | 3.1.1   | Mini-Graph Identification                        |

|   |     | 3.1.2   | Greedy Selection Algorithm                       |

|   |     | 3.1.3   | Template Sharing                                 |

|   |     | 3.1.4   | Backtracking to Include Larger Templates         |

|   |     | 3.1.5   | Exhaustive Selection                             |

|   | 3.2 | Introd  | luction to Serialization                         |

|   |     | 3.2.1   | Basic Coverage Maximizing Selection              |

|   |     | 3.2.2   | What is Serialization?                           |

|   | 3.3 | Struct  | ural Selection Algorithms                        |

|   |     | 3.3.1   | $Struct_{None}$                                  |

|   |     | 3.3.2   | $Struct_{Bounded}$                               |

|   | 3.4 | Slack-  | Based Selection Algorithms                       |

|   |     | 3.4.1   | Slack <sub>Profile</sub>                         |

|   |     | 3.4.2   | Slack <sub>Dynamic</sub>                         |

|   |     | 3.4.3   | Analysis: Comparison with Exhaustive Search      |

|   | 3.5 | Relate  | ed Work on Aggregate Selection Schemes           |

|   |     | 3.5.1   | Treatment of Serialization                       |

|   |                | 3.5.2 Applicability to other Aggregate Schemes | 150 |

|---|----------------|------------------------------------------------|-----|

|   | 3.6            | Summary                                        | 151 |

| 4 | Per            | formance Analysis                              | 152 |

|   | 4.1            | Benchmark Suites                               | 152 |

|   | 4.2            | Performance Contribution Analysis              | 158 |

|   | 4.3            | In-Order Performance Analysis                  | 172 |

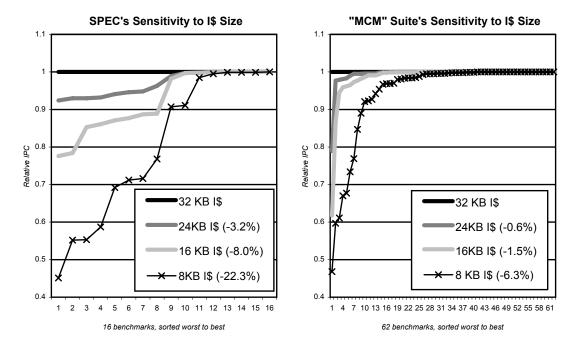

|   | 4.4            | Exploiting Instruction Cache Amplification     | 180 |

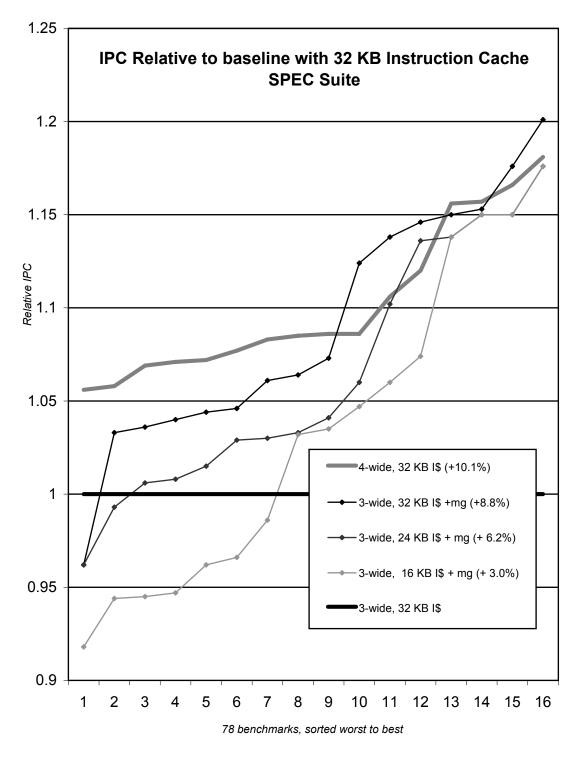

|   |                | 4.4.1 Instruction Cache Amplification for SPEC | 182 |

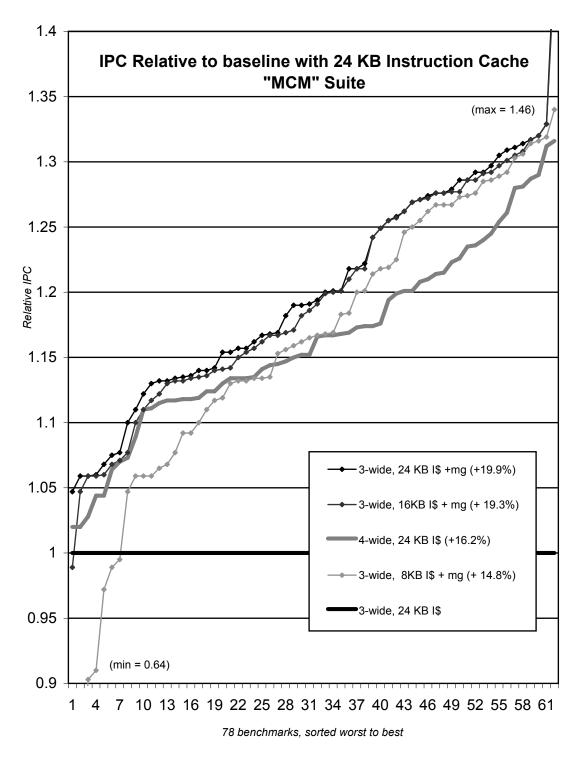

|   |                | 4.4.2 Instruction Cache Amplification for MCM  | 182 |

|   | 4.5            | MGT Configuration and Area Analysis            | 184 |

| 5 | $\mathbf{Rel}$ | ated Work                                      | 192 |

|   | 5.1            | Fusion Techniques                              | 192 |

|   | 5.2            | Non-Fusion Techniques                          | 200 |

| 6 | Cor            | nclusions                                      | 206 |

## List of Tables

| 2.1 | Possible Mini-Graph 32-Bit Instruction Formats                             |

|-----|----------------------------------------------------------------------------|

| 2.2 | Coverage Achieved with 1- and 2-Instruction Handles                        |

| 2.3 | Coverage Achieved with Possible Mini-Graph Instruction Formats $\ldots$ 34 |

| 2.4 | Coverage Rates                                                             |

| 2.5 | Input Connectivity Statistics                                              |

| 2.6 | ALU Instruction Distribution                                               |

| 2.7 | Coverage Variation and Shift Operations                                    |

| 3.1 | Coverage Summaries: Greedy vs. Exhaustive                                  |

| 3.2 | Coverage Summaries: Greedy vs. Integer Programming 103                     |

| 4.1 | Functional Properties of Benchmarks, Part 1                                |

| 4.2 | Functional Properties of Benchmarks, Part 2                                |

| 4.3 | Microarchitectural Properties of Benchmarks, Part 1                        |

| 4.4 | Microarchitectural Properties of Benchmarks, Part 2                        |

# List of Figures

| 1.1  | Instruction Processing                                | 3  |

|------|-------------------------------------------------------|----|

| 1.2  | Representation of Micro-op and Macro Fusion           | 6  |

| 1.3  | Timing of Micro-op and Macro Fusion                   | 6  |

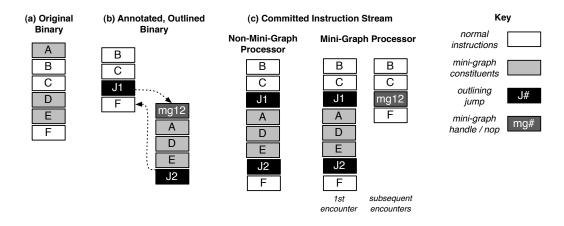

| 1.4  | Representing Mini-Graphs                              | 10 |

| 1.5  | Creating an Annotated, Outlined Binary                | 12 |

| 1.6  | 3-input, 3-stage ALU Pipeline                         | 13 |

| 1.7  | Mini-Graph Fusion                                     | 15 |

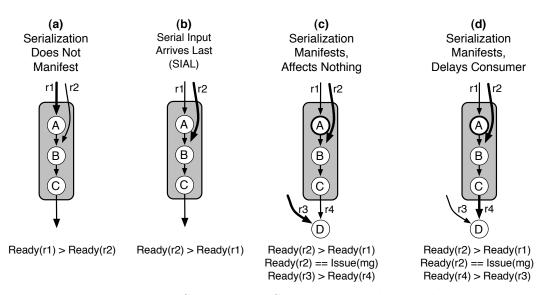

| 1.8  | Serialization Effects in Mini-Graphs                  | 17 |

| 1.9  | Simulation Configuration                              | 18 |

| 1.10 | Mini-Graph Coverage and Performance                   | 20 |

| 2.1  | Architectural Changes                                 | 25 |

| 2.2  | Mini-Graph Table and ALU Pipeline                     | 28 |

| 2.3  | Increasing Inputs vs. Increasing Outputs              | 34 |

| 2.4  | 7- and 5-Bank Mini-Graph Patterns                     | 39 |

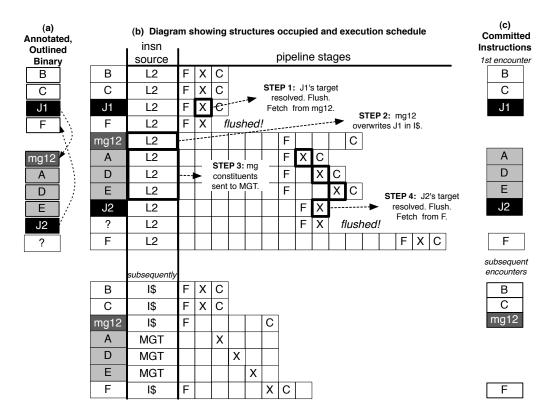

| 2.5  | Basics of Annotated Outlining                         | 42 |

| 2.6  | Annotated, Outlined Execution on Mini-Graph Processor | 42 |

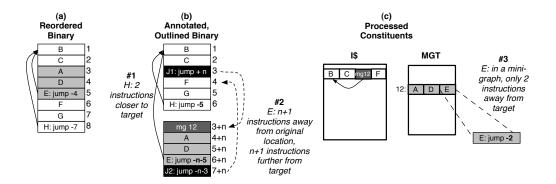

| 2.7  | Correcting branch offsets                             | 46 |

| 2.8  | 3-Stage ALU Pipeline                                  | 49 |

| 2.9  | Programming the ALU Pipeline                          | 50 |

| 2.10 | The ALU Pipeline in Action                            | 51 |

| 2.11 | Inter-Stage Connectivity within the ALU Pipeline      | 53 |

|      |                                                       |    |

| 2.12 | Support for Latency Reduction                              |

|------|------------------------------------------------------------|

| 2.13 | Internal and External Value Communication                  |

| 2.14 | External Value Coordination                                |

| 2.15 | External and Internal Value Coordination                   |

| 2.16 | Pseudo-Code for Creating a Mini-Graph Template             |

| 2.17 | Template Compilation Example                               |

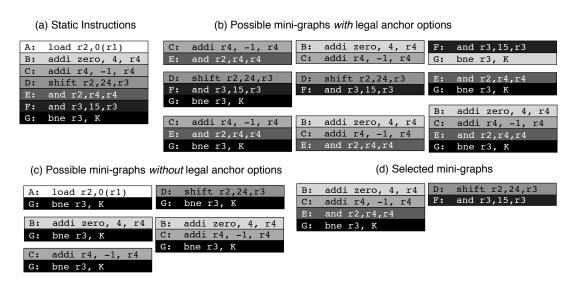

| 3.1  | Mini-Graph Identification                                  |

| 3.2  | Static instructions and their mini-graphs                  |

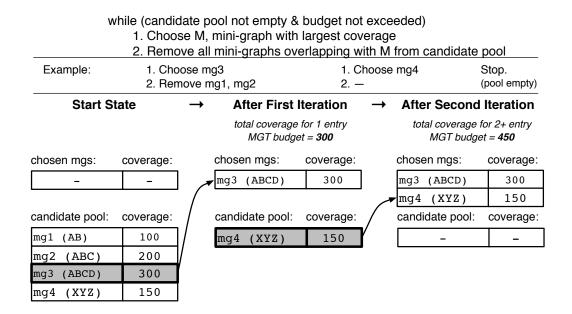

| 3.3  | Greedy selection algorithm                                 |

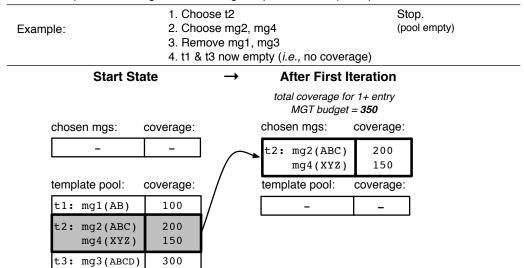

| 3.4  | Static instructions and their mini-graph templates         |

| 3.5  | Greedy selection with template sharing                     |

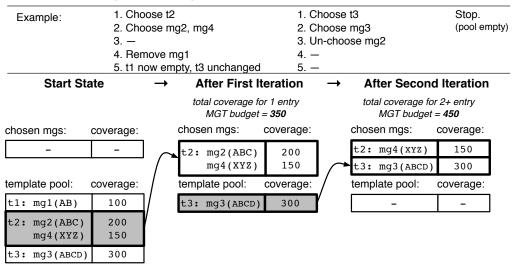

| 3.6  | Greedy selection with template sharing and backtracking 95 |

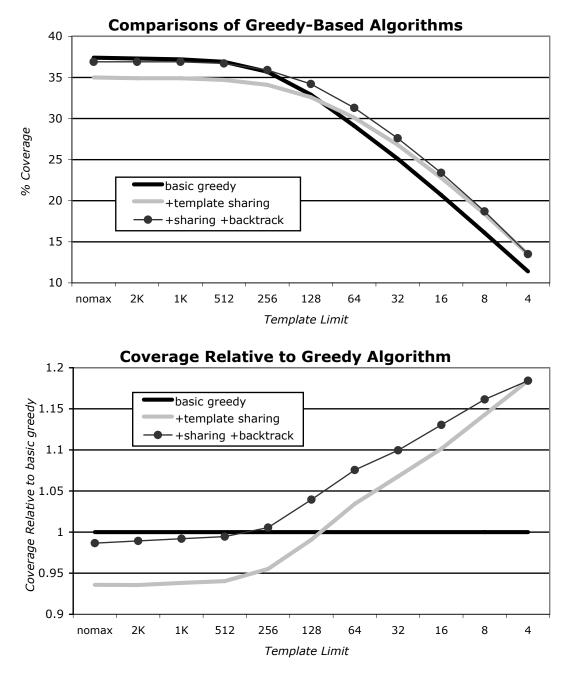

| 3.7  | Variations of Greedy Algorithm                             |

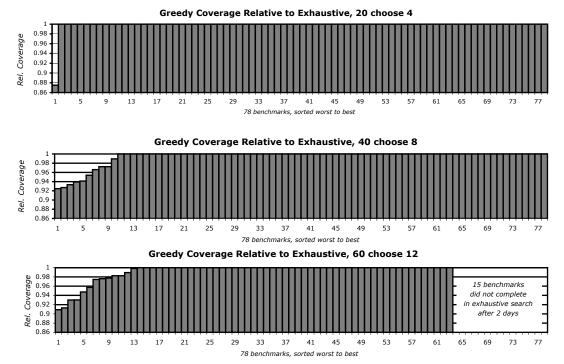

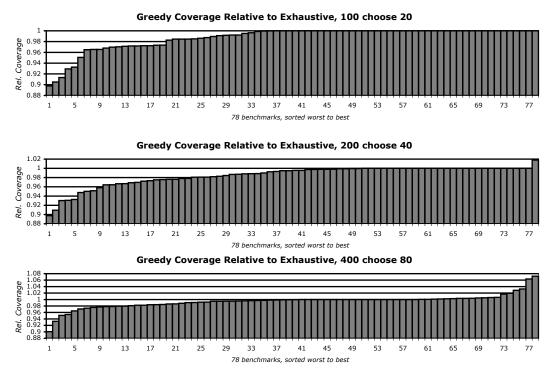

| 3.8  | Individual Benchmarks: Greedy vs. Exhaustive Search 100    |

| 3.9  | Individual Benchmarks: Greedy vs. Integer Programming 103  |

| 3.10 | Amplifying vs. Increasing Resources                        |

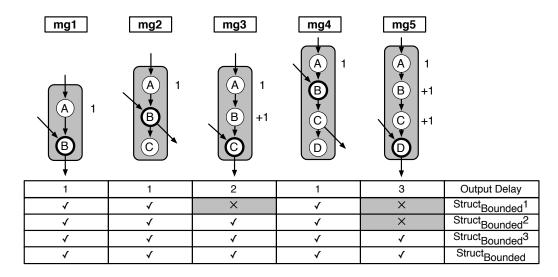

| 3.11 | Serialization Effects in Mini-Graphs                       |

| 3.12 | Basic Selection vs. Structural Pruning Selection           |

| 3.13 | Ignoring vs. Forbidding Serialization                      |

| 3.14 | Bounded vs. Unbounded Serialization                        |

| 3.15 | Serialization Bounded by Various Cycles                    |

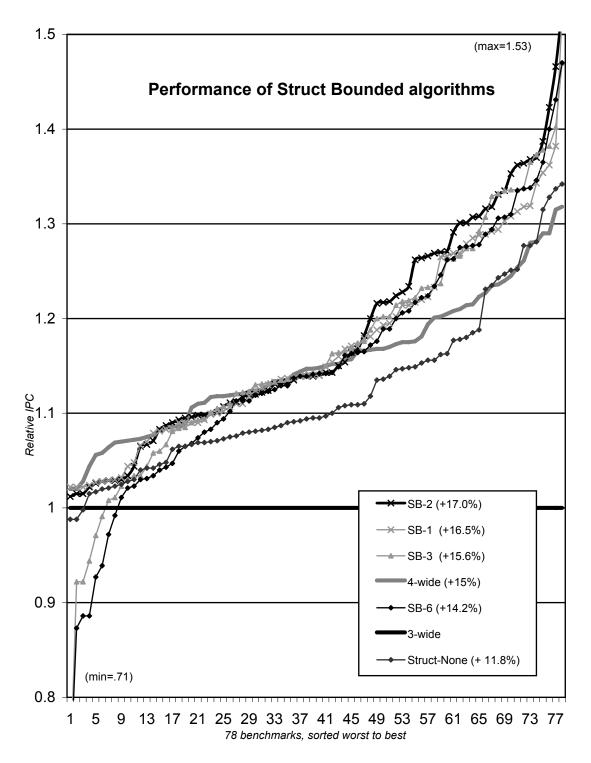

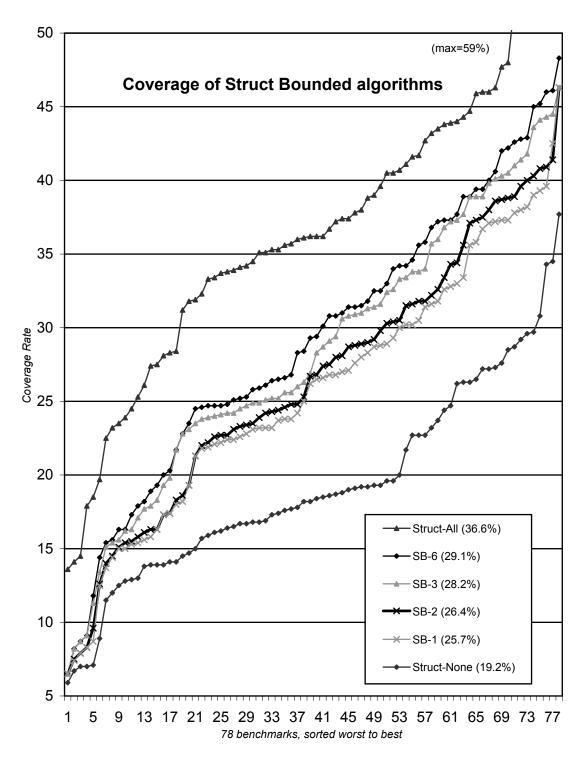

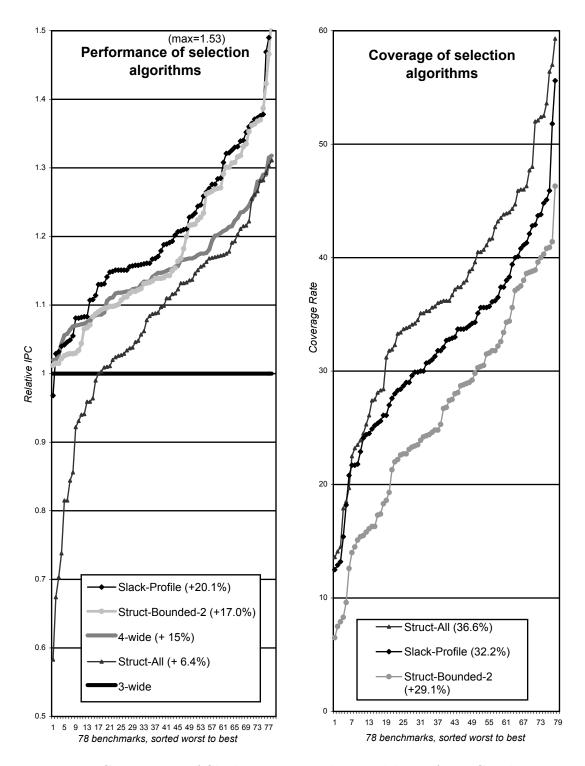

| 3.16 | $Struct_{Bounded}$ Performance                             |

| 3.17 | $Struct_{Bounded}$ Coverage                                |

| 3.18 | Structural vs. Slack-Based Pruning Selection               |

| 3.19 | Slack <sub>Profile</sub>                                   |

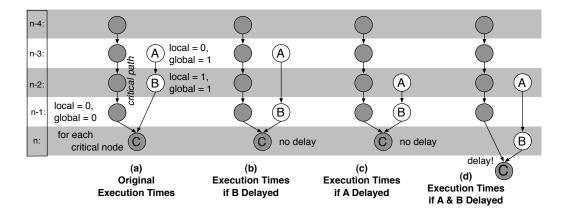

| 3.20 | Calculating Issue and Ready Times                          |

| 3.21 | Local vs. Global Slack                                     |

| 3.22 | Incorporating Local vs. Global Slack into Selection        |

| 3.23 | Comparison of $\text{Slack}_{\text{Profile}}$ with other models                                         | 131 |

|------|---------------------------------------------------------------------------------------------------------|-----|

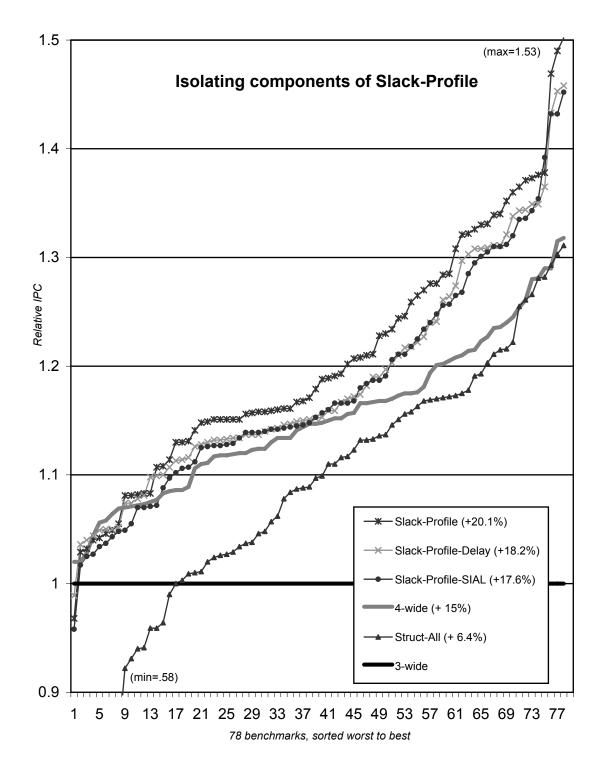

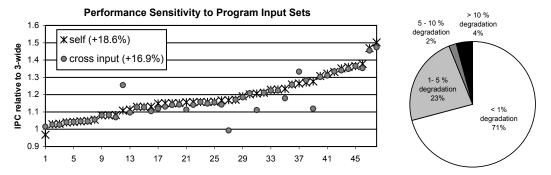

| 3.24 | Isolating Components of Slack <sub>Profile</sub>                                                        | 133 |

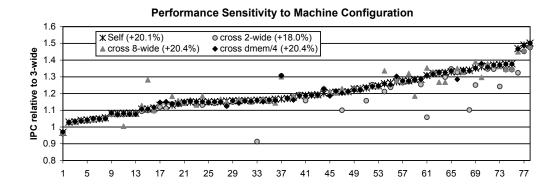

| 3.25 | $\operatorname{Slack}_{\operatorname{Profile}}$ Robustness: Microarchitecture Sensitivity (Performance) | 135 |

| 3.26 | $\operatorname{Slack}_{\operatorname{Profile}}$ Robustness: Microarchitecture Sensitivity (Breakdowns)  | 136 |

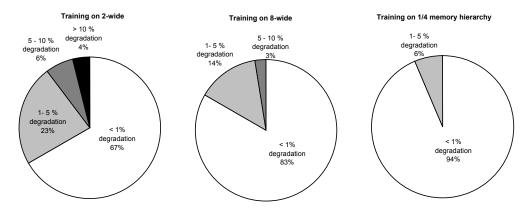

| 3.27 | $\operatorname{Slack}_{\operatorname{Profile}}$ Robustness: Program Input Sensitivity                   | 137 |

| 3.28 | Dynamic Serialization Scenarios                                                                         | 138 |

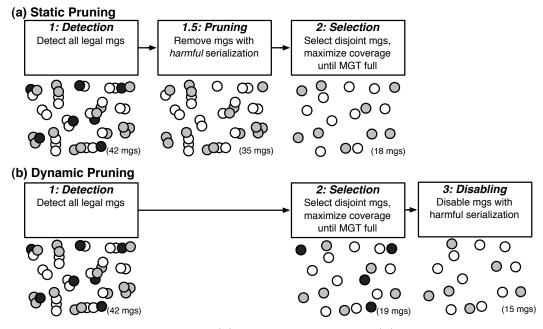

| 3.29 | Static vs. Dynamic Pruning Techniques                                                                   | 140 |

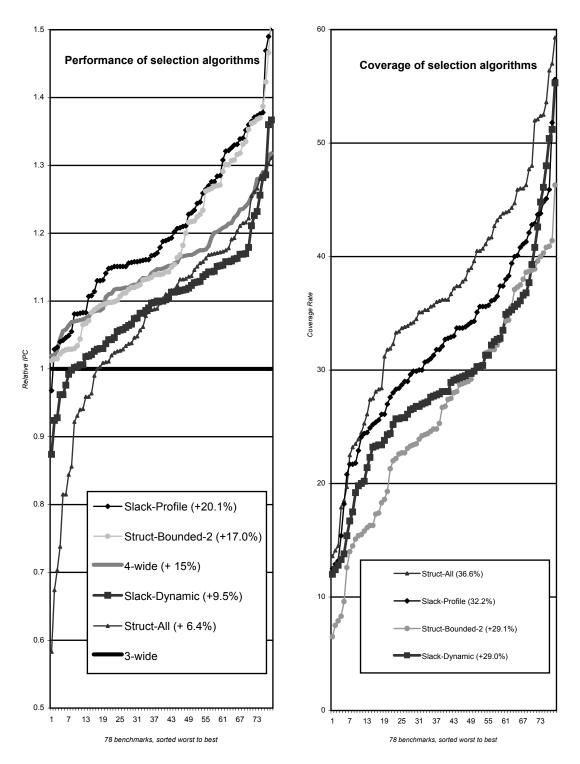

| 3.30 | Comparison of all Models                                                                                | 141 |

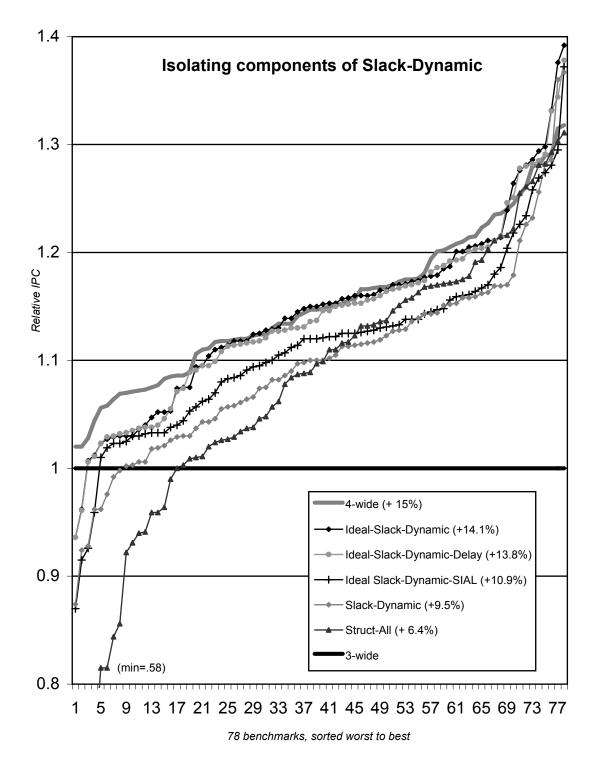

| 3.31 | Isolating Components of $\operatorname{Slack}_{\operatorname{Dynamic}}$                                 | 143 |

| 3.32 | Exhaustive Limit Study                                                                                  | 146 |

| 3.33 | Summary of Limit Study                                                                                  | 147 |

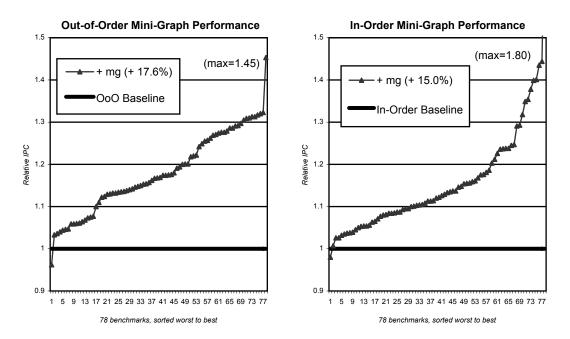

| 4.1  | Lone Contributors of Mini-Graph Performance                                                             | 161 |

| 4.2  | Isolating Components of Mini-Graph Performance Contributions                                            |     |

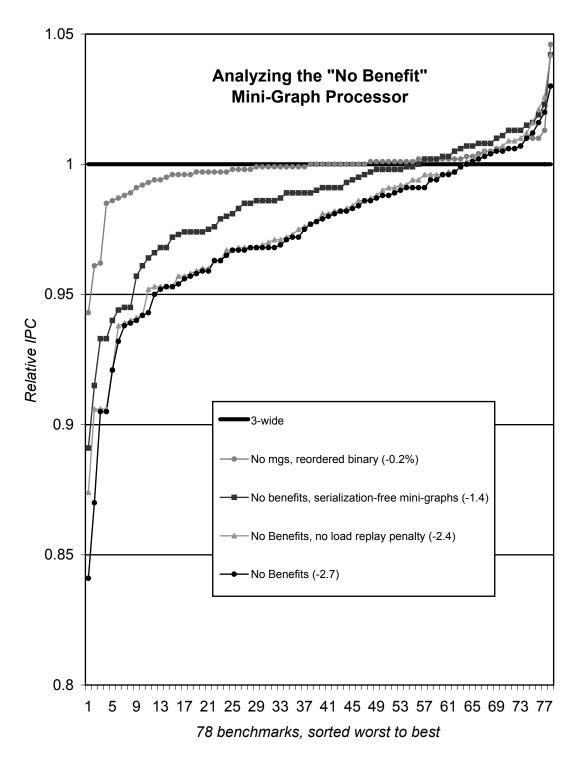

| 4.3  | Analyzing the "No Benefit" Mini-Graph Processor.                                                        | 165 |

| 4.4  | "No Benefit" Mini-graph Overhead                                                                        | 169 |

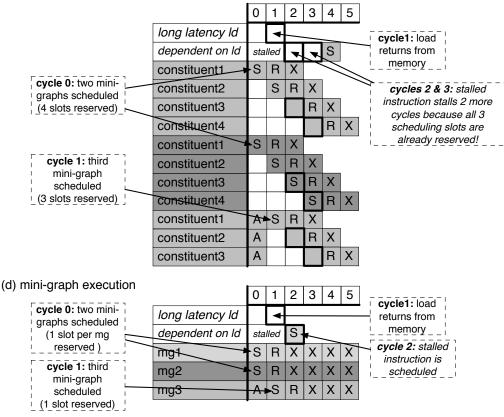

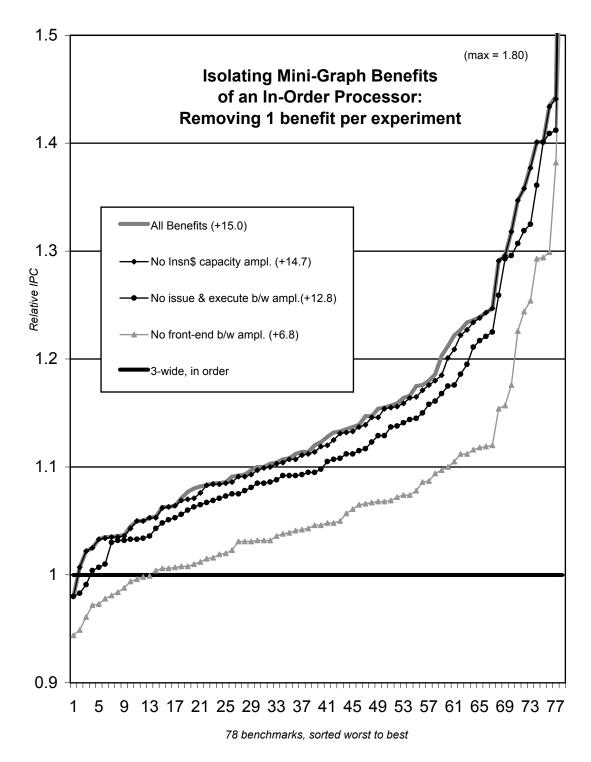

| 4.5  | Mini-graph performance in out-of-order and in-order contexts                                            | 173 |

| 4.6  | Lone Contributors of In-Order Mini-Graph Performance                                                    | 174 |

| 4.7  | Isolating Components of In-Order Mini-Graph Performance                                                 | 175 |

| 4.8  | Local Out-of-Order Execution Effect of Mini-graphs                                                      | 177 |

| 4.9  | Instruction Cache Behavior Differences                                                                  | 181 |

| 4.10 | Mini-Graph Performance with Various Instruction Cache Sizes, SPEC                                       | 183 |

| 4.11 | Mini-Graph Performance with Various Instruction Cache Sizes, MCM                                        | 185 |

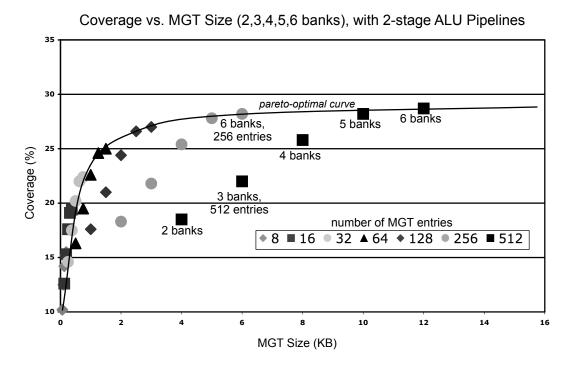

| 4.12 | MGT Coverage vs. Size in KB                                                                             | 187 |

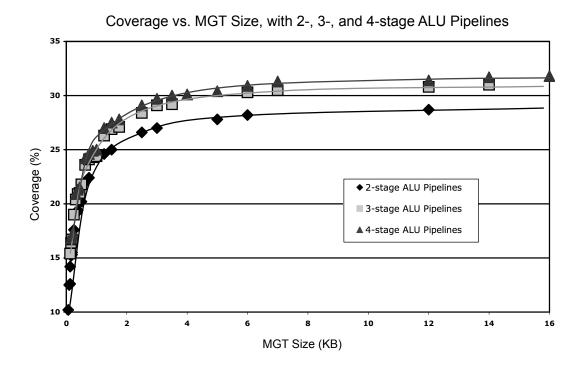

| 4.13 | Pareto-Optimal MGT Sizes for 2-, 3-, and 4-stage ALU Pipelines                                          | 188 |

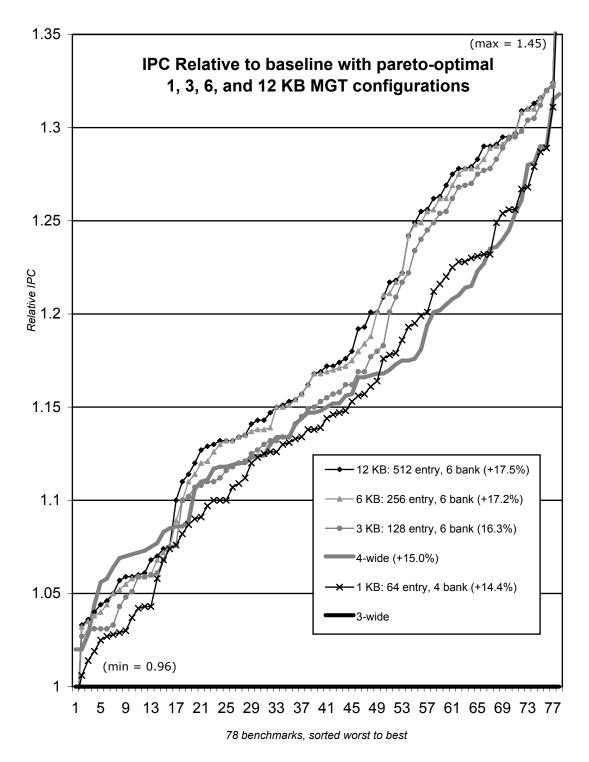

| 4.14 | Pareto-Optimal Mini-Graph Performance                                                                   | 189 |

## Chapter 1

## Introduction

Mini-graph processing is a form of instruction fusion — the grouping of multiple operations into a single processing unit — that increases the instruction-per-cycle (IPC) throughput of dynamically scheduled superscalar processors in an efficient way [12, 14]. A *mini-graph* is an atomic multi-instruction aggregate with the interface of a RISC singleton instruction that is processed as a single instruction at every pipeline stage, except for execute — there the constituent operations are retrieved and performed serially micro-code style. A software tool statically identifies mini-graphs and encodes them in the program binary on a per-application basis. Mini-graph processing improves IPC by amplifying the capacities and bandwidths of structures and stages that perform instruction bookkeeping and inter-operation register communication.

This dissertation describes a mini-graph architecture and evaluates it using cyclelevel simulation. Experiments show that across four benchmark suites, the addition of mini-graph processing allows a dynamically scheduled 3-wide superscalar processor to match the IPC of a 4-wide superscalar machine.

### **1.1** Efficient Uniprocessors

For years, single-thread performance was the most dominant force driving processor development. Performance was pursued through a combination of increasing clock frequencies and higher IPC throughput via wider, superscalar issue and more deeply speculative out-of-order execution.

In recent years, however, this approach has curtailed for two reasons. First, concerns about power have slowed the push for ever increasing frequencies. Second, IPC improving techniques such as pipeline and instruction window scaling have diminishing returns on investment. Not only is the marginal benefit of an additional issue slot, for example, sub-linear in terms of IPC, but it also diminishes; the  $n^{th}$  slot is less utilized than the  $n - 1^{th}$ . At the same time, the cost in terms of area, power, and delay is super-linear; the  $n^{th}$  slot costs more than the  $n - 1^{th}$  slot, because it raises the cost of the existing slots by requiring communication and coordination with them. The marginal benefit of an additional window entry is similarly sub-linear. As a consequence, many aspects of processor design are becoming less aggressive. Pipelines hit maximum depth with the Pentium 4 and subsequent designs have fewer pipeline stages. Some superscalar designs have been scaled to 5- and 6-wide [37, 46, 50, 93], but 4-wide appears to be the superscalar sweet-spot [106].

In response to the poor scaling of single-thread superscalar performance and the ever-increasing number of transistors available on chip, industry has decreed that future performance scaling will come from thread-level parallelism running on multicore designs. This approach places a premium on the area and power efficiency of individual cores. The trend, therefore, is towards narrower cores with smaller windows; but doing so lowers single-thread performance, a side-effect industry cannot afford. The question then remains, how to maintain—and, ideally, improve—single-thread performance under such constraints.

### **1.2** Instruction Fusion

Single thread performance is measured as the execution time of particular program:

program latency =  $\frac{\text{dynamic instruction count}}{IPC \times \text{clock frequency}}$

where IPC is the average number of instructions processed per cycle, and clock frequency is measured in cycles per second. Traditional approaches to performance improvement either increase clock frequency or throughput (IPC). This dissertation leverages instruction fusion, an alternative approach to performance improvement that focuses instead on the third component of the above equation: dynamic instruction count.

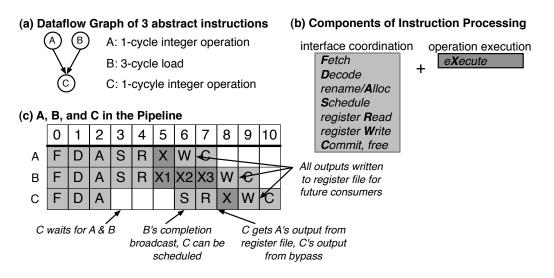

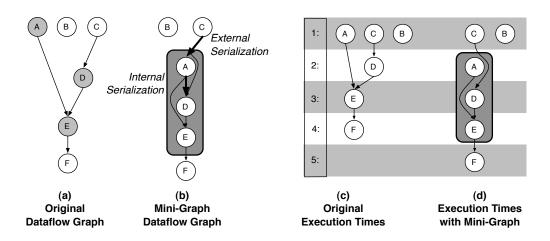

Figure 1.1: Instruction Processing: Interface Coordination + Operation Execution

Instruction = Interface + Operation. To reduce the dynamic instruction count, instruction fusion exploits the distinction between two aspects of instruction processing: operation execution and interface coordination. Consider the instruction "add r1, r2  $\rightarrow$  r3." Semantically, this instruction requires that an addition operation takes place. But processing this instruction is not just a matter of addition; it also concerns the instruction's inputs and outputs. Figure 1.1a shows the dataflow graph of three abstract instructions, A, B, and C. Figure 1.1b lists the pipeline stages required to process these instructions, separating the interface coordination (left) from the actual execution (right). Figure 1.1c shows these three instructions as they travel down the pipeline. At the execute stage (shaded), the instructions' actual operations are executed. Before and after executing the operations, a processor performs book-keeping and inter-operation communication steps. The operation is only a small component of the dynamic processing of an instruction; book-keeping and communication steps dominate with respect to cycles, pipeline stages, and on-chip resource usage.

Instruction fusion and resource amplification. The faithful execution of a program requires that the semantics specified by the operations in a binary not be changed. Interface coordination, however, is left to the processor's discretion. It is these coordinating steps that are combined in instruction fusion. Instruction fusion groups multiple operations into a single processing unit for select pipeline stages. During these stages, book-keeping and communication steps are performed on the aggregate rather than the individual operations.

Instruction fusion decreases the number of book-keeping and communication steps required per operation. The operation count is unaltered, but the number of interface-coordinating steps is decreased. Instruction fusion does not suffer from the diminishing performance returns on resource investment associated with widerissue, larger-instruction window superscalar processors. Instruction fusion does not increase the physical complexity (latency, area, power) of on-chip structures; on the contrary, it amplifies resources, and allows superscalar structures to be made simpler. Reducing the number of book-keeping steps required to execute a program *amplifies* the capacities and bandwidths of those resources dedicated to instruction book-keeping. Bandwidth amplification allows younger instructions to enter a particular stage earlier. For example, amplifying issue bandwidth allows some instructions to potentially issue sooner. Capacity amplification of a given structure potentially allows younger instructions to enter the structure sooner. For example, amplifying the register file allows instructions that might previously have stalled waiting for a free register to be renamed earlier.

The benefit of instruction fusion is proportional to its *dynamic coverage*, the percent of dynamic instructions embedded into aggregates. Coverage measures the resource amplification introduced by instruction fusion. A program with 30% dynamic coverage, for example, has approximately 30% fewer instructions at those pipeline stages for which fusion takes place. Coverage is defined by the following equation:

dynamic coverage =

$$\sum_{\forall mini-graphs}$$

,  $\frac{frequency(mini-graph) \times (size(mini-graph) - 1)}{\text{program's dynamic instruction count}}$

where *size* is the length of the mini-graph in number of instructions, and *frequency*

is the number of times each mini-graph is encountered throughout the execution of a program. Each time a 4-instruction mini-graph is encountered, for example, one instruction is processed where once there were 4 instructions; three instructions are internal to the mini-graph. Coverage rates directly translate to a commensurate reduction in the number of instructions needing book-keeping resources at those pipeline stages for which fusion takes place, be that fetch, rename, schedule, or commit, as well as a reduction in the number of values needing to be written to physical registers and the number of instructions requiring instruction and issue queue entries.

Micro-op and macro fusion. Two complementary instruction fusion techniques found in modern processors are *micro-op* and *macro fusion*. As real-world examples of instruction fusion, micro-op and macro fusion provide this dissertation with a useful backdrop for introducing and explaining mini-graph processing.

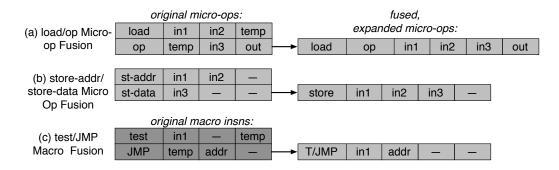

Micro-op fusion was introduced in Intel's Pentium M [38, 51], which fuses load/execute and store-address/store-data micro-op pairs into expanded micro-ops. Examples of each of these pairs are shown in Figure 1.2a-b. Load/execute and store instructions are x86/macro instructions. Instead of decoding the macro instruction

Figure 1.2: Representation of Micro-op and Macro Fusion.

into two micro-ops (shown on the left), micro-op fusion decodes them into a single, expanded micro-op (shown on the right). The expanded micro-op is a superset of its original micro-op constituents.

Figure 1.3: Timing of Micro-op and Macro Fusion.

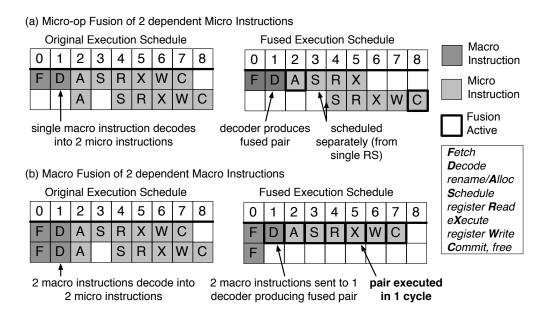

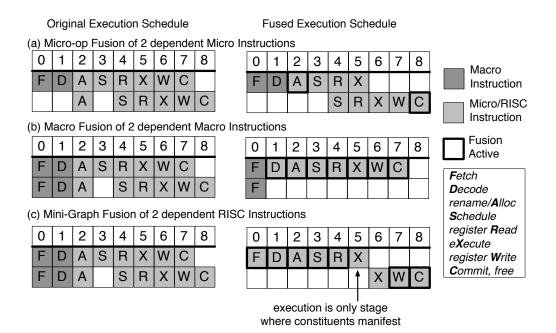

An example of micro-op fusion in the pipeline is shown in Figure 1.3a. On the left is the execution schedule of the original dependent micro-ops. On the right is the execution schedule under micro-op fusion. Micro-op fusion decodes the macro instruction into a single micro-op, which occupies a single reorder buffer (ROB) and issue queue entry. The ROB and the issue queue are amplified as a consequence. Micro-op fusion also reduces the number of micro-ops that are renamed and committed. Finally, by reducing the number of x86 instructions that decode into multiple micro-ops—such instructions decode on the lone complex decoder—micro-op fusion also amplifies the decode bandwidth. The constituents of the fused micro-op are still scheduled separately—one directed to the load unit, the other to a simple ALU—and therefore do not amplify issue or execution bandwidth [38].

Macro fusion was introduced in Intel's Core processor [72, 102]. Macro fusion fuses test or compare instructions to conditional branches. An example of the original micro-ops and the fused, expanded micro-op is shown in Figure 1.2c. An example of macro fusion in the pipeline is shown in Figure 1.3b. Whereas micro-op fusion fuses micro-ops after the decode stage, macro fusion fuses x86 macro instructions prior to the decode stage. Macro fusion further extends the benefit of fusion to execution latency reduction; as shown in the execution schedule, the fused instructions are executed in a single cycle on a modified branch unit. Because they are executed on a single functional unit, they are also issued atomically, unlike fused micro-ops.

Intel estimates that micro-op fusion reduces the number of micro-ops handled by the out-of-order logic by more than 10% [38]. In other words, it has 10% coverage. This assumes, however, that store instructions are already split in two. For those ISAs that do not make this assumption—like the Alpha ISA used to measure the coverage of mini-graphs—micro-op fusion would result in less coverage. Some estimates show that adding macro fusion to micro-op fusion increases coverage to just over 15%. The typical performance improvement offered by micro-op fusion for integer benchmarks is approximately 5%. Performance estimates for macro fusion have not yet been made publicly available at the time of this dissertation, but would likely create a total improvement between 7% and 10%. Although relatively simple to implement and moderately effective at reducing bookkeeping costs in the processor, both techniques are limited. First, neither of them offer fusion benefits that extend to the entire pipeline. Second, both forms of fusion apply to only two specific instruction pairings (load-and-execute and store-address-and-store-data for micro-op fusion, test/compare-branch for macro fusion).

### **1.3** Mini-Graph Processing

Mini-graph processing is an aggressive instruction fusion technique [12, 14]. In the context of micro-op and macro fusion, mini-graph processing can be thought of as a logical extension to both techniques.

Mini-graph processing is aggressive with respect to amplification, which it maximizes in two respects. First, it extends the benefits of fusion to more instruction combinations than the few pairing options available in micro-op and macro fusion. Second, it expands the scope of instruction fusion, extending its benefits to more pipeline stages and structures. At the same time, mini-graph processing remains conservative with respect to the changes it requires to the pipeline and ISA. The operating system need only be aware of mini-graph processing in order to disable it—a debugging aid, but not a necessity for correctness (see Section 2.2).

Moderate coverage rates provide incremental IPC improvements to the extent that amplified resources are performance limiters. With sufficiently high coverage rates, however, mini-graph processing can serve as a replacement for superscalar width and window size. To give a concrete example, if mini-graphs can achieve coverage/amplification rates of 33%, then a conventional 4-wide dynamically scheduled superscalar machine with a 128 entry reorder buffer and a 64 entry issue queue can be replaced with a 3-wide superscalar with a 96 entry reorder buffer and 48 entry issue queue *plus* mini-graph support. This goal is accomplished in the following five steps.

#### **1.3.1** Maximizing Coverage

Micro-op and macro fusion both focus on fusing pre-defined operation pairs. Minigraph processing supports fusion of larger instruction aggregates (called *mini-graphs*) and also application-specific fusion. These capabilities require three pieces of innovation. The first is the separation of the mini-graph interface from the mini-graph operations. The second is an on-chip structure, the Mini-Graph Table, that stores the internal definition of each mini-graph's operations. The third is an encoding mechanism, called *annotated outlining*, whereby mini-graphs can be encoded into a binary and subsequently used to program the Mini-Graph Table at runtime.

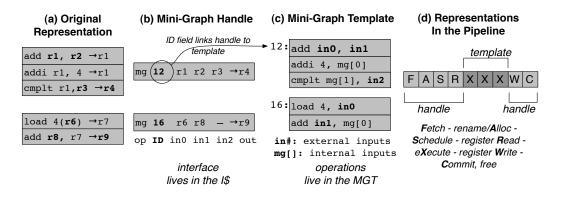

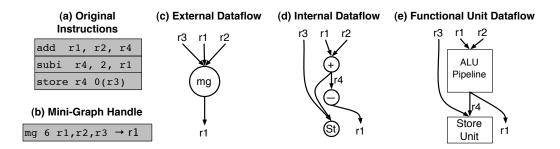

Instruction = Handle + Template. Mini-graphs are manipulated at two levels: the handle and the template. The interface is represented by a *handle*, a quasi-instruction that the mini-graph processor manipulates while the mini-graph travels down the pipeline. The mini-graph handle has three components: an opcode, register specifiers, and an immediate field. Mini-graphs use a reserved opcode mg, which can be any opcode (or several opcodes) that would be interpreted as a nop by a non-mini-graph processor. The handle is meaningful only to a mini-graph enabled processor.

The handle specifies three register inputs and an output. The four register names explicit in a handle are the mini-graph's interface registers which define its external dependences. These register names (or their renamed versions) are needed at renaming, scheduling, register read, register write, retirement, and mis-speculation recovery; stages where only the handle is available, not the complete mini-graph. Finally, the handle has an immediate field, the MGID, that links the handle to its internal definition. The MGID connects the mini-graph interface to its definition, specifying which mini-graph template should be invoked at execute. In this respect, it is similar to the parameterizable instruction used to exploit hardware-programmable functional units on a PRISC machine [83]. Using the MGID rather than, say, the address of the handle, allows two different, static locations of code to invoke the same mini-graph template.

The *template* encodes the mini-graphs's internal definition. A mini-graph template specifies the exact constituent operations (opcodes and immediates) as well as the internal register dataflow of the mini-graph. Each template is assigned a unique identifier which is stored in the handle's MGID field. Because the template specifies internal register dataflow without using actual register names, a single template can be used to specify mini-graphs in multiple static locations in the code.

Figure 1.4: Representing Mini-Graphs: Handles and Templates.

Mini-graph representation example. Figure 1.4a shows two instruction sequences. Figure 1.4b shows the handle that summarizes each sequence. The MGID, 12 and 16, indexes the corresponding definitions of the mini-graphs. Figure 1.4c shows the template for each mini-graph. Note, this figure is logical; the organization and contents of the actual structure that holds templates are described later. External input registers are denoted with a combination of in and their index in the handle (0,1,2) while interior values are denoted using mg[] indexed with the mini-graph instruction that creates them. For example, the third mini-graph constituent of mg12, cmplt r1, r3,  $\rightarrow$  r4 is represented as cmplt mg[1], in2 where in2 is interface input register r3 and mg[1] is output of the second mini-graph instruction. Interior values such as mg[1] are provably transient by static analysis and do not need to be stored in registers at runtime.

Finally, Figure 1.4d illustrates which representations are used at which pipeline stages. Whereas the interface is needed throughout the pipeline, the mini-graph definition is needed only at the schedule and execution stages. At schedule, a summary of mini-graph resource needs (not shown) directs resource reservations required to schedule the handle; at execution, the template drives constituent execution.

The Mini-Graph Table (MGT). Mini-graphs exploit the most common operational idioms found for each program. Fused pairs supported by micro-op fusion (e.g., load-and-execute) require permanent changes to the decoder and scheduler and are therefore conservatively general so as to have utility across all possible programs. Mini-graphs, on the other hand, can be defined for a single program. The enabling mechanism for this flexibility is the MGT.

The MGT factors fused execution information out of the decoder and issue queue and into a separate structure. This means that the decoder is modified only to recognize the class of instructions known as mini-graphs. Furthermore, this allows a conventional issue queue and conventional scheduler to drive the execution of arbitrary aggregates.

The MGT holds all the template definitions for every mini-graph handle occurring in a particular program binary. During execution, a mini-graph processor invokes the MGT to drive a cycle-by-cycle execution of the constituent operations, micro-code style. The handle has an immediate field called the MGID, which is serves as the index into the MGT. Using an MGID field to index into the MGT enables multiple dynamic locations of semantically identical instruction sequences to use a single MGT entry. The MGT is implemented as a cache. MGT size is not part of the architected state of a mini-graph processor, but informing the software tool that prepares the mini-graph binary with the MGT size can improve performance (see Section 2.6).

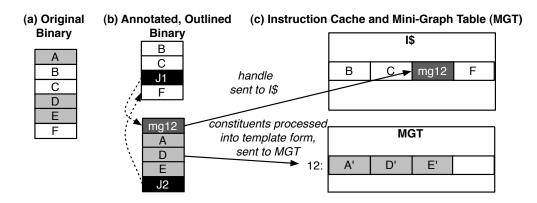

Annotated outlining. Annotated outlining is a novel encoding scheme used to transform a standard binary into a mini-graph binary. The process is shown in Figure 1.5. First, the instructions that form the body of the mini-graph are made contiguous and prepended with the mini-graph handle. This extended sequence is then "outlined" from the code (as opposed to "inlined") using a pair of jumps (Figure 1.5b). As shown in Figure 1.5c, the instruction cache fill path recognizes the handle and places it in the instruction cache. The mini-graph constituent operations are preprocessed into template form and diverted to the MGT at the index corresponding to the handle's MGID.

Figure 1.5: Creating an Annotated, Outlined Binary

#### **1.3.2** Maximizing Amplification

Mini-graph processing not only increases coverage to arbitrary combinations of instructions, but it also extends the benefits of amplification to new pipeline stages and structures. Micro-op and macro fusion amplify decode, rename, and commit bandwidth, and issue queue and reorder buffer capacity. Because their target processors perform architectural register and ROB-style renaming, amplifying ROB capacity has the same effect that amplifying register file capacity has on a processor that performs physical register renaming. Mini-graphs extend bandwidth amplification to fetch, register read/write, and integer execution and capacity amplification to the instruction cache. Doing this requires three pieces of innovation.

Amplifying instruction cache capacity and fetch bandwidth. Instruction

cache capacity and fetch bandwidth amplification is one of many benefits of annotated outlining. This benefit comes as the simple consequence of representing an entire mini-graph as a single instruction (*the handle*) in the instruction cache.

Amplifying the register file. Without static analysis to guarantee the transience of values, micro-op and macro fusion can target instruction pairs that have at most one register output. Consecutive load and op x86 macro instructions cannot be fused because they could have more than one output; load and op instructions from the *same* macro instruction can only have a single output because the value passed from the load to the op is deemed transient by the compiler and therefore never assigned to a register. Hence, the number of values written and communicated globally does not change as a result of micro-op fusion. Mini-graph processing targets instruction groups whose constituents may produce multiple values, so long as all but one of these values are statically, provably *transient*—existing only within the mini-graph. Value communication is orchestrated by the MGT using bypasses and latches without actual registers, amplifying register file capacity and register read and write bandwidth. Transience is determined through static liveness analysis, and—to guarantee transience—mini-graphs are atomic.

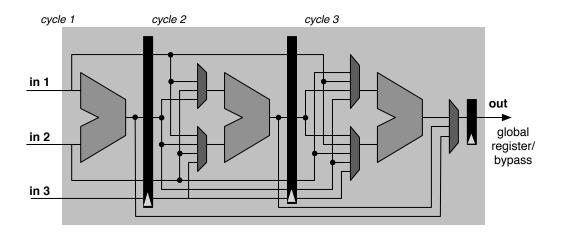

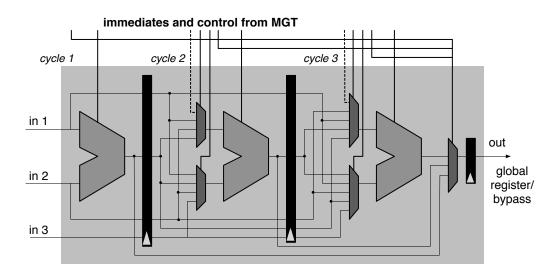

Figure 1.6: 3-input, 3-stage ALU Pipeline

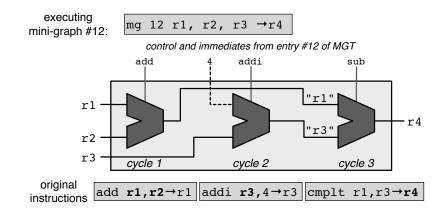

Amplifying execution with ALU Pipelines. Mini-graph processors further exploit mini-graph interior value transience by executing chains of integer constituents on a new, multi-cycle functional unit called an *ALU Pipeline*: a single-entry, single-exit chain of ALUs. An ALU pipeline is essentially a multi-cycle functional unit (like a multiplier). Figure 1.6 shows a 3-input, 3-stage ALU pipeline executing the previously shown mg12. In the case of mg12, the inputs arrive at the beginning of cycle 1 and the output is ready at the end of cycle 3. At each cycle, each ALU receives the requisite immediates and control signals from the MGT. Transient values are propagated via the forward-only operand network between ALUs and do not access the register file. The execution of multiple mini-graphs may be pipelined across this new functional unit.

ALU Pipelines play a critical amplification role. Because execute is the only pipeline stage that manipulates constituents rather than handles, it is the only pipeline stage whose bandwidth is not naturally amplified by fusion. ALU Pipelines prevent execution from becoming a new bandwidth bottleneck by adding integer ALU execution bandwidth (which is relatively inexpensive) without commensurate increases in global bypass, register file, and scheduling bandwidths (which are more expensive). Because singleton instructions can also execute on ALU pipelines with no performance penalty, a mini-graph processor simply replaces some of its ALUs with ALU pipelines.

**Putting it all together.** Figure 1.7a-b shows the execution schedules of microop and macro fusion (unchanged from Figure 1.3). Figure 1.7c shows the same for mini-graph processing. Unlike the micro-op and macro fusion, mini-graphs are fused for the entire pipeline: from fetch to commit, excepting execute. Processing minigraphs as handles at almost all stages maximizes amplification while minimizing the number of changes required to the pipeline; only the instruction cache fill, schedule, and execute stages are made mini-graph aware.

Figure 1.7: Mini-Graph Fusion.

#### **1.3.3** Supporting Limited Latency Reduction

There are actually two approaches to instruction fusion. Mini-graphs are an amplification-oriented form of fusion; they focus on amortizing interface coordination. Most forms of fusion are actually latency-oriented, focusing on reducing the execution latency of common operation chains (or more generally graphs). Latency-oriented fusion can actually shorten the height of a program's dataflow graph.

Mini-graphs can incorporate the benefits of execution latency reduction by supporting the pair-wise collapsing of ALU pipeline stages. To illustrate, if two ALU pipeline stages could execute in a single cycle, cycles 5 and 6 of Figure 1.7 would collapse into a single cycle, as was achieved for macro fusion in Figure 1.3b. Furthermore, mini-graph processing can apply latency reduction to arbitrary pairs of arithmetic/logical operations, not just the test/compare-branch pairs of macro fusion.

#### 1.3.4 Minimizing Design Impact

Although aggressive with respect to amplification, mini-graph processing is designed to be conservative in terms of hardware and software design changes. To minimize pipeline modifications, mini-graphs are constrained to have the interfaces of RISC singleton instructions. These constraints are detected statically by a software tool that identifies legal mini-graphs. Most importantly, mini-graphs are constrained to be atomic, have at most three register inputs and one register output, and to perform at most one memory operation. This last constraint preserves instruction-granularity handling of memory operations, including memory related exception handling. Existing mechanisms like branch prediction, memory disambiguation, and load-store forwarding remain unchanged in the presence of mini-graphs; mechanisms that use instruction PC (e.g., branch prediction) can use handle PC instead. Annotated outlining makes a minor ISA extension that requires only one or two new opcodes; annotated outlining naturally supports functional compatibility across different minigraph and non-mini-graph processors. Because the binary contains the original instruction sequences, these can be retrieved to aid in debugging or to handle rare and difficult exceptions. Mini-graphs do not need to be explicitly virtualized and require OS support only if disabling mini-graphs is desired.

#### 1.3.5 Providing Robust Performance

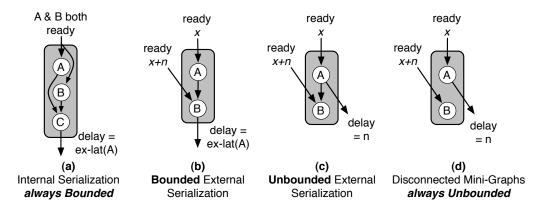

Fused micro-ops occupy a single issue queue slot, but they issue separately. Minigraph constituents, on the other hand, are issued atomically. The benefit is obvious. Whereas micro-op fusion amplifies only the issue queue, mini-graph processing amplifies both the issue queue and issue bandwidth. There is, however, a cost. Requiring mini-graph constituents to issue atomically creates the possibility of *serialization*, the introduction of new program dependences. Because a mini-graph cannot issue until all of its external inputs are ready, data dependences exist between all producers of mini-graph inputs and the first operation in the mini-graph.

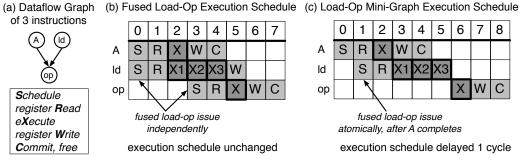

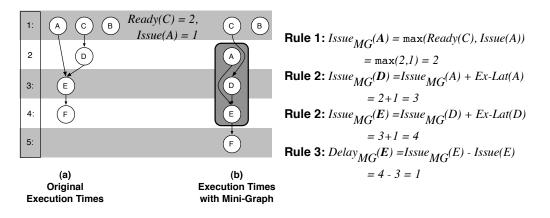

Figure 1.8: Serialization Effects in Mini-Graphs

Figure 1.8 shows an example with three instructions A, 1d, and op, shown in Figure 1.8a. Figure 1.8b shows the execution schedule of these three instructions, with the load-op pair fused by micro-op fusion. Figure 1.8c shows the execution schedule of the same three instructions, with the load-op pair as a mini-graph. (The pipelines begin with the schedule stage for simplicity.) Whereas the micro-op pair are scheduled independently, allowing the load to execute in parallel with instruction A, the mini-graph is scheduled atomically, requiring the load to wait for instruction A to complete before it can be executed. The result is a 1 cycle delay in the execution schedule. The load waits for a value that it does not actually depend on; this delays not only the load but also the op that follows it.

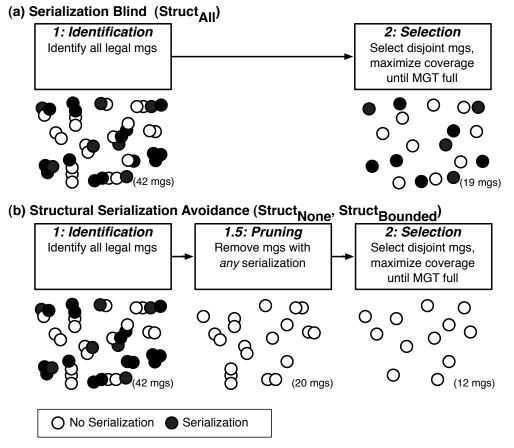

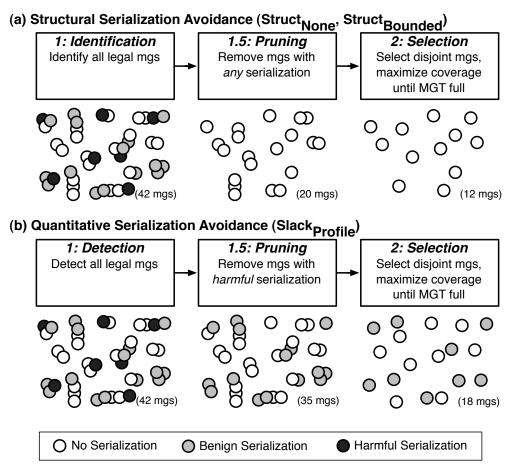

Small increases in execution latency caused by serialization can result in overall program slowdowns. This dissertation provides an extensive examination of the problem of serialization and serialization-aware fusion in the context of mini-graphs. Selecting mini-graphs aggressively (*i.e.*, ignoring serialization) maximizes mini-graph coverage but the associated performance loss for many programs outweighs the benefits of amplification in the first place. Selecting mini-graphs conservatively (*i.e.*, prohibiting serialization by static analysis) avoids performance loss but produces little amplification. Most instances of serialization are benign (unmanifested or unimportant). This dissertation develops three serialization-aware selection schemes that identify and reject mini-graphs with *harmful serialization only*.

### 1.4 Results Summary

Mini-graph processing is a low-cost, low-area, low-design-impact substitute for superscalar width and window capacity. Current processors are converging upon the 4-wide issue core as a performance-efficiency design sweet-spot [106]. Given the goal of designing low-power, low-area cores that still maintain high single-thread performance, the question is whether the coverage offered by mini-graphs is sufficient to achieve the performance of the 4-wide core with a mini-graph-enabled 3-wide core. Answering this question requires a study of both the coverage and performance of mini-graph processing. Specifically, a performance comparison is made between a 3-wide mini-graph processor and a 4-wide non-mini-graph processor. Figure 1.9 details both the 3-wide and 4-wide configurations, and the mini-graph support. Both the 3-wide and the 4-wide configurations are tuned to the performance "knee" for both issue queue entries (20 vs. 30) and physical registers (120 vs. 144).

| <b></b>                                                                                                                                                                                                                                                              | i                                                                                                                                                                                                                                                                      |                  |                                         |                                          |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|------------------------------------------|--|

| Parameter                                                                                                                                                                                                                                                            | Configuration                                                                                                                                                                                                                                                          |                  |                                         |                                          |  |

| Memory System                                                                                                                                                                                                                                                        | 32KB, 2-way/4-way associative 3-cycle access data/instruction caches. 64-entry, 4-way associative instruction and data TLBs. 1MB, 4-way associative, 12-cycle access on-chip L2. Infinite, 200 cycle-access main memory. 16B memory bus clocked at 1/4 core frequency. |                  |                                         |                                          |  |

| Branch<br>Prediction                                                                                                                                                                                                                                                 | 24Kb hybrid bimodal/gShare branch direction predictor, 2K-entry, 4-way associative BTB, 32-entry RAS                                                                                                                                                                   |                  |                                         |                                          |  |

| Pipeline                                                                                                                                                                                                                                                             | 16 stages: 1 predict, 3 instruction cache, 1 decode, 2 rename, 1 schedule, 2 register read, 1 execute, 1 register write, 3 replay, 1 commit                                                                                                                            |                  |                                         |                                          |  |

| Instruction<br>Window                                                                                                                                                                                                                                                | bads are scheduled aggressively using<br>In the pipeline. Cache miss replays are                                                                                                                                                                                       |                  |                                         |                                          |  |

| Processor Width                                                                                                                                                                                                                                                      | fetch/issue/commit<br>width                                                                                                                                                                                                                                            | issue queue size | register file<br>size                   | Scheulder Issues per cycle:<br>(maximum) |  |

| 4-wide                                                                                                                                                                                                                                                               | 4-wide                                                                                                                                                                                                                                                                 | 30 entry         | 144 pregs                               | 4 int / 1fp / 2 load / 1 store           |  |

| 3-wide                                                                                                                                                                                                                                                               | 3-wide                                                                                                                                                                                                                                                                 | 20 entry         | 120 pregs                               | 3 int / 1fp / 2 load / 1 store           |  |

| Mini-Graphs     Maximum 5 instructions, 7 cycles, 3 integer constituents, 1 load or store, 1 terr<br>instruction. Scheduler issues at most 2 mini-graphs per cycle, at most 1 integer min<br>MGT SIZE: 512-entries, 7 banks. 2 3-stage ALU Pipelines replace standar |                                                                                                                                                                                                                                                                        |                  | at most 1 integer mini-graph per cycle. |                                          |  |

Figure 1.9: Simulation Configuration for 3-wide and 4-wide processors.

Methodology. This dissertation studies mini-graphs in the context of userlevel code, the Alpha AXP ISA, and processors with unified physical register files [36, 43, 110]. Mini-graph processing in the context of non-Alpha ISAs is discussed in Section 2.7; mini-graphs in the context of alternative microarchitectures is discussed in Section 2.8. Mini-graph binaries were created from 78 Alpha binaries across four benchmark suites: SPECint2000 (SPEC), MediaBench [60], CommBench [108], and MiBench [42]. The original binaries were compiled for the Alpha EV6 using the Digital OSF compiler with optimization flags -O3. All benchmarks were run to completion: SPEC programs on their training inputs at 2% periodic sampling with warm-up; all other benchmarks on their largest available inputs with no sampling. Not all of these suites (*e.g.*, MiBench) actually target dynamically scheduled superscalar processors. They are included to show the applicability of mini-graphs to different kinds of codes.

The timing simulation infrastructure uses the SimpleScalar 3.0 Alpha AXP instruction definition and system call modules to model a dynamically scheduled superscalar processor. The simulator uses cycle level simulation to generate IPCs, but does not explicitly account for circuit delay, frequency, or power. Performance results are quantitative insofar as the cycles required to execute each instruction are faithfully modeled by each pipeline stage. The performance results do not, however, account for possible frequency changes. Power and frequency results are strictly qualitative; particular processor configurations are determined to consume more or less power based on relative capacities and bandwidths of particular critical on-ship structures.

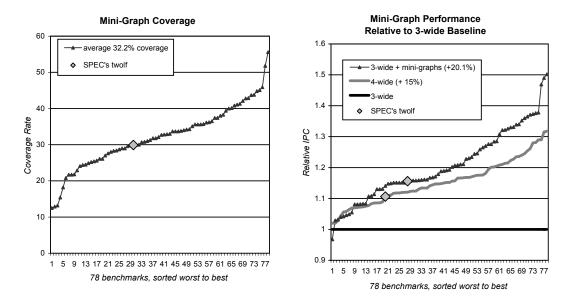

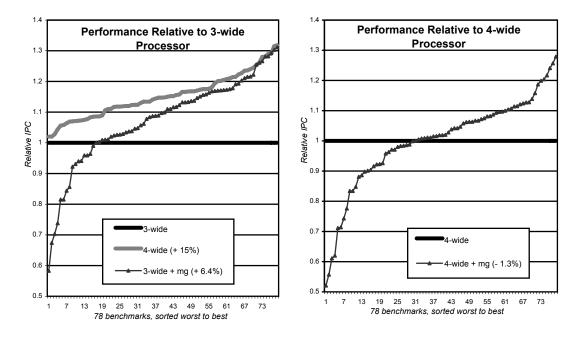

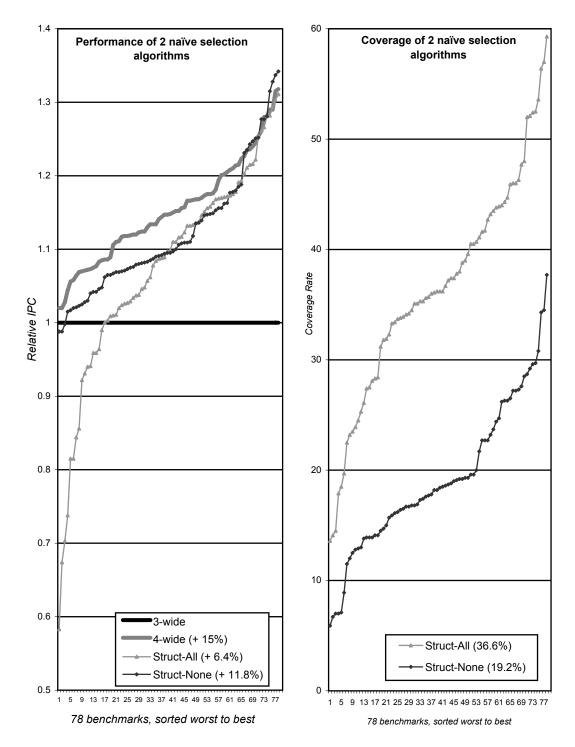

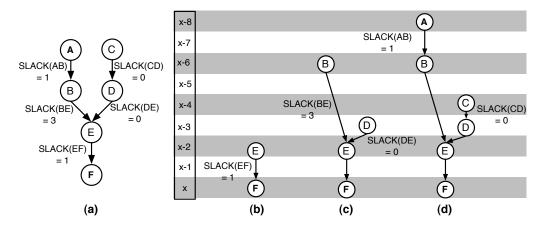

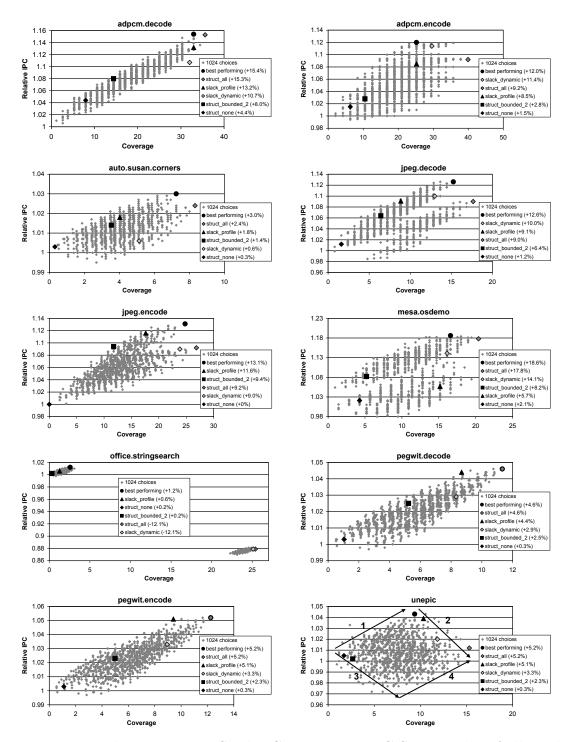

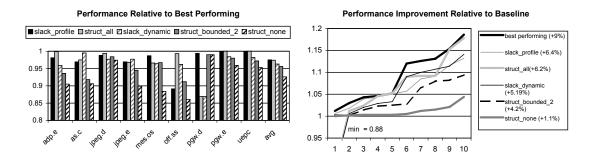

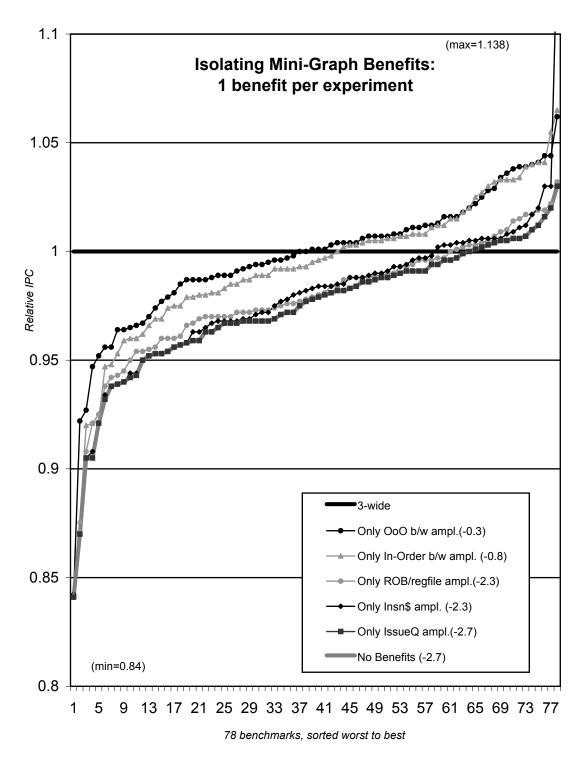

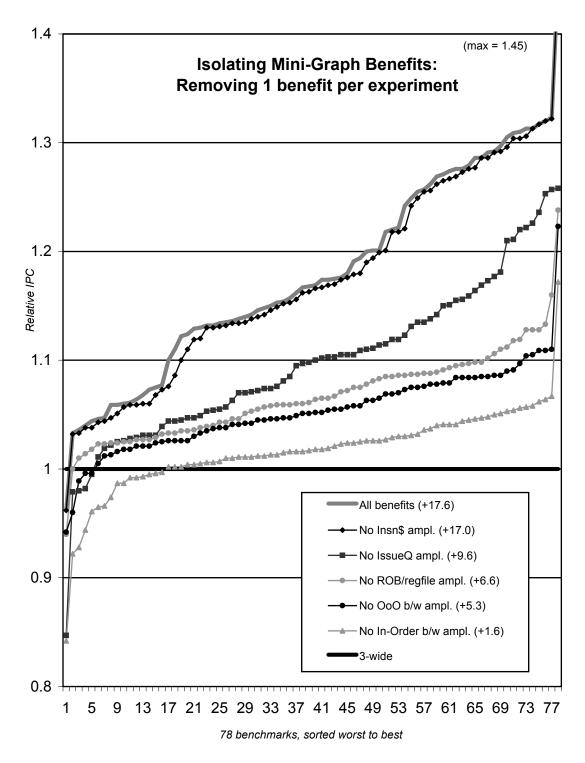

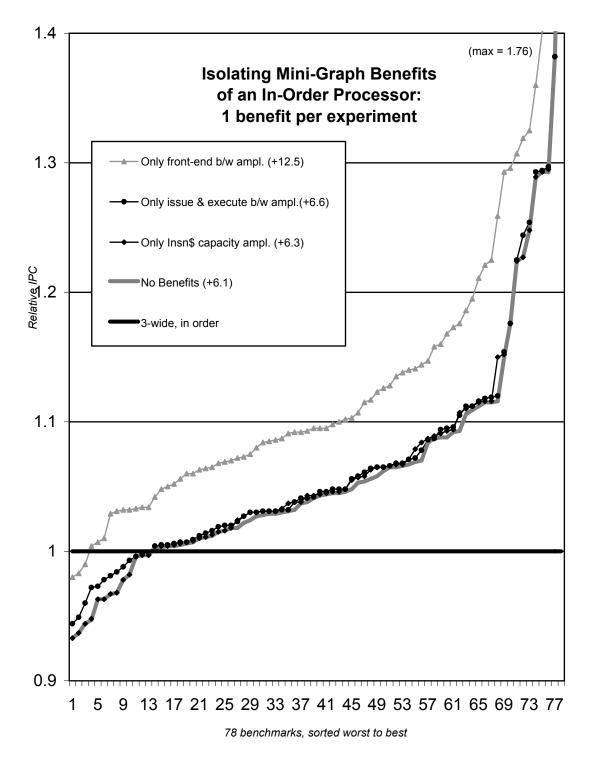

This section presents results for both coverage and performance, as shown in Figure 1.10. Much of the data in this dissertation is displayed using S-curve graphs. Each line represents an experiment in which all programs are sorted from worst to best; hashes mark each program. In the same graph, each experiment is sorted independently so that the same horizontal point may correspond to different programs in different experiments. To illustrate, the large diamond in each graph shows the results for the SPEC benchmark *twolf*. On a 4-wide processor, *twolf* sees a

10.6% performance improvement over a 3-wide processor. On a mini-graph processor, *twolf* has a 30% coverage rate and sees a 15.6% performance improvement over a 3-wide processor. S-curves effectively display trends and medians for large numbers of benchmarks and prevent outliers from hiding in averages.

Figure 1.10: Mini-Graph Coverage and Performance. Left: Coverage of mini-graphs across 78 benchmarks. Right: Comparison of 3-wide mini-graph processor and 4-wide processor. Relative to a 3-wide processor. Mini-graphs in this graph are chosen using the best performing serialization-aware selection algorithm,  $Slack_{Profile}$  (see Chapter 3).

**Coverage.** Coverage varies based on the mini-graph definition (how many and what kinds of instructions can be incorporated into mini-graphs). The graph on the left of Figure 1.10 shows coverage rates for mini-graphs with as many as three integer operations and at most five total constituents.

Coverage across 78 benchmarks is approximately 32%. Structures and pipeline stages which process handles are effectively one third larger. This is achieved without physically increasing capacity or bandwidths. The next graph compares the performance of a mini-graph processor with a non-mini-graph processor that *is* physically larger by this same (one-third) amount.

**Performance.** The performance effects of mini-graph processing can be observed by comparing a less-provisioned (*i.e.*, 3-wide) processor with mini-graph capabilities to a more-provisioned (*i.e.*, 4-wide) processor without mini-graphs. This comparison is shown in the graph on the right of Figure 1.10. Performance is relative to a 3-wide, non-mini-graph baseline. The 3-wide mini-graph processor outperforms the 4-wide non-mini-graph processor in almost every case; the former shows a 20% performance improvement over a baseline 3-wide machine, the latter only a 15% improvement.

The mini-graphs in this experiment are selected using the best performing serialization-aware selection algorithm,  $Slack_{Profile}$ , which is introduced in Chapter 3. It is important to note that without this algorithm, the performance improvement is both half that of the 4-wide machine and significantly less robust; approximately 25% of benchmarks would see a performance *loss* over the 3-wide baseline.

A 3-wide mini-graph processor not only matches the performance of a 4-wide non-mini-graph processor, but it does so with smaller superscalar structures and bandwidths. (These data do not assume latency reduction in the ALU Pipeline; each operation executes in a full cycle.) The main hardware cost of mini-graph processing is the MGT, whose capacity, bandwidth, and support for banking (as explained in the next chapter) makes it inexpensive, relative to the cost of adding entries and ports to existing structures (*e.g.*, register file, issue queue) or increasing the bandwidth of the entire processor by one-third. Mini-graph processing can, in fact, act as a robust, less expensive replacement for some of the expensive bookkeeping machinery of a high-performance processor.

### 1.5 Contributions

This dissertation makes several contributions. Specifically, it:

• Introduces the concept of mini-graphs processing, a form of instruction fusion

that focuses on pipeline capacity and bandwidth amplification.

- Describes a novel microarchitecture for processing mini-graphs that requires only small modifications over existing superscalar designs. The key components of the implementation include the Mini-Graph Table, ALU Pipelines, and an outlining-based ISA extension facility.

- Presents the first extensive discussion of the problem of serialization. Introduces both external and internal serialization as well as the conditions under which each can affect performance. Develops and evaluates several serialization-aware mini-graph pruning algorithms. Compares these algorithms to each other as well as to naive and exhaustive methods.

- Presents a simulation-driven performance evaluation of the complete minigraph system, showing that the addition of mini-graph processing allows a dynamically scheduled 3-wide superscalar processor to match the IPC of a 4-wide superscalar machine.

Previously published work on mini-graph processing include a 2004 publication in the 37th International Symposium on Microarchitecture [12], a 2006 publication in the 39th International Symposium on Microarchitecture [14], and a 2006 technical report from the University of Pennsylvania [13]. The first publication introduces the concept of mini-graph processing including the MGT and ALU Pipelines, discusses the coverage across different possible mini-graph definitions, introduces the concept of serialization, and shows initial performance benefits for various mini-graph processor configurations. The second publication briefly discusses the mini-graph encoding scheme but focuses primarily on serialization. It introduces several pruning algorithms designed to overcome the performance penalties caused by serialization. The technical report best describes the outlining-based ISA extension facility used to create a mini-graph binary; this encoding differs from the DISE-based encoding [26] of the 2004 publication. These three publications correspond to Chapter 2, Chapter 3, and Section 2.2, respectively. That said, this dissertation—particulary Chapter 2—presents a more extensive discussion of mini-graph processing than is present in any of the publications.

This dissertation is organized as follows. Chapter 2 describes the architecture and microarchitecture of a mini-graph processor, detailing how mini-graphs are encoded in a program binary and how they are processed as the program executes. Chapter 3 discusses how mini-graphs are identified statically and how they can be chosen to maximize both resource amplification and performance. This section focuses on minimizing performance penalties associated with serialization. Chapter 4 presents a simulation-based timing evaluation of mini-graph processing. Chapters 5 and 6 discuss related works and conclusions, respectively.

# Chapter 2

# Mini-Graph Architecture

Mini-graph processing is a unique form of instruction fusion that targets bandwidth and capacity amplification throughout the entire pipeline, from fetch to commit. By performing certain actions once per aggregate instead of on a per-instruction basis, structure bandwidth and capacity is allocated to other instructions, creating an amplification effect. This wholesale amplification enables either improved IPC throughput at a fixed resource point or, alternatively, fixed (or better) IPC with fewer resources.

This dissertation studies mini-graphs in the context of user-level code written in the Alpha ISA. The assumed microarchitecture is similar to an unclustered Alpha 21264, specifically one that implements register renaming using a unified physical register file (as opposed to an architectural register file and a value-based ROB), that has a unified scheduler for integer and memory operations and a separate scheduler for floating-point operations.

Mini-graphs are designed to maximize amplification both from a dynamic instruction standpoint and from the standpoint of number of structures and pipeline stages amplified. At the same time, they are designed to minimize impact on the microarchitecture—specifically the number of structures that are made mini-graph aware—the ISA, and the operating system. In other words, mini-graphs maximize their amplification impact while minimizing their implementation costs.

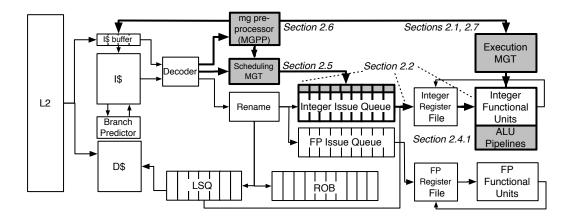

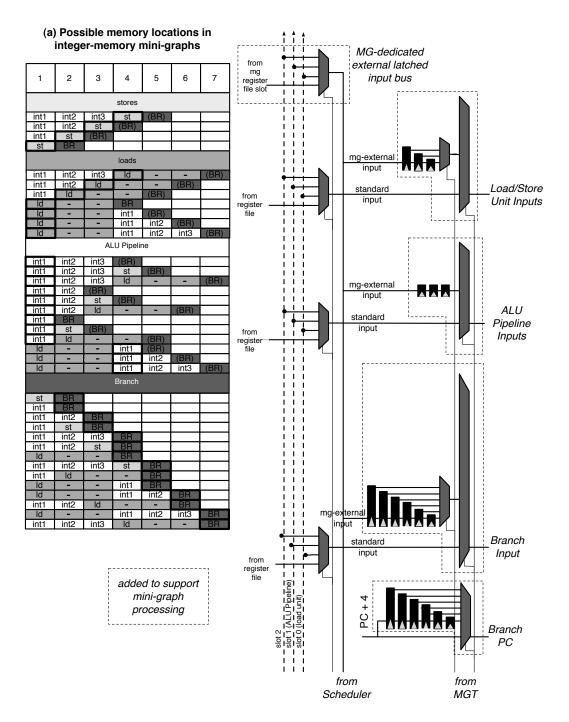

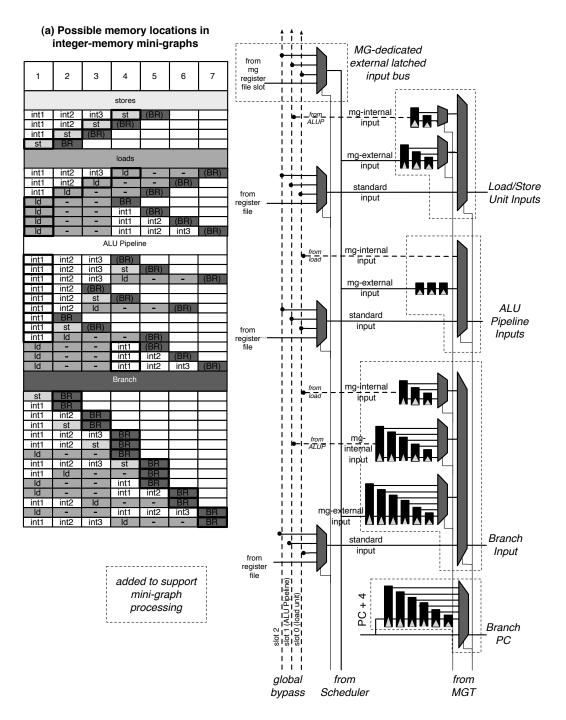

This chapter begins with a brief overview of the structural changes required to support mini-graph processing. Figure 2.1 depicts a high level diagram of a basic out-of-order processor. The unshaded parts of the figure show the structures that are unmodified in a mini-graph processor: the instruction and data caches, the branch predictor, the floating-point units, as well as more complicated entities such as the decoder, the load/store queue, register renaming, as well as the register and memory schedulers. The shaded parts of the figure show the structures that are added in order to support mini-graph processing: the Mini-Graph Table, the Mini-Graph Pre-Processor, and ALU Pipelines. Structures outlined in bold (issue queue, functional units) are modified from the basic processor in order to support minigraph processing. The bold lines show new or modified paths between the structures themselves. Each shaded structure or bold line is labeled with the section number in which this support is discussed.

Figure 2.1: Architectural Changes

Mini-Graph Table (MGT). Mini-graph templates reside in an on-chip structure called the *Mini-Graph Table* (MGT). The MGT is an on-chip cache for minigraph templates—each entry holds the resource needs and definition of one minigraph template, indexed by MGID. Mini-graph templates are entered into the MGT on a per-program basis; this allows each program to have its own unique set of templates. Mini-graph templates do not need to be shared across applications.

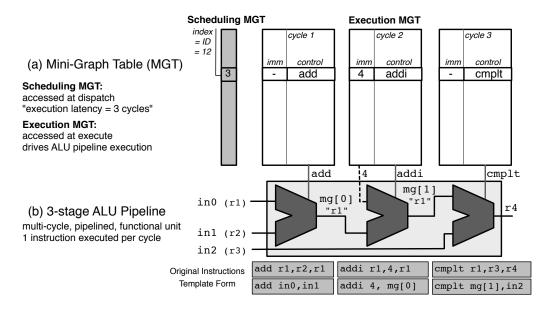

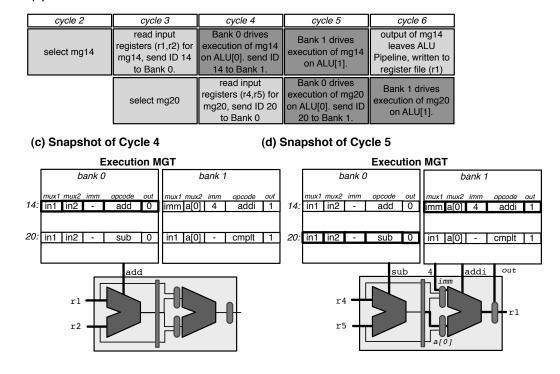

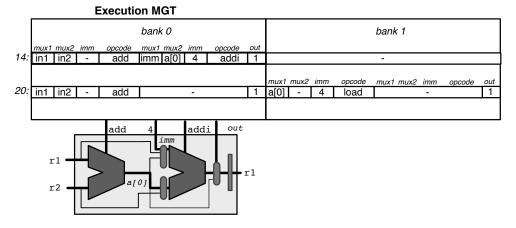

The MGT is divided into two parts: the Scheduling MGT and the Execution MGT, shown in Figure 2.2a. The *Scheduling MGT* (see Section 2.4) summarizes the resource needs of each mini-graph template. Mini-graph scheduling information is accessed at dispatch and then used by the scheduler to coordinate resource reservations. For example, the Scheduling MGT informs the scheduler that the mini-graph mg12 in Figure 2.2a has an execution latency of 3 cycles and therefore needs a correspondingly delayed reservation of a writeback port.

The *Execution MGT* holds the per-constituent template information and drives the cycle-by-cycle execution of the mini-graph's constituent operations, micro-code style. Each entry contains an opcode, an immediate, and a group of control bits. The opcode and immediates are found in the original non-mini-graph constituents. The control bits encode the dataflow of the mini-graphs, driving the input muxes to functional units and the output muxes of the ALU Pipeline (explained next).

The Execution MGT is both banked and pipelined; n banks are required to support a mini-graph with an execution latency of n cycles. Figure 2.2, for example, shows and Execution MGT where n = 3. The first bank controls the execution of the first mini-graph constituent during the first cycle of execution of the minigraph. If a mini-graph does not execute a new constituent at a particular cycle, the corresponding bank's entry remains unused. m read ports per bank support the continuous pipelining of m mini-graphs per cycle. With this configuration, the MGT is free of structural hazards. Assuming a 6-bit opcode, a 16-bit immediate, two 3-bit mux controllers (for selecting inputs), 1 bit indicating an output, and remaining bits to indicate which functional unit a constituent executes on, each MGT constituent requires 32 bits, *i.e.*, 4 bytes. A 512-entry MGT, then, requires 2KB per MGT bank. A 7-bank MGT is 14KB. The configuration of the MGT is one of the primary levers that trades minigraph coverage with mini-graph implementation costs. Adding entries to the MGT either supports fewer MGT misses and improves performance or supports more minigraph templates and consequently increases coverage. Adding banks to the MGT supports longer mini-graphs and consequently increases coverage. Adding more ports to each bank supports the execution of more mini-graphs per cycle and consequently increases mini-graph throughput. However, increasing the number of MGT entries, banks, or ports all increases the cost of mini-graph processing by increasing the size and power consumption of the MGT itself.

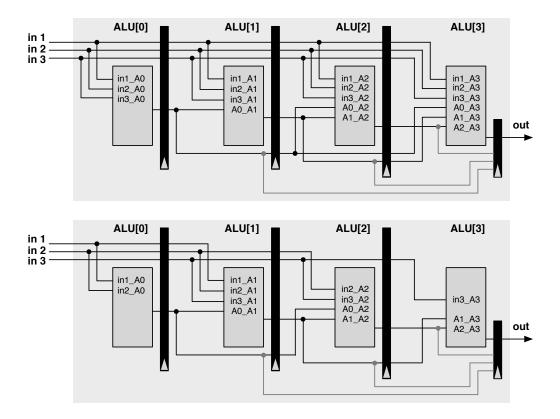

**ALU Pipelines.** Execution is the only pipeline stage not amplified by minigraph processing. To prevent execution from becoming a new bandwidth bottleneck, a mini-graph processor replaces some of its ALUs with *ALU Pipelines*: single-entry, single-exit chains of ALUs with forward-only interior operand networks (see Figure 2.2b). An ALU Pipeline is essentially a multi-cycle functional unit (like a multiplier) on which integer mini-graphs execute. ALU Pipelines add ALU execution bandwidth without requiring matching increases in register file and bypass bandwidths.

Like the MGT, the configuration of the ALU Pipeline is another lever used to trade coverage with implementation costs. ALU Pipelines with more stages support longer mini-graphs that achieve more coverage. Adding an ALU Pipeline stage incurs the same area and power costs of adding a standard ALU, but none of the bypass complexity of actually increasing the execution width of the processor. The ALU Pipeline support also affects performance. Having multiple ALU Pipelines will not improve coverage, but it will improve throughput. Finally, the cost of an interlockcollapsing ALU Pipeline comes with the benefit of reducing the execution latency of the mini-graph and potentially shortening the height of a program's dataflow.

MGT and ALU Pipeline example. Figure 2.2 shows an MGT that supports integer mini-graphs of up to three instructions long connected to its corresponding ALU Pipeline (of 3 ALUs). The MGT is indexed by the MGID field of the mini-graph

Figure 2.2: Mini-Graph Table and ALU Pipeline.

handle (in this case, 12). At dispatch, the Scheduling MGT is accessed to determine the execution latency of the mini-graph; this information extends the scheduler itself and is used in the next cycle. The Execution MGT contains the necessary immediate inputs, opcodes, and input selectors (not shown) in order to drive the execution of the mini-graph on the ALU Pipeline. For simplicity, the ALU Pipeline in Figure 2.2b shows only paths that are used by this particular mini-graph. Scheduling and executing integer-memory mini-graphs is slightly more complex and is discussed in Section 2.3.

Integer-memory mini-graphs. The final lever used to trade coverage and cost is the mini-graph definition itself. This dissertation focuses on two types of minigraphs: *integer mini-graphs*, which contain only single-cycle ALU operations and *integer-memory mini-graphs* which can also contain loads, stores, and control transfers. Because they behave almost identically to standard multi-cycle instructions, integer mini-graphs require little support. Unfortunately, they also have an average 14% coverage rate—not enough to compete with an additional superscalar slot. Because they incorporate more types of instructions, integer-memory mini-graphs achieve coverage rates of approximately 35%. This amplification benefit comes at an implementation cost. Three-cycle loads make inefficient use of the MGT which is banked by cycle, not instructions. Integer-memory mini-graphs also fundamentally require coordination of multiple functional units; ALU Pipelines cannot easily be extended to support memory or control instructions. This coordination impacts both the scheduler and the bypass network, although careful design can minimize this impact.

The mini-graphs supported in this dissertation is as follows. Integer mini-graphs (or the integer constituents of an integer-memory mini-graph) are executed on 3stage ALU Pipelines. Integer-memory mini-graphs may contain up to three consecutive integer operations, a maximum of one loads or stores, and a single control instruction—up to 7 cycles of execution. Load latency is assumed to be three cycles. Two mini-graphs may issue per cycle, but only one of these may be an integermemory mini-graph.

This chapter reviews the basics of mini-graphs and mini-graph processing with these design goals in mind. It describes all the necessary components of a minigraph architecture. Section 2.1 details mini-graph criteria. Section 2.2 explains how mini-graphs, once identified in a program, are encoded in a program binary. Section 2.3 introduces the microarchitectural support necessary to execute minigraphs. Section 2.4 describes mini-graph scheduling. Section 2.5 discusses the Mini-Graph Pre-Processor whereas Section 2.6 provides further details about the MGT. Additional attention is needed in order to select mini-graphs that guarantee robust performance. Chapter 3 discusses selection for robustness and high performance.

## 2.1 Mini-Graph Criteria

Mini-graphs are aggregates with the external appearance of singleton RISC instructions. The RISC singleton interface makes mini-graphs appropriate for superscalar processors which rely on simple book-keeping units to implement register renaming and dynamic scheduling. Mini-graph handles are designed to look and behave as any other singleton instruction and require as little special handling as possible.

Mini-graphs are first and foremost *atomic* – constituent operations are executed on an all-or-none basis, and internal mini-graph state is unobservable by external instructions. Atomicity is the key to amplification; pipeline stages and superscalar structures that manipulate instructions do so at a mini-graph (not constituent) granularity. Atomicity also allows register communication that is "interior" to a mini-graph to take place without actual registers. Provably transient values live only in the bypass network. This amplifies both the capacity of the physical register file as well as the bandwidths of all stages that manipulate either register names (rename/register-allocate and commit/register-free) or values (register read and write).

Atomicity constrains mini-graphs to reside within atomic instruction sequences of a program. In this dissertation, atomicity is enforced by mining mini-graphs from basic blocks. Mining mini-graphs from larger atomic code sequences, either statically (*e.g.*, predicated hyperblocks or transactional code sequences within a software rePLay framework [71]) or dynamically (*e.g.*, from rePLay frames [78]) is possible but is outside the scope of this dissertation

Beyond the fundamental constraint of atomicity, mini-graph criteria are largely a set of tradeoffs—finding the sweet spot between the benefit of coverage and a cost, such as ease of implementation. Mini-graphs are conservatively defined so as to minimize the number of pipeline stages that are explicitly mini-graph aware, changes to the ISA, and the involvement of the operating system.

This section explores the implementation costs and coverage benefits associated

with mini-graph criteria such as mini-graph instruction formats, maximum cycle length, and which instruction types to include. The stricter the mini-graph criteria, the fewer architectural changes are required to process mini-graphs, but the less coverage these mini-graphs offer. Conversely, relaxing mini-graph constraints improves coverage but also increases the cost of implementation.

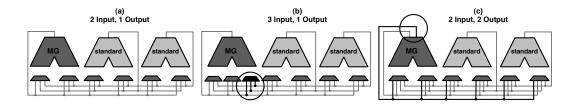

Handle formats. Mini-graph handles can be represented in a program binary using a common 32-bit instruction format—shared by Alpha, MIPS, and SPARC instructions—that assumes opcodes require 6 bits and register specifiers require 5 bits each. The remaining n bits belong to the MGID which can express  $2^n$  mini-graph templates. Three possible 32-bit formats are shown in Table 2.1. With 32 bits total, a mini-graph can have either 2 register inputs and 1 register output, 3 register inputs and 1 register output, or 2 register inputs and 2 register outputs. The choice of formats is the first of many decisions that weighs coverage benefits with implementation cost.

|   | 31 - 26 | 25 - 21 | 20 - 16 | 15 - 11  | 10 - 6   | 5 - 0 | templates |

|---|---------|---------|---------|----------|----------|-------|-----------|

| А | opcode  | input 1 | input 2 | output   | MGI      | D     | 2048      |

| В | opcode  | input 1 | input 2 | input 3  | output   | MGID  | 64        |

| С | opcode  | input 1 | input 2 | output 1 | output 2 | MGID  | 64        |