#### CS412/413

Introduction to Compilers Radu Rugina

Lecture 28: Instruction Selection 4 Apr 03

### **Instruction Selection**

- Different sets of instructions in low-level IR and in the target machine

- Instruction selection = translate low-level IR to assembly instructions on the target machine

- Straightforward solution: translate each low-level IR instruction to a sequence of machine instructions

- Example:

```

x = y + z

mov y, r1

mov z, r2

add r2, r1

mov r1, x

```

CS 412/413 Spring 2003

Introduction to Compilers

#### **Instruction Selection**

- Problem: straightforward translation is inefficient

- One machine instruction may perform the computation in multiple low-level IR instructions

- Consider a machine with includes the following instructions:

$\begin{array}{lll} \text{add } r2, \, r1 & & r1 \leftarrow r1 + r2 \\ \text{mulc } c, \, r1 & & r1 \leftarrow r1 * c \\ \text{load } r2, \, r1 & & r1 \leftarrow * r2 \\ \text{store } r2, \, r1 & & * r1 \leftarrow r2 \\ \text{movem } r2, \, r1 & & * r1 \leftarrow * r2 \\ \text{movex } r3, \, r2, \, r1 & & * r1 \leftarrow * (r2 + r3) \\ \end{array}$

CS 412/413 Spring 2003

Introduction to Compilers

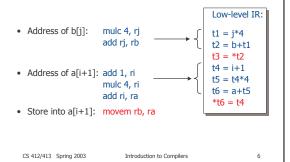

#### Example

• Consider the computation:

a[i+1] = b[j]

CS 412/413 Spring 2003

Assume a,b, i, j are global variables register ra holds address of a register rb holds address of b register ri holds value of i register rj holds value of j

Introduction to Compilers

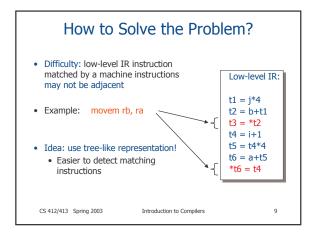

Low-level IR:

t1 = j\*4

t3 = \*t2

t4 = i+1

t5 = t4\*4

t6 = a+t5

\*t6 = t4

t2 = b+t1

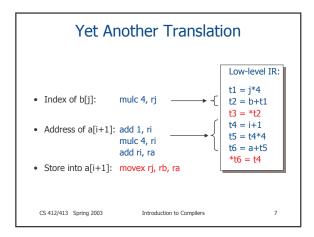

#### **Possible Translation**

```

Low-level IR:

• Address of b[j]:

mulc 4, rj

t1 = j*4

add rj, rb

t2 = b+t1

t3 = *t2

Load value b[j]:

load rb, r1

t4 = i+1

• Address of a[i+1]: add 1, ri

t5 = t4*4

mulc 4, ri

t6 = a + t5

add ri, ra

*t6 = t4

• Store into a[i+1]: store r1, ra

```

CS 412/413 Spring 2003

Introduction to Compilers

#### **Another Translation**

#### **Issue: Instruction Costs** • Different machine instructions have different costs - Time cost: how fast instructions are executed - Space cost: how much space instructions take • Example: cost = number of cycles add r2, r1 mulc c, r1 load r2, r1 cost=3 store r2, r1 cost=3 movem r2, r1 cost=4 movex r3, r2, r1 cost=5 · Goal: find translation with smallest cost CS 412/413 Spring 2003 Introduction to Compilers

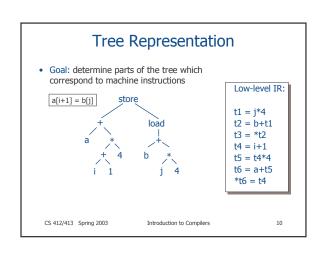

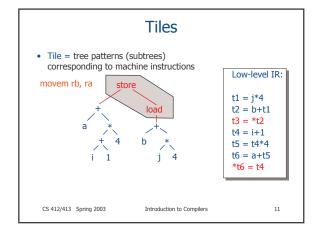

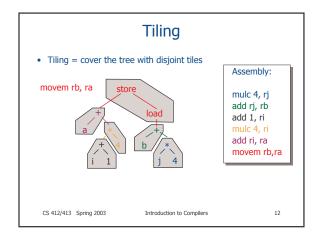

## **Directed Acyclic Graphs**

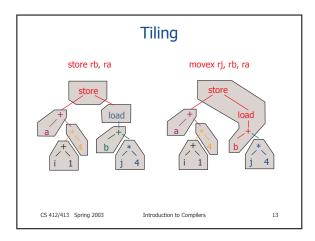

- Tree representation: appropriate for instruction selection

- Tiles = subtrees → machine instructions

- DAG = more general structure for representing instructions

- Common sub-expressions represented by the same node

- Tile the expression DAG

- Example:

- t = y+1 y = z\*t t = t+1 z = t\*y

CS 412/413 Spring 2003

stroduction to Compilers

#### **Big Picture**

- What the compiler has to do:

- 1. Translate low-level IR code into DAG representation

- 2. Then find a good tiling of the DAG

- Maximal munch algorithm

- Dynamic programming algorithm

CS 412/413 Spring 2003

Introduction to Compilers

15

17

#### **DAG Construction**

- Input: a sequence of low IR instructions in a basic block

- Output: an expression DAG for the block

- Idea:

- Label each DAG node with variable which holds that value

- Build DAG bottom-up

- Problem: a variable may have multiple values in a block

- Solution: use different variable indices for different values of the variable: t<sub>0</sub>, t<sub>1</sub>, t<sub>2</sub>, etc.

CS 412/413 Spring 2003

Introduction to Compilers

## Algorithm

index[v] = 0 for each variable v

For each instruction I (in the order they appear) For each v that I directly uses, with n=index[v]

if node  $v_n$  doesn't exist

create node  $v_n$  , with label  $v_n$

Create expression node for instruction I, with children

$\{ v_n \mid v \in use[I] \}$

For each  $v \in def[I]$

index[v] = index[v] + 1

If I is of the form x = ... and n = index[x] label the new node with  $x_n$

CS 412/413 Spring 2003

Introduction to Compilers

#### **Issues**

- Function/method calls

- May update global variables or object fields

- def[I] = set of globals/fields

- Store instructions

- May update any variable

- If stack addresses are not taken (e.g. Java),def[I] = set of heap objects

CS 412/413 Spring 2003

Introduction to Compilers

18

16

#### Local Variables in DAG

- · Use stack pointers to access local variables

- Example: x = y+1

CS 412/413 Spring 2003

Introduction to Compiler

#### **Next: DAG Tiling**

- · Goal: find a good covering of DAG with tiles

- Problem: need to know what variables are in registers

- Assume abstract assembly:

- Machine with infinite number of registers

- Temporary variables stored in registers

- Local/global/heap variables: use memory accesses

CS 412/413 Spring 2003

Introduction to Compilers

#### **Problems**

- · Classes of registers

- Registers may have specific purposes

- Example: Pentium multiply instruction

- multiply register eax by contents of another register

- store result in eax (low 32 bits) and edx (high 32 bits)

- need extra instructions to move values into eax

- Two-address machine instructions

- Three-address low-level code

- Need multiple machine instructions for a single tile

- CISC versus RISC

- Complex instruction sets => many possible tiles and tilings

- Example: multiple addressing modes (CISC) versus load/store architectures (RISC)

CS 412/413 Spring 2003

Introduction to Compilers

## Pentium ISA

- Pentium: two-address CISC architecture

- General-purpose registers: eax, ebx, ecx, edx, esi, edi

- Stack registers: ebp, esp

- Typical instruction:

- Opcode (mov, add, sub, mul, div, jmp, etc)

- Destination and source operands

- Multiple addressing modes: source operands may be

- Immediate value: imm

- Register: reg

- Indirect address: [reg], [imm], [reg+imm],

- Indexed address: [reg+reg'], [reg+imm\*reg'],

- [reg+imm\*reg'+imm']

- Destination operands = same, except immediate values

CS 412/413 Spring 2003

Introduction to Compilers

22

#### **Example Tiling**

- Consider: t = t + i

- t = temporary variable

- i = parameter

- Need new temporary registers between tiles (unless operand node is labeled with temporary)

- Result code:

mov %ebp, t0 sub \$20, t0 mov 0(t0), t1 add t1, t

• Note: also compute i, if it is live

CS 412/413 Spring 2003

Introduction to Compilers

t t t toad (i)

23

#