# Sec 01: Logisim

# Why Logisim?

- Most real-world hardware design is done using a text-based hardware description language – VHDL, AHDL, etc.

- Schematics can be "compiled" into a text description

- Can use a simulator to test the circuit

- Other back-end tools optimize, perform layout and wire routing, floorplan, etc.

- Final spec is either downloaded onto a programmable device, or etched into silicon

- We will be using Logisim for all hardware design

- interactive, graphical schematic editor

- educational use mainly (makes it user-friendly)

## VHDL Example: Signed Adder

```

1 library ieee;

2 use ieee.std logic 1164.all;

3 use ieee.numeric std.all;

5 entity signed adder is

6 port

aclr : in std logic;

9 clk : in std logic;

10 a : in std logic vector;

11 b : in std logic vector;

q : out std logic vector

13 ):

14 end signed adder;

16 architecture signed adder arch of signed adder is

signal q s : signed(a'high+1 downto 0); -- extra bit wide

18

19 begin -- architecture

20 assert (a'length >= b'length)

21 report "Port A must be the longer vector if different sizes!"

22 severity FAILURE;

23  q <= std logic vector(q s);</pre>

25 adding proc:

26 process (aclr, clk)

begin

if (aclr = '1') then

q s <= (others => '0');

elsif rising edge(clk) then

q s <= ('0'&signed(a)) + ('0'&signed(b));

end if: -- clk'd

end process;

35 end signed adder arch:

```

# Why Logisim?

- Most real-world hardware design is done using a text-based hardware description language – VHDL, AHDL, etc.

- Schematics can be "compiled" into a text description

- Can use a simulator to test the circuit

- Other back-end tools optimize, perform layout and wire routing, floorplan, etc.

- Final spec is either downloaded onto a programmable device, or etched into silicon

- We will be using Logisim for all hardware design

- interactive, graphical schematic editor

- educational use mainly (makes it user-friendly)

### What are we going to talk about?

- Using Logisim:

- pins and subcircuits

- probes for debugging

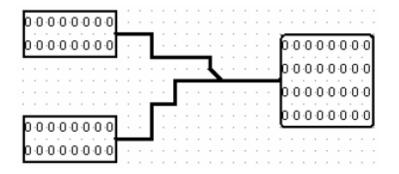

- bundles/splitters (with labels!)

- logging

- test vectors

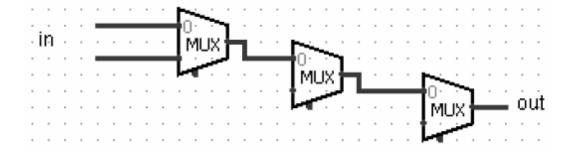

- Example Circuits: 1-bit & 32-bit 2:1 Mux

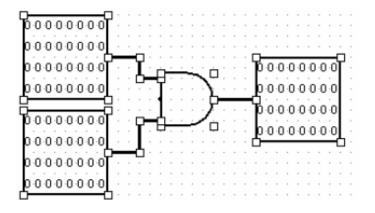

- Using Subcircuits: 2:1 Mux and Controller

- Logging & Test Vectors

- Logisim Don'ts

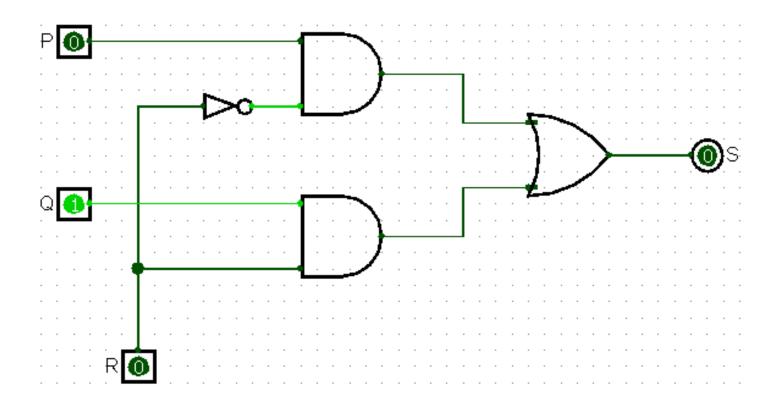

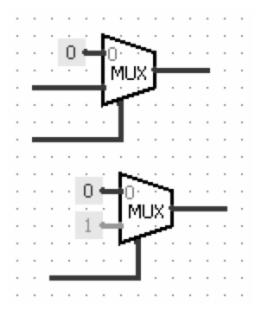

### **Example Circuit: 1-bit 2:1 Mux**

$$S = P \text{ if } R == 0$$

$S = Q \text{ if } R == 1$

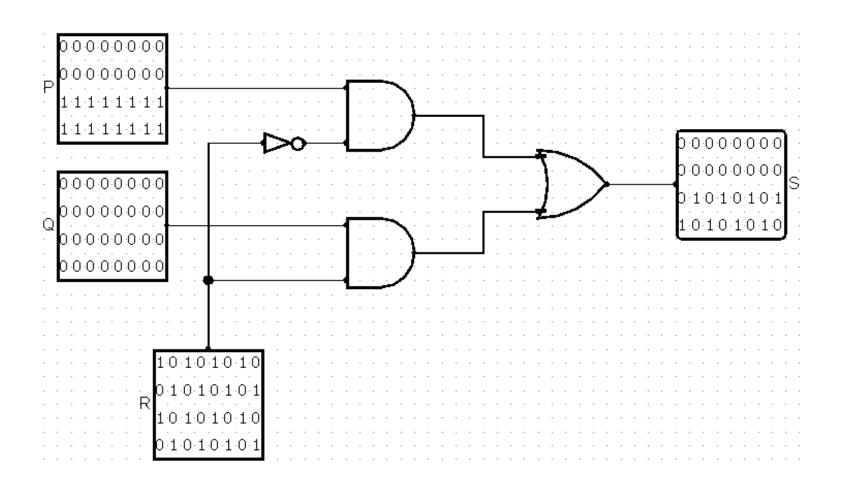

#### **Example Circuit: 32-bit 2:1 Mux**

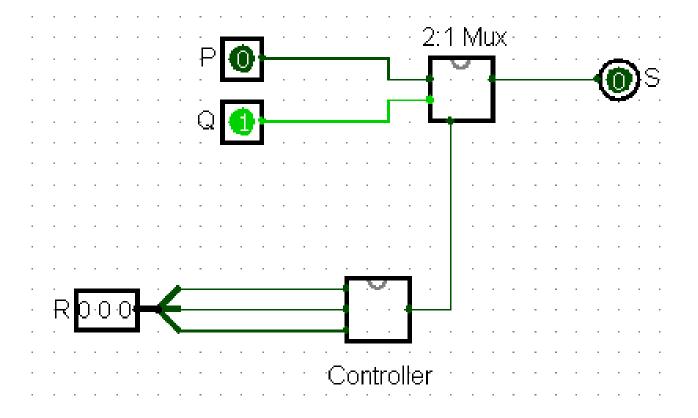

#### **Using Subcircuits: 2:1 Mux and Controller**

S = Q if R == 010

S = P otherwise

### Logging & Test Vectors

#### Log File

```

# Logisim: Log main of multiplexer1

# Mon Jan 25 11:18:42 EST 2010

P Q R S

0 0 0 0 0

0 0 0

0 1 0 0

0 1 1 1 1

1 1 1

1 0 1 1

1 1 1 1

1 1 1 1

```

#### **Test Vector Truth Table**

| Passed: 8 Failed: 0 |        |   |   |   |   |  |

|---------------------|--------|---|---|---|---|--|

|                     | status | P | Q | R | S |  |

|                     | pass   | 0 | 0 | 0 | 0 |  |

|                     | pass   | 0 | 0 | 1 | 0 |  |

|                     | pass   | 0 | 1 |   | 0 |  |

|                     | pass   | 0 | 1 | 1 | 1 |  |

|                     | pass   | 1 | 0 | 0 | 1 |  |

|                     | pass   | 1 | 0 | 1 | 0 |  |

|                     | pass   | 1 | 1 | 0 | 1 |  |

|                     | pass   | 1 | 1 | 1 | 1 |  |

|                     |        |   |   |   |   |  |

|                     |        |   |   |   |   |  |

#### No Controlled Buffers

- Leave wires floating

- Works in Logisim

- Breaks in real life

- Use a multiplexor instead

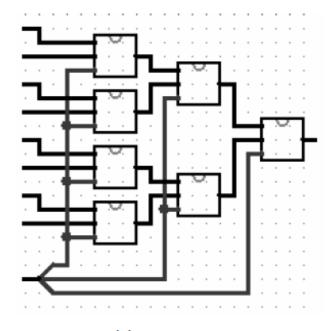

#### Don't Build Your Own

- Building your own wastes time and is confusing to grade

- Almost every component customizable

- Number of inputs

- Bit depth

Building an 8-way Mux the hard way

#### Don't Use Constants

- Constants are almost never necessary

- Exception is supplying value to extra input

- Try to optimize away before using

- Think truth tables

#### Don't Make Trivial Sub-circuits

- Try to build logical sub-circuits

- Problems

- All sub-circuits look the same

- Wastes time specifying inputs and outputs of small circuits

- Big hierarchy harder to understand

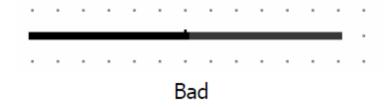

#### Don't Use Invisible Splitters

- Please...

- Its really hard to see them when we grade

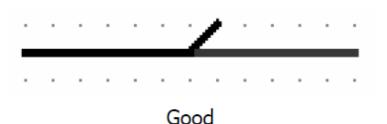

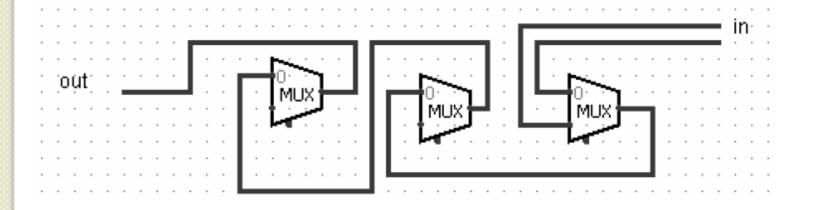

### Don't Work Right to Left

#### Some more information

- MIPS Assignments:

- 32-bit ALU

- 32-bit Processor

- 32-bit Pipelined Processor

Webpage:

http://www.cs.cornell.edu/courses/cs3410/2010sp/