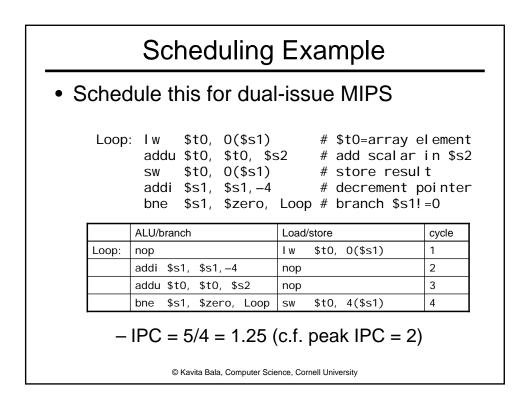

## MIPS with Static Dual Issue

- Two-issue packets

- One ALU/branch instruction

- One load/store instruction

- 64-bit aligned

- ALU/branch, then load/store

- Pad an unused instruction with nop

| Address | Instruction type | Pipeline Stages |    |    |     |     |     |    |

|---------|------------------|-----------------|----|----|-----|-----|-----|----|

| n       | ALU/branch       | IF              | ID | EX | MEM | WB  |     |    |

| n + 4   | Load/store       | IF              | ID | EX | MEM | WB  |     |    |

| n + 8   | ALU/branch       |                 | IF | ID | EX  | MEM | WB  |    |

| n + 12  | Load/store       |                 | IF | ID | EX  | MEM | WB  |    |

| n + 16  | ALU/branch       |                 |    | IF | ID  | EX  | MEM | WB |

| n + 20  | Load/store       |                 |    | IF | ID  | EX  | MEM | WB |

© Kavita Bala, Computer Science, Cornell University

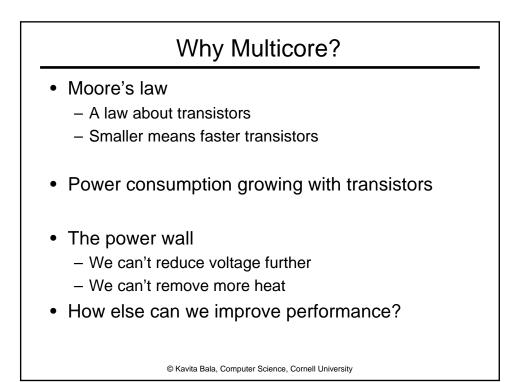

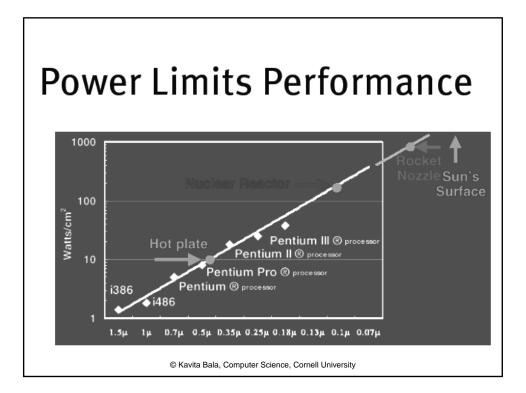

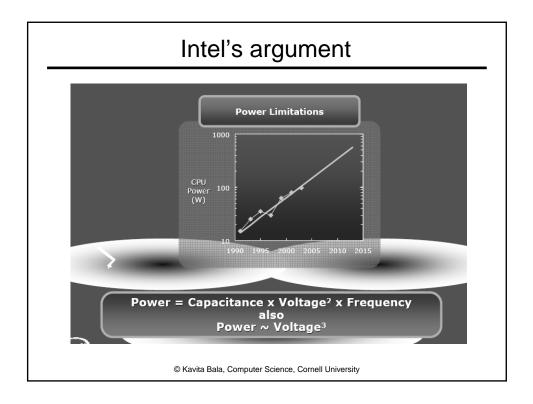

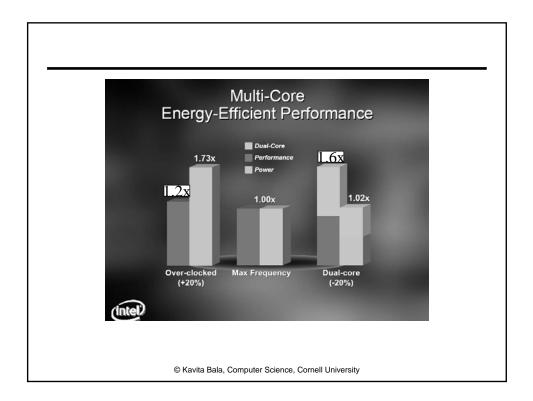

## **Power Efficiency**

• Complexity of dynamic scheduling and speculations requires power

| • | Multiple | simpler | cores may | be better |

|---|----------|---------|-----------|-----------|

|---|----------|---------|-----------|-----------|

| Microprocessor | Year | Clock Rate | Pipeline<br>Stages | Issue<br>width | Out-of-order/<br>Speculation | Cores | Power |

|----------------|------|------------|--------------------|----------------|------------------------------|-------|-------|

| i486           | 1989 | 25MHz      | 5                  | 1              | No                           | 1     | 5W    |

| Pentium        | 1993 | 66MHz      | 5                  | 2              | No                           | 1     | 10W   |

| Pentium Pro    | 1997 | 200MHz     | 10                 | 3              | Yes                          | 1     | 29W   |

| P4 Willamette  | 2001 | 2000MHz    | 22                 | 3              | Yes                          | 1     | 75W   |

| P4 Prescott    | 2004 | 3600MHz    | 31                 | 3              | Yes                          | 1     | 103W  |

| Core           | 2006 | 2930MHz    | 14                 | 4              | Yes                          | 2     | 75W   |

| UltraSparc III | 2003 | 1950MHz    | 14                 | 4              | No                           | 1     | 90W   |

| UltraSparc T1  | 2005 | 1200MHz    | 6                  | 1              | No                           | 8     | 70W   |

© Kavita Bala, Computer Science, Cornell University

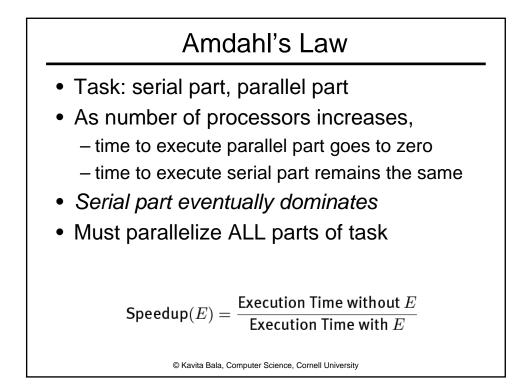

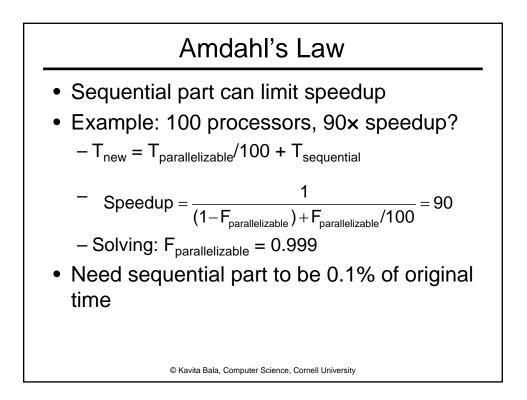

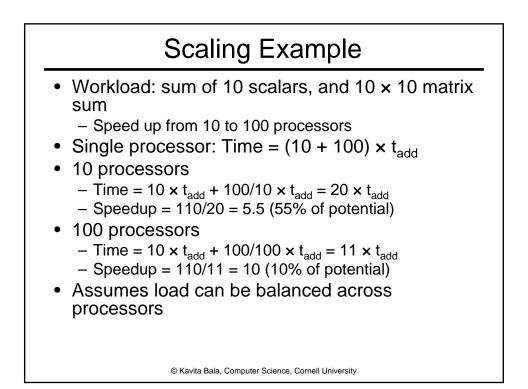

## Scaling Example (cont)

- What if matrix size is 100 x 100?

- Single processor: Time =  $(10 + 10000) \times t_{add}$

- 10 processors

- Time = 10 × t<sub>add</sub> + 10000/10 × t<sub>add</sub> = 1010 × t<sub>add</sub>

- Speedup = 10010/1010 = 9.9 (99% of potential)

- 100 processors

- Time = 10 ×  $t_{add}$  + 10000/100 ×  $t_{add}$  = 110 ×  $t_{add}$

- Speedup = 10010/110 = 91 (91% of potential)

- Assuming load balanced

© Kavita Bala, Computer Science, Cornell University