|     | Announcements                                                                   |

|-----|---------------------------------------------------------------------------------|

| •   | HW 3                                                                            |

| •   | HW4: due this Friday                                                            |

| • F | PA 3 out Nov 14 <sup>th</sup>                                                   |

|     | <ul> <li>Due Nov 25<sup>th</sup> (feel free to turn it in early)</li> </ul>     |

|     | <ul> <li>Demos and pizza party: Dec 1<sup>st</sup> or 2<sup>nd</sup></li> </ul> |

| • [ | Prelim 2: Dec 4th                                                               |

| • F | -inal project: distributed multicore ray tracer                                 |

|     | – Due exam week                                                                 |

|     | © Kavita Bala, Computer Science, Cornell University                             |

© Kavita Bala, Computer Science, Cornell University

| Virtual Memory Design Parameters |            |                                        |             |  |  |  |

|----------------------------------|------------|----------------------------------------|-------------|--|--|--|

|                                  | L1         | Paged Memory                           | TLB         |  |  |  |

| Size<br>(blocks)                 | 1/4k to 4k | 16k to 1M                              | 64 to 4k    |  |  |  |

| Size<br>(kB)                     | 16 to 64   | 1M to 4G                               | 2 to 16     |  |  |  |

| Block<br>size (B)                | 16-64      | 4k to 64k                              | 4-32        |  |  |  |

| Miss<br>rates                    | 2%-5%      | 10 <sup>-4</sup> to 10 <sup>-5</sup> % | 0.01% to 2% |  |  |  |

| Miss<br>penalty                  | 10-25      | 10M-100M                               | 10-1000     |  |  |  |

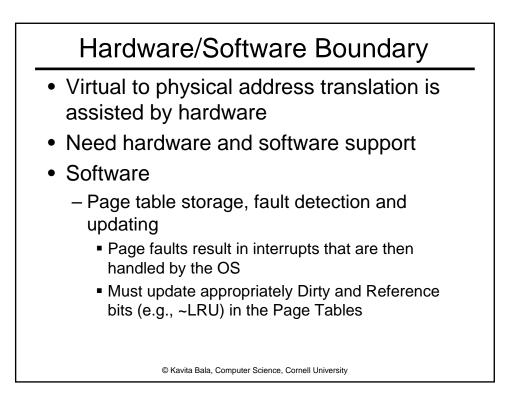

## Hardware/Software Boundary

- Hardware support for exceptions

- Exception program counter

- Cause register

- Special instructions to load TLB

- Only do-able by kernel

- Precise and imprecise exceptions

- In pipelined architecture

- Have to correctly identify PC of exception

- MIPS and modern processors support this

© Kavita Bala, Computer Science, Cornell University

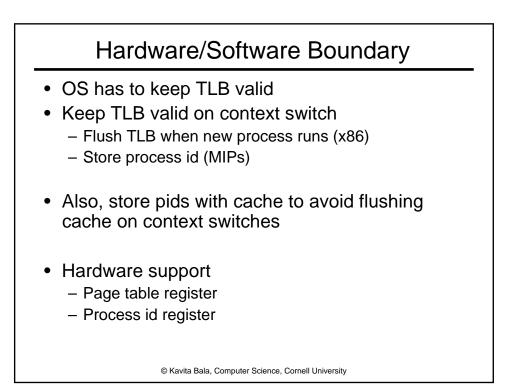

## Hardware/Software Boundary

- Hardware guarantees

- Previous instructions complete

- Later instructions are flushed

- EPC and cause register are set

- Jump to prearranged address in OS

- When you come back, restart instruction

- Disable exceptions while responding to one

- Otherwise can overwrite EPC and cause

© Kavita Bala, Computer Science, Cornell University

© Kavita Bala, Computer Science, Cornell University

| Terminology                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Trap <ul> <li>Any kind of a control transfer to the OS</li> </ul> </li> <li>Syscall <ul> <li>Synchronous, program-initiated control transfer from user to the OS to obtain service from the OS</li> <li>e.g. SYSCALL</li> </ul> </li> </ul>                                                                                       |

| <ul> <li>Exception         <ul> <li>Asynchronous, program-initiated control transfer from user to the OS in response to an exceptional event</li> <li>e.g. Divide by zero, TLB miss, Page fault</li> </ul> </li> <li>Interrupt         <ul> <li>Asynchronous, device-initiated control transfer from user to the OS</li> </ul> </li> </ul> |

| - e.g. Network packet, I/O complete<br>© Kavita Bala, Computer Science, Cornell University                                                                                                                                                                                                                                                 |

| Terminology                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Trap <ul> <li>Any kind of a control transfer to the OS</li> </ul> </li> <li>Syscall <ul> <li>Synchronous, program-initiated control transfer from</li> </ul> </li> </ul> |

| <ul> <li>user to the OS to obtain service from the OS</li> <li>– e.g. SYSCALL</li> <li>Exception</li> </ul>                                                                       |

| <ul> <li>Asynchronous, program-initiated control transfer from<br/>user to the OS in response to an exceptional event</li> <li>e.g. Divide by zero</li> <li>Interrupt</li> </ul>  |

| <ul> <li>Asynchronous, device-initiated control transfer from<br/>user to the OS</li> <li>e.g. Clock tick, network packet</li> </ul>                                              |

| © Kavita Bala, Computer Science, Cornell University                                                                                                                               |