CS 316: Caches-III

Kavita Bala Fall 2007 Computer Science Cornell University

## Announcements

- HW 1 grades are out

- HW 2 is due on Friday

- PA 4 is out on Friday

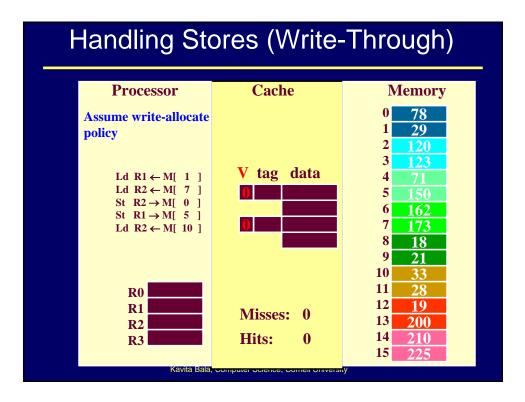

| Processor       Cache       Memory $\downarrow$ Ld RI $\leftarrow$ M[ 1 ] $\downarrow$ $\downarrow$ $\downarrow$ $\downarrow$ $\downarrow$ Ld RI $\leftarrow$ M[ 1 ] $\downarrow$ $V$ tag data $\downarrow$ $\downarrow$ $\downarrow$ Ld RI $\leftarrow$ M[ 7 ] $V$ tag data $\downarrow$ $\uparrow$ $\downarrow$ $\downarrow$ Ld RI $\leftarrow$ M[ 7 ] $V$ tag data $\downarrow$ $\uparrow$ $\downarrow$ $\downarrow$ R2 $\leftarrow$ M[ 10 ] $V$ tag data $\downarrow$ $\uparrow$ $\downarrow$ $\downarrow$ R1 $\leftarrow$ $\downarrow$ $\downarrow$ $\downarrow$ $\downarrow$ $\downarrow$ $R_1$ $R_2$ $R_3$ $Misses: 0$ $13$ $200$ $R_1$ $R_2$ $Hits: 0$ $14$ $210$ $15$ $225$ | Write-T                                                                                                                                                                                                                      | hrough (RE                                        | F 1)                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------|

| Kouite Bala, Computer Science, Cornell University                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $ \begin{array}{c} & \longrightarrow \ Ld \ R1 \leftarrow M[ \ 1 \ ] \\ Ld \ R2 \leftarrow M[ \ 7 \ ] \\ St \ R2 \rightarrow M[ \ 0 \ ] \\ St \ R1 \rightarrow M[ \ 5 \ ] \\ Ld \ R2 \leftarrow M[ \ 10 \ ] \\ \end{array} $ | V tag data<br>0<br>0<br>0<br>Misses: 0<br>Hits: 0 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

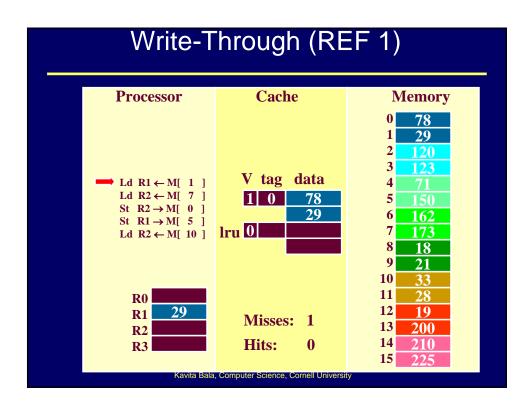

| Write-T                                                                                                                                             | hrough (RE                                   | F 2)                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------|

| Processor<br>Ld $R1 \leftarrow M[1]$<br>Ld $R2 \leftarrow M[7]$<br>St $R2 \rightarrow M[0]$<br>St $R1 \rightarrow M[5]$<br>Ld $R2 \leftarrow M[10]$ | Cache<br>V tag data<br>1 0 78<br>29<br>Iru 0 | Memory<br>0 78<br>1 29<br>2 120<br>3 123<br>4 71<br>5 150<br>6 162<br>7 173<br>8 18<br>9 21<br>10 33 |

| R0<br>R1 29<br>R2<br>R3<br>Kavita Bala                                                                                                              | Misses: 1<br>Hits: 0                         | 11     28       12     19       13     200       14     210       15     225                         |

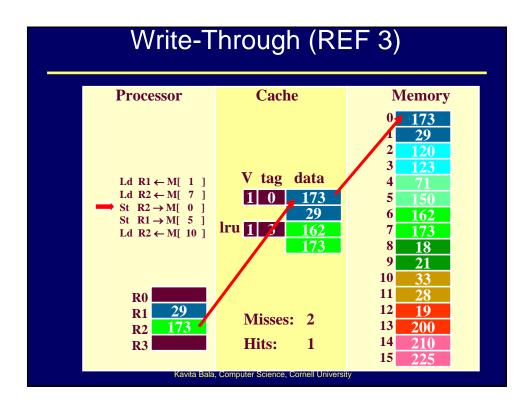

| Write-T                                                                                                                                                                            | hrough (RE                                                                        | EF 3)                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Processor<br>Ld $R1 \leftarrow M[1]$<br>Ld $R2 \leftarrow M[7]$<br>St $R2 \rightarrow M[0]$<br>St $R1 \rightarrow M[5]$<br>Ld $R2 \leftarrow M[10]$<br>R0<br>R1<br>29<br>R2<br>173 | Cache<br>V tag data<br>Iru 1 0 78<br>29<br>1 3 162<br>173<br>Misses: 2<br>Hits: 0 | Memory<br>0 78<br>1 29<br>2 120<br>3 123<br>4 71<br>5 150<br>6 162<br>7 173<br>8 18<br>9 21<br>10 33<br>11 28<br>12 19<br>13 200<br>14 210 |

| R3 Kavita Bala                                                                                                                                                                     | , Computer Science, Cornell Universi                                              | 15 225                                                                                                                                     |

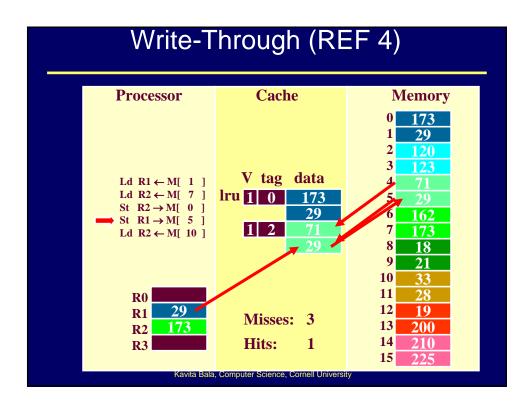

| Processor       Cache       Memory $Ld RI \leftarrow M[1]$ 1       29 $Ld R1 \leftarrow M[1]$ 1       29 $Ld R2 \leftarrow M[7]$ 3       123 $St R2 \rightarrow M[0]$ V tag data       4 $St R1 \rightarrow M[5]$ 29       6 $Ld R2 \leftarrow M[10]$ 29       6 $R1 = 29$ 162       7 $R1 = 29$ 11       28 $R1 = 29$ Misses: 2       13 $R3 = 173$ Hits: 1       14 | Write-T                                                                                                                                                                                                                                                                                                                                                                                                                                   | hrough (RE                                                     | F 4)                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|

| 15 225                                                                                                                                                                                                                                                                                                                                                                | $ \begin{array}{c} \text{Ld } \text{R1} \leftarrow \text{M[} 1 \text{ ]} \\ \text{Ld } \text{R2} \leftarrow \text{M[} 7 \text{ ]} \\ \text{St } \text{R2} \rightarrow \text{M[} 0 \text{ ]} \\ \implies \text{St } \text{R1} \rightarrow \text{M[} 5 \text{ ]} \\ \text{Ld } \text{R2} \leftarrow \text{M[} 10 \text{ ]} \\ \end{array} $ $ \begin{array}{c} \text{R0} \\ \text{R1} \\ \text{R2} \\ \text{R2} \\ \text{173} \end{array} $ | V tag data<br>1 0 173<br>29<br>Iru 1 3 162<br>173<br>Misses: 2 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

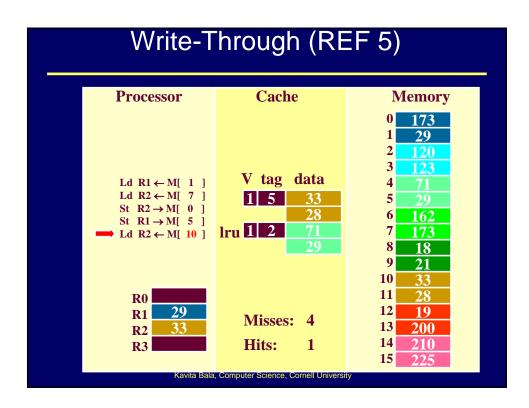

| Write-T                                                                                                                | hrough (RE                                                                                                                          | EF 5)                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Processor<br>Ld R1 $\leftarrow$ M[1]<br>Ld R2 $\leftarrow$ M[7]<br>St R2 $\rightarrow$ M[0]<br>St R1 $\leftarrow$ M[5] | Cache<br>V tag data<br>Iru 1 0 173<br>29                                                                                            | Memory<br>0 173<br>1 29<br>2 120<br>3 123<br>4 71<br>5 29<br>6 162                                                                    |

| St $R1 \rightarrow M[5]$<br>$\rightarrow Ld R2 \leftarrow M[10]$<br>R0<br>R1<br>R2<br>R2<br>R2<br>R3<br>Kavita Bala    | 1       2       71         29       29         Misses:       3         Hits:       1         . Computer Science, Cornell University | $\begin{array}{c ccccc} 7 & 173 \\ 8 & 18 \\ 9 & 21 \\ 10 & 33 \\ 11 & 28 \\ 12 & 19 \\ 13 & 200 \\ 14 & 210 \\ 15 & 225 \end{array}$ |

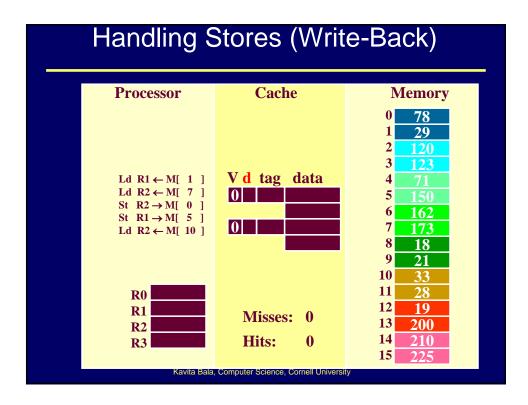

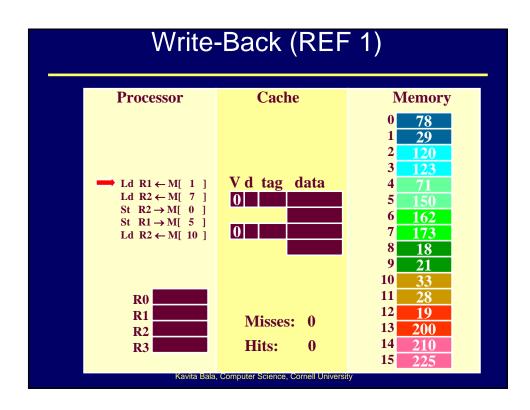

| Write                                                                                                                                                                             | -Back (REF                                                             | 1)                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor<br>Ld $R1 \leftarrow M[1]$<br>Ld $R2 \leftarrow M[7]$<br>St $R2 \rightarrow M[0]$<br>St $R1 \rightarrow M[5]$<br>Ld $R2 \leftarrow M[10]$<br>R0<br>R1<br>29<br>R2<br>R3 | Cache<br>V d tag data<br>1 0 0 78<br>29<br>E 0<br>Misses: 1<br>Hits: 0 | Memory         0       78         1       29         2       120         3       123         4       71         5       150         6       162         7       173         8       18         9       21         10       33         11       28         12       19         13       200         14       210         15       225 |

| Kavita Bala                                                                                                                                                                       | a, Computer Science, Cornell Universi                                  | ty                                                                                                                                                                                                                                                                                                                                   |

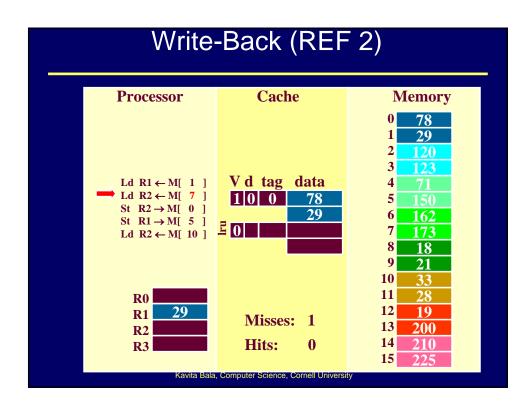

| Write                                                                                                                                               | -Back (REF                                              | 2)                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor<br>Ld $R1 \leftarrow M[1]$<br>Ld $R2 \leftarrow M[7]$<br>St $R2 \rightarrow M[0]$<br>St $R1 \rightarrow M[5]$<br>Ld $R2 \leftarrow M[10]$ | Cache<br>V d tag data<br>100 78<br>29<br>103 162<br>173 | Memory<br>0 78<br>1 29<br>2 120<br>3 123<br>4 71<br>5 150<br>6 162<br>7 173<br>8 18<br>9 21<br>1 29<br>2 120<br>3 123<br>4 71<br>5 150<br>6 162<br>7 173<br>8 18<br>9 21 |

| R0<br>R1 29<br>R2 173<br>R3<br>Kavita Bala                                                                                                          | Misses: 2<br>Hits: 0                                    | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                   |

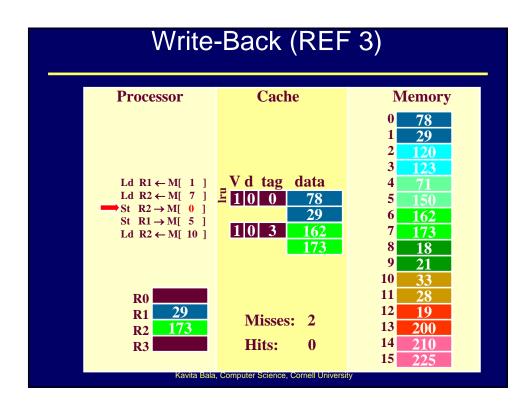

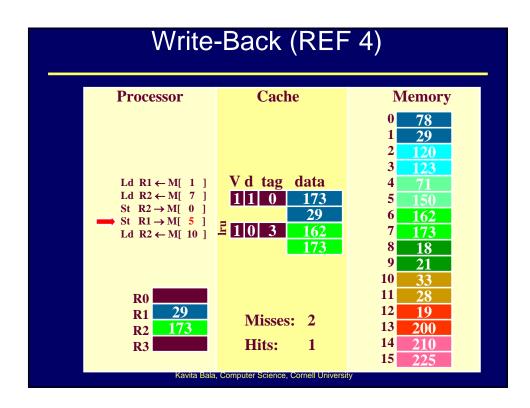

| Write                                                                                                                                                                | -Back (REF                                                               | 3)                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------|

| Processor                                                                                                                                                            | Cache                                                                    | Memory<br>0 78                                         |

| Ld $R1 \leftarrow M[1]$<br>Ld $R2 \leftarrow M[7]$<br>St $R2 \rightarrow M[0]$<br>St $R1 \rightarrow M[5]$<br>Ld $R2 \leftarrow M[10]$<br>R0<br>R1<br>29<br>R2<br>R3 | V d tag data<br>1 0 173<br>29<br>10 2 162<br>173<br>Misses: 2<br>Hits: 1 | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| Kavita Bala                                                                                                                                                          | , Computer Science, Cornell Universi                                     | ty                                                     |

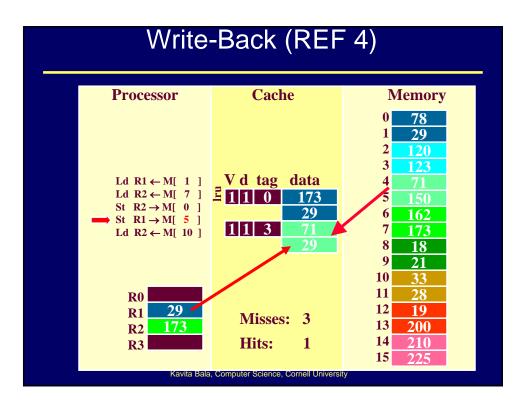

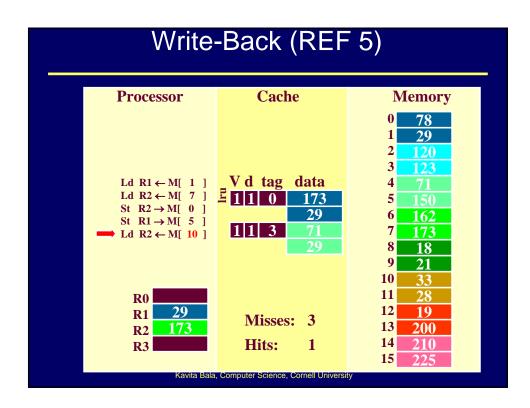

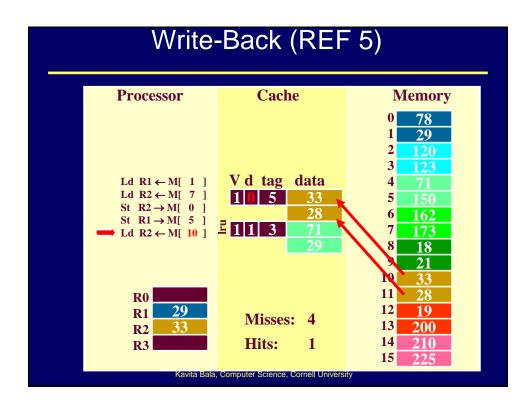

| Write                                                                                                                                                                                    | -Back (REF                                                                       | 5)                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor<br>Ld $R1 \leftarrow M[1]$<br>Ld $R2 \leftarrow M[7]$<br>St $R2 \rightarrow M[0]$<br>St $R1 \rightarrow M[5]$<br>Ld $R2 \leftarrow M[10]$<br>R0<br>R1<br>29<br>R2<br>173<br>R3 | Cache<br>V d tag data<br>1 0 173<br>29<br>1 1 3 71<br>29<br>Misses: 4<br>Hits: 1 | Memory         0       173         1       29         2       120         3       123         4       71         5       150         6       162         7       173         8       18         9       21         10       33         11       28         12       19         13       200         14       210         15       225 |

| Kavita Bala                                                                                                                                                                              | , Computer Science, Cornell Universi                                             | ty                                                                                                                                                                                                                                                                                                                                    |

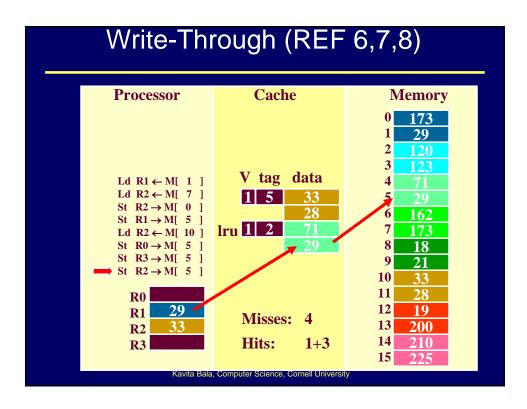

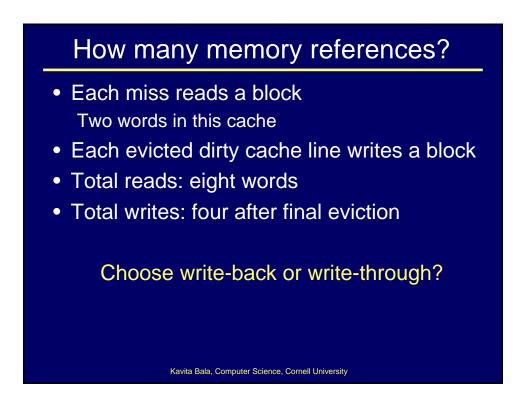

| Processor       Cache       Memory $Ld RI \leftarrow M[1]$ $0$ 78 $Ld RI \leftarrow M[1]$ $1$ $29$ $Ld RI \leftarrow M[1]$ $1$ $29$ $Ld RI \leftarrow M[1]$ $1$ $29$ $St R2 \rightarrow M[0]$ $1$ $28$ $St R2 \rightarrow M[5]$ $28$ $6$ $Ld R2 \leftarrow M[10]$ $28$ $6$ $St R3 \rightarrow M[5]$ $33$ $71$ $St R2 \rightarrow M[5]$ $33$ $9$ $St R2 \rightarrow M[5]$ $10$ $33$ $R1$ $29$ $10$ $33$ $R1$ $29$ $Misses: 4$ $13$ $200$ $R1$ $29$ $R3$ $Misses: 4$ $13$ $200$ $R1$ $29$ $R2$ $33$ $14$ $210$ $15$ $R2$ $33$ $R$ $13$ $200$ $15$ $225$ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

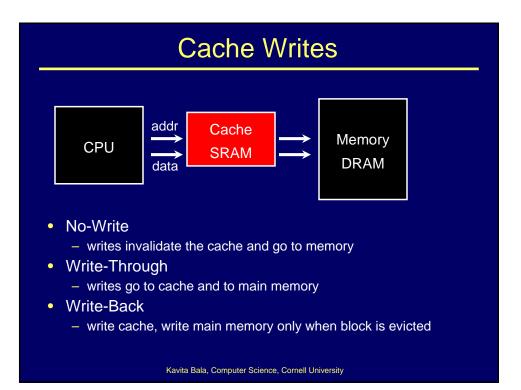

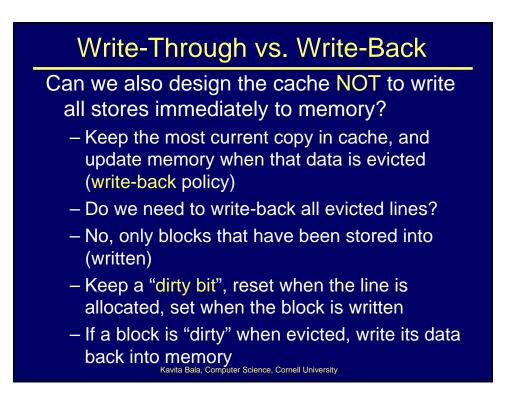

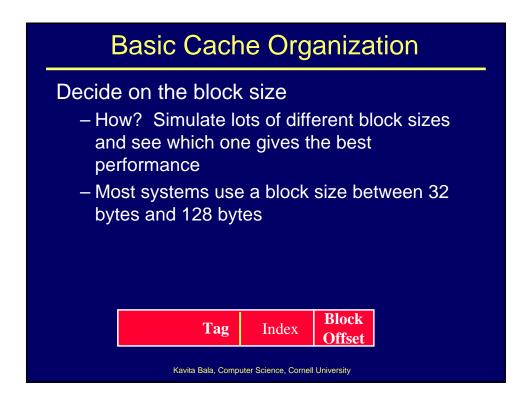

## Cache Design

- Need to determine parameters

- Block size

- Number of ways

- Eviction policy

- Write policy

- Separate I-cache from D-cache

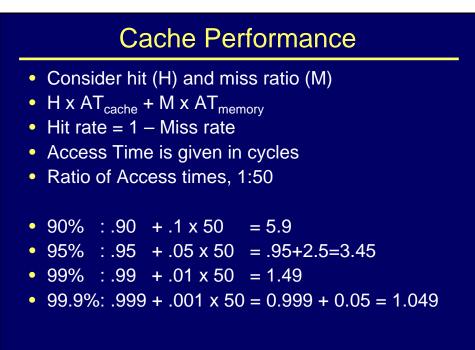

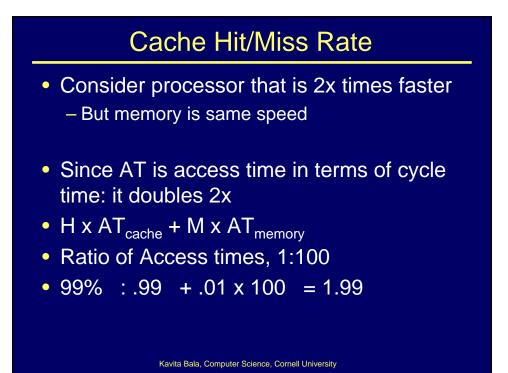

## Cache Hit/Miss Rate

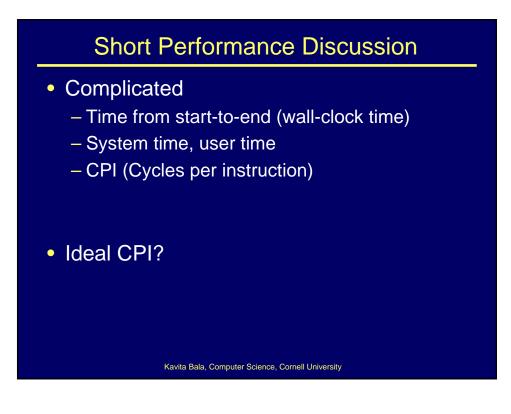

- Original is 1GHz, 1ns is cycle time

- CPI (cycles per instruction): 1.49

- Therefore, 1.49 ns for each instruction

- New is 2GHz, 0.5 ns is cycle time.

- CPI: 1.99, 0.5ns. 0.995 ns for each instruction.

- So it doesn't go to 0.745 ns for each instruction.

- Speedup is 1.5x (not 2x)

Kavita Bala, Computer Science, Cornell University

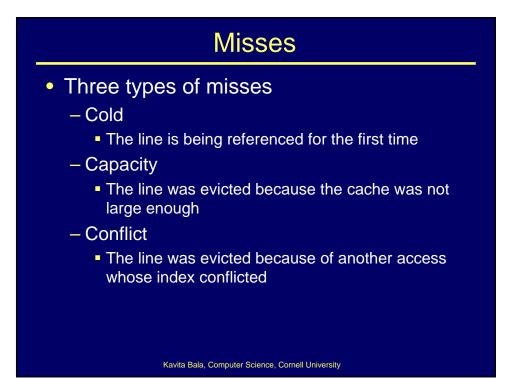

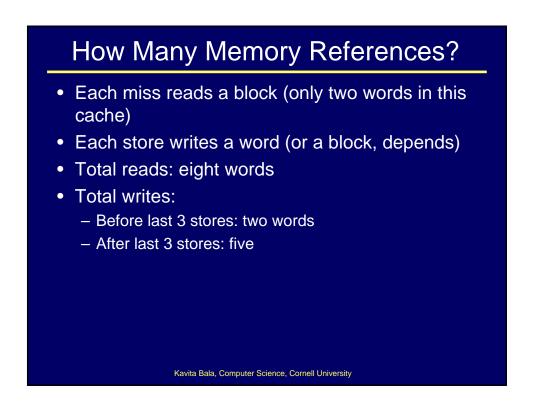

## Misses

- Three types of misses

- Cold

- The line is being referenced for the first time

- Capacity

- The line was evicted because the cache was not large enough

- Conflict

- The line was evicted because of another access whose index conflicted