## ECE/CS 314 Spring 2004

## Section 5

## Combinational Logic

From lecture, we have seen the design of a 1-bit full adder. Now, let's try to add a carryin bit to the input:

| А | В | Cin | Sum | Cout |

|---|---|-----|-----|------|

| 0 | 0 | 0   | 0   | 0    |

| 0 | 0 | 1   | 1   | 0    |

| 0 | 1 | 0   | 1   | 0    |

| 0 | 1 | 1   | 0   | 1    |

| 1 | 0 | 0   | 1   | 0    |

| 1 | 0 | 1   | 0   | 1    |

| 1 | 1 | 0   | 0   | 1    |

| 1 | 1 | 1   | 1   | 1    |

The equations can be derived immediately as:

$Sum = \underline{a} \underline{b} c + \underline{a} \underline{b} \underline{c} + \underline{a} \underline{b} \underline{c} + \underline{a} \underline{b} c$  $Cout = \underline{a} \underline{b} c + \underline{a} \underline{b} \underline{c} + \underline{a} \underline{b} \underline{c} + \underline{a} \underline{b} c$

To simplify the equations, Karnot Maps should be used:

Sum:

|   | <u>b</u> <u>c</u> | <u>b</u> c | b c | b <u>c</u> |

|---|-------------------|------------|-----|------------|

| a | 0                 | 1          | 0   | 1          |

| a | 1                 | 0          | 1   | 0          |

Cout:

|          | <u>b</u> <u>c</u> | <u>b</u> c | b c | b <u>c</u> |

|----------|-------------------|------------|-----|------------|

| <u>a</u> | 0                 | 0          | 1   | 0          |

| a        | 0                 | 1          | 1   | 1          |

While Sum cannot be reduced further, Cout can be reduced to:

Cout = a c + a b + b c

Espresso

Espresso is a logic minimization tool; it is installed on the BSD cluster. To demonstrate it, use the truth table from above. Place the table in a text file as follows (Let's call it adder.raw):

Don't-cares are indicated as '-' (rather than an 'x' from ECE230).

You can run espresso on this file by executing:

espresso –s adder.raw > adder.red

The reduced truth table will be saved in adder.red:

To extract the equations, look at each column on the right (output) side. A '1' indicates that the min-term on the left is included in the reduced equation. For example, the Sum column (1<sup>st</sup> column on the right side) has '1's at the last row (11-), which means that the min-terms is  $a \cdot b$ .

(Note: If an equation has more than one min-term, the result is just the "sum" of them)

Sequential Logic

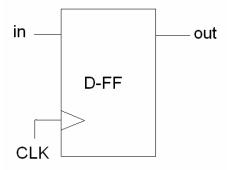

State holding element: D Flip-flop

On a positive edge of the clock signal, the D Flip-flop passes the input value to the output.

| Now, let's implement a 2-bit counter: |

|---------------------------------------|

|---------------------------------------|

| Reset | <b>S</b> 1 | SO | <b>S</b> 1' | S0' |

|-------|------------|----|-------------|-----|

| 0     | 0          | 0  | 0           | 1   |

| 0     | 0          | 1  | 1           | 0   |

| 0     | 1          | 0  | 1           | 1   |

| 0     | 1          | 1  | 0           | 0   |

| 1     | 0          | 0  | 0           | 0   |

| 1     | 0          | 1  | 0           | 0   |

| 1     | 1          | 0  | 0           | 0   |

| 1     | 1          | 1  | 0           | 0   |

|       |            |    |             |     |

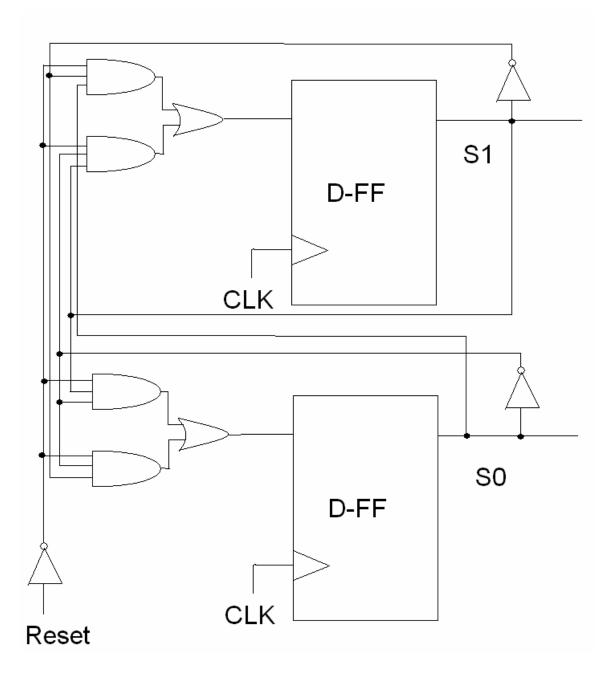

The equations of S0' and S1' can be derived as:

$\begin{array}{l} S1' = \underline{Reset}\,\underline{S1}\,\,S0 + \underline{Reset}\,\,S1\,\,\underline{S0}\\ S0' = \underline{Reset}\,\underline{S1}\,\,\underline{S0} + \underline{Reset}\,\,S1\,\,\underline{S0} \end{array}$

And here's a gate diagram of the circuit: