# **State and Finite State Machines**

Prof. Hakim Weatherspoon CS 3410, Spring 2015 Computer Science Cornell University

See P&H Appendix B.7. B.8, B.10, B.11

#### Announcements

#### Make sure you are

- Registered for class, can access CMS

- Have a Section you can go to.

- Lab Sections are required.

- "Make up" lab sections *only* 8:40am Wed, Thur, or Fri

- Bring laptop to Labs

- Project partners are required for projects.

- Have project partner in same Lab Section, if possible

#### HW1 and Lab1 available today, after lecture

- Do HW1 problems with lecture, i.e. finish part1 and 2 this week

- Work alone on both

- But, use your resources

- Lab Section, Piazza.com, Office Hours, Homework Help Session,

- Class notes, book, Sections, CSUGLab

#### Announcements

Make sure to go to <u>your</u> Lab Section this week Completed Lab1 due *before* winter break, Friday, Feb 13th Note, a Design Document is due when you submit Lab1 final circuit Work alone

#### Homework1 is available, after lecture

Due a week before prelim1, Monday, February 23rd *Work on problems incrementally, as we cover them in lecture* Office Hours for help Work **alone**

#### Work alone, **BUT** use your resources

- Lab Section, Piazza.com, Office Hours

- Class notes, book, Sections, CSUGLab

### Announcements

Check online syllabus/schedule

- http://www.cs.cornell.edu/Courses/CS3410/2015sp/schedule.html

- Slides and Reading for lectures

- Office Hours

- Pictures of all TAs

- Homework and Programming Assignments

- Dates to keep in Mind

- Prelims: Tue Mar 3rd and Thur April 30th

- Lab 1: Due next Friday, Feb 13th before Winter break

- Proj2: Due Thur Mar 26th before Spring break

- Final Project: Due when final would be (not known until Feb 14t

#### Schedule is subject to change

## Collaboration, Late, Re-grading Policies

"Black Board" Collaboration Policy

- Can discuss approach together on a "black board"

- Leave and write up solution independently

- Do not copy solutions

Late Policy

- Each person has a total of *four* "slip days"

- Max of *two* slip days for any individual assignment

- Slip days deducted first for *any* late assignment, cannot selectively apply slip days

- For projects, slip days are deducted from all partners

- 25% deducted per day late after slip days are exhausted

**Regrade policy**

- Submit written request to lead PhD TA (Deniz, Vishal, Adam, Praveen), and lead TA will pick a different grader

- Submit another written request, lead TA will regrade directly

- Submit yet another written request for professor to regrade.

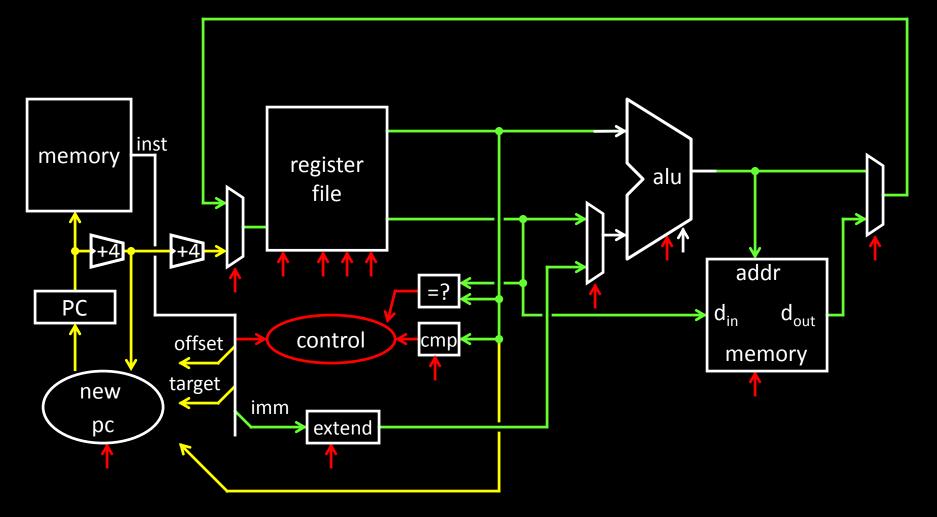

# **Big Picture: Building a Processor**

A Single cycle processor

#### Review

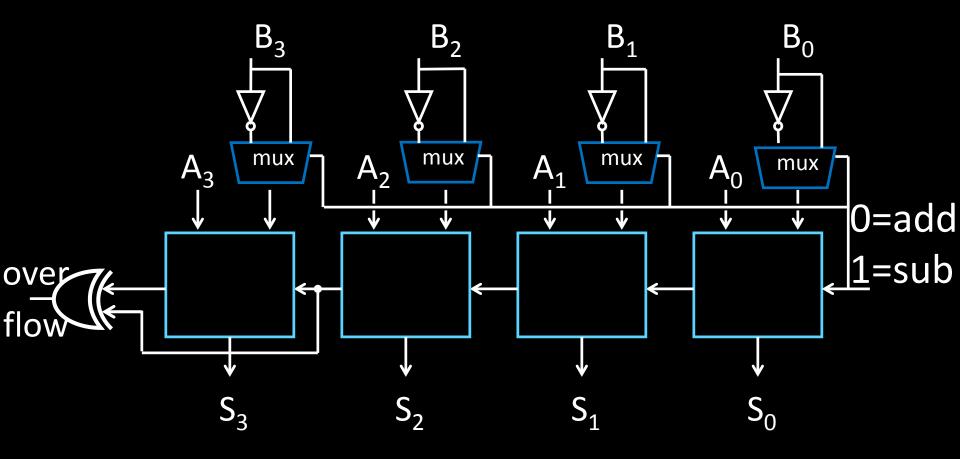

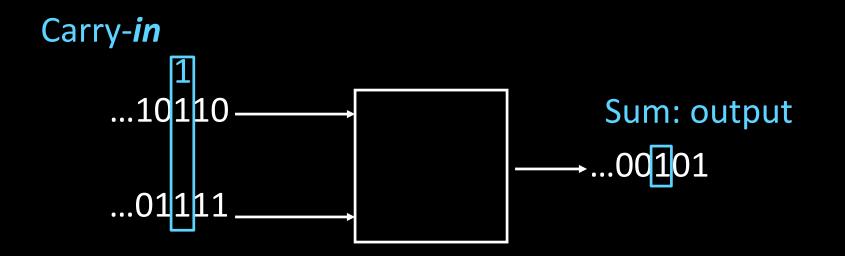

• We can generalize 1-bit Full Adders to 32 bits, 64 bits ...

#### Review

• We can generalize 1-bit Full Adders to 32 bits, 64 bits ...

- We can generalize 1-bit Full Adders to 32 bits, 64 bits ...

- How long does it take to compute a result?

- We can generalize 1-bit Full Adders to 32 bits, 64 bits ...

- How long does it take to compute a result?

- A) 2 ns

- B) 2 gate delays

- C) 10 ns

- D) 10 gate delays

- E) 8 gate delays

- We can generalize 1-bit Full Adders to 32 bits, 64 bits ...

- How long does it take to compute a result?

- We can generalize 1-bit Full Adders to 32 bits, 64 bits ...

- How long does it take to compute a result?

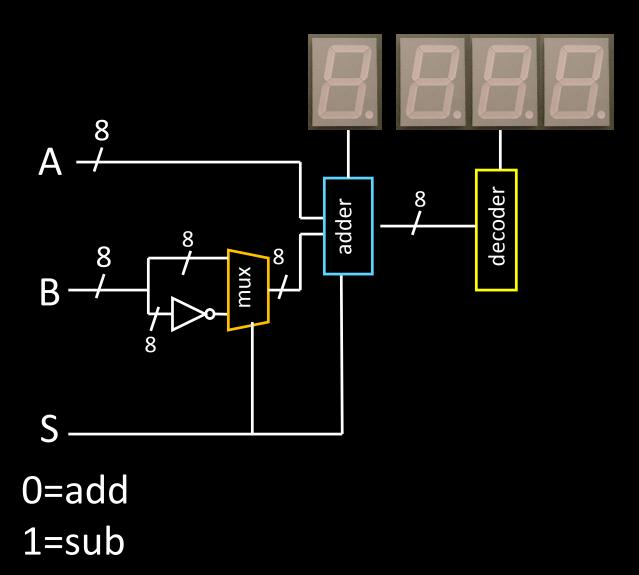

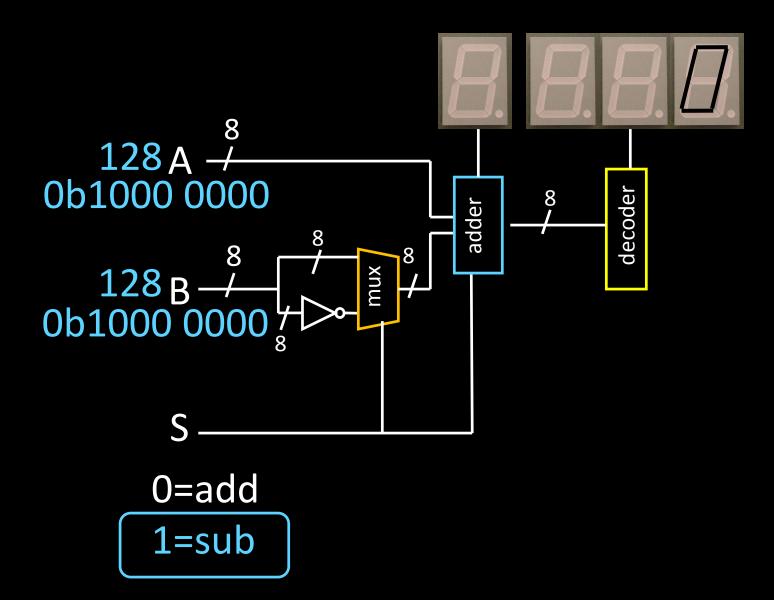

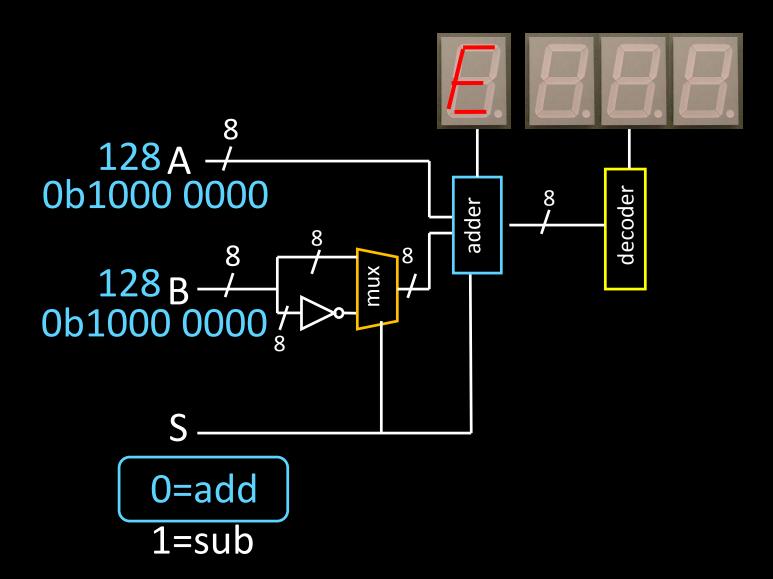

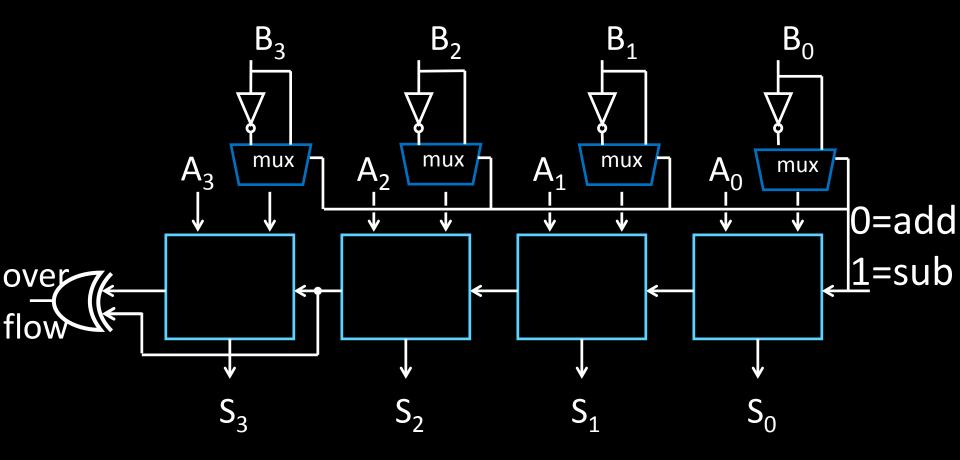

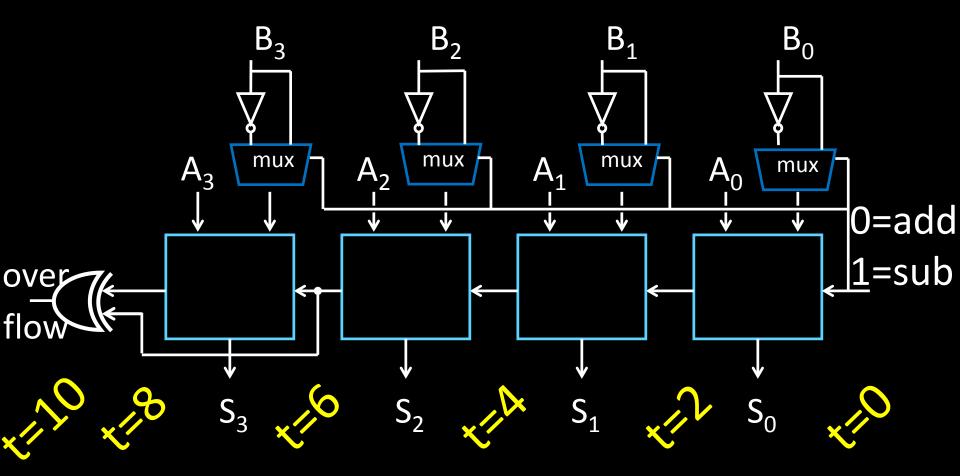

- Can we store the result? Ba  $B_{\gamma}$  $B_1$ B<sub>0</sub> mux mux mux  $A_{2}$  $A_0$ mux  $A_1$ 0=add \_sub ove flow  $S_3$  $S_2$

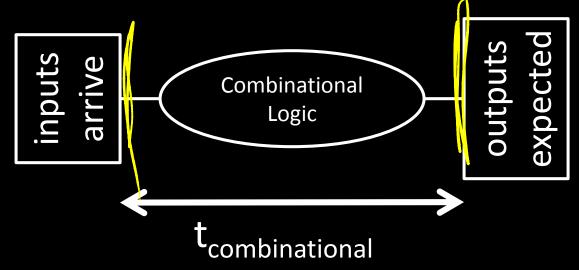

### Performance

Speed of a circuit is affected by the number of gates in series (on the *critical path* or the *deepest level of logic*)

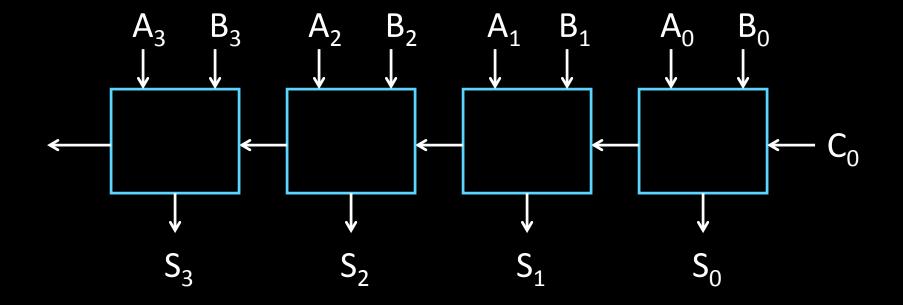

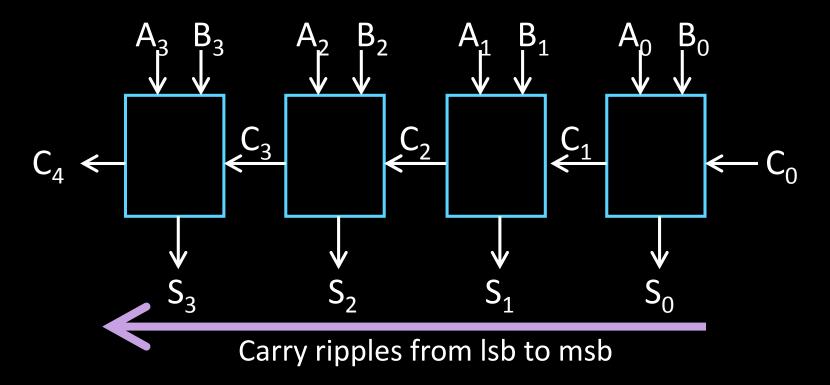

# 4-bit Ripple Carry Adder

• First full adder, 2 gate delay

Second full adder, 2 gate delay

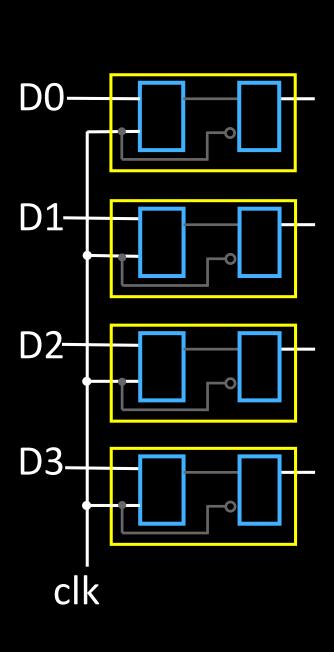

#### Stateful Components Until now is combinationial logic

- Output is computed when inputs are present

- System has no internal state

- Nothing computed in the present can depend on what happened in the past!

Need a way to record data

- Need a way to build stateful circuits

- Need a state-holding device

Finite State Machines

# **Goals for Today**

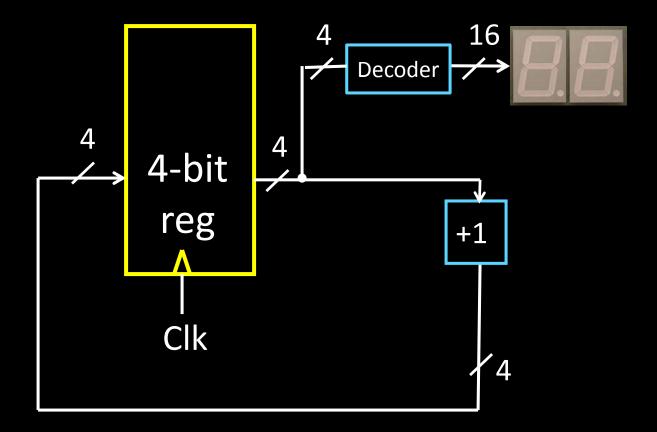

#### State

• How do we store *one* bit?

- Attempts at storing (and changing) one bit

- Set-Reset Latch

- D Latch

- D Flip-Flops

- Master-Slave Flip-Flops

- Register: storing more than one bit, N-bits

#### **Basic Building Blocks**

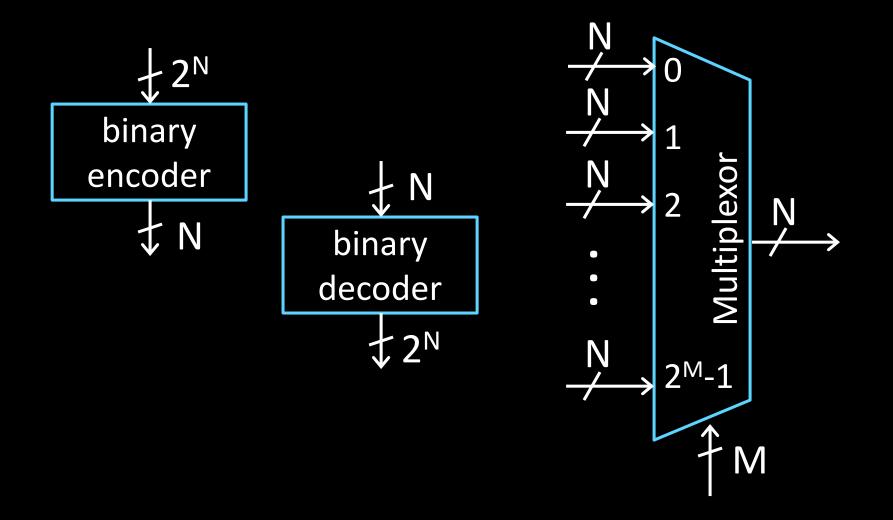

Decoders and Encoders

Finite State Machines (FSM)

- How do we design logic circuits with state?

- Types of FSMs: Mealy and Moore Machines

- Examples: Serial Adder and a Digital Door Lock

#### Goal

#### How do we store store **one** bit?

## First Attempt: Unstable Devices

## First Attempt: Unstable Devices

#### Does not work!

- Unstable

- Oscillates wildly!

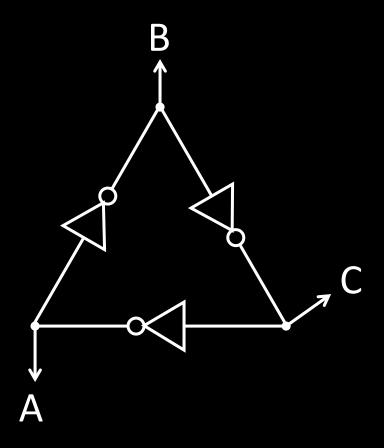

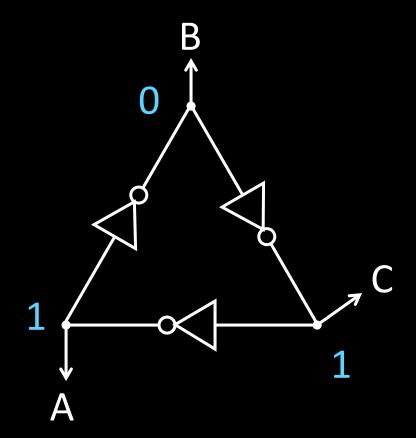

## Second Attempt: Bistable Devices

Stable and unstable equilibria?

A Simple Device

In stable state, A = B

How do we change the state?

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| S | R | Q | $\overline{\mathrm{Q}}$ |

|---|---|---|-------------------------|

| 0 | 0 |   |                         |

| 0 | 1 |   |                         |

| 1 | 0 |   |                         |

| 1 | 1 |   |                         |

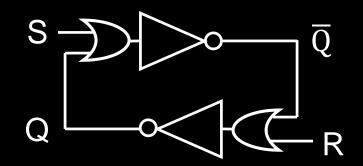

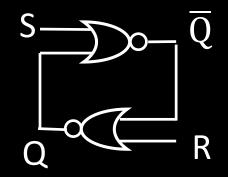

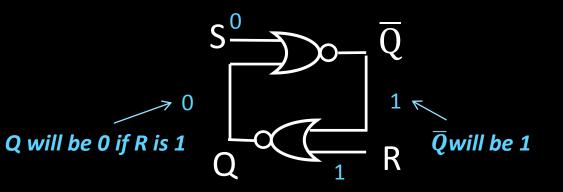

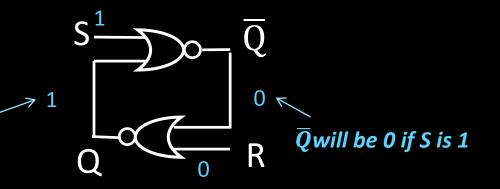

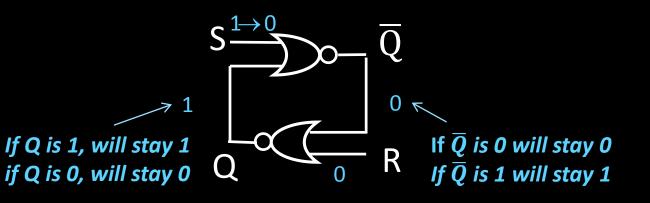

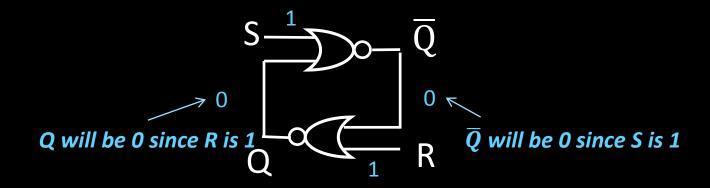

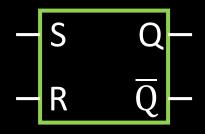

#### Set-Reset (S-R) Latch

Stores a value Q and its complement

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| S | R | Q | $\overline{Q}$ |

|---|---|---|----------------|

| 0 | 0 |   |                |

| 0 | 1 | 0 | 1              |

| 1 | 0 |   |                |

| 1 | 1 |   |                |

Set-Reset (S-R) Latch

Stores a value Q and its complement

Q will be 1

| S | R | Q | $\overline{\mathrm{Q}}$ |

|---|---|---|-------------------------|

| 0 | 0 |   |                         |

| 0 | 1 | 0 | 1                       |

| 1 | 0 | 1 | 0                       |

| 1 | 1 |   |                         |

Set-Reset (S-R) Latch

**0** and **0**

<u>0 and 1</u>

1 and 0

1 and 1

a)

b

| Α | Β | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

Stores a value Q and its complement

What are the values for Q and Q?

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| S | R | Q | $\overline{\mathrm{Q}}$ |

|---|---|---|-------------------------|

| 0 | 0 | Q | $\overline{\mathbf{Q}}$ |

| 0 | 1 | 0 | 1                       |

| 1 | 0 | 1 | 0                       |

| 1 | 1 |   |                         |

Set-Reset (S-R) Latch

Stores a value Q and its complement

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| S | R | Q | $\overline{\mathbf{Q}}$ |

|---|---|---|-------------------------|

| 0 | 0 | Q | $\overline{\mathbf{Q}}$ |

| 0 | 1 | 0 | 1                       |

| 1 | 0 | 1 | 0                       |

| 1 | 1 | ? | ?                       |

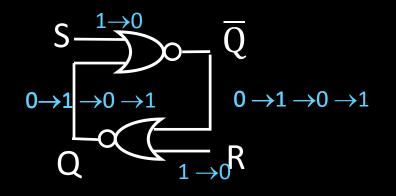

Set-Reset (S-R) Latch

Stores a value Q and its complement

What happens when S,R changes from 1,1 to 0,0?

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

| S | R | Q      | $\overline{\mathbf{Q}}$ |

|---|---|--------|-------------------------|

| 0 | 0 | Q      | $\overline{\mathbf{Q}}$ |

| 0 | 1 | 0      | 1                       |

| 1 | 0 | 1      | 0                       |

| 1 | 1 | forbio | dden                    |

Set-Reset (S-R) Latch

Stores a value Q and its complement

What happens when S,R changes from 1,1 to 0,0?

Q and  $\overline{Q}$  become unstable and will oscillate wildly between values 0,0 to 1,1 to 0,0 to 1,1 ...

| S | R | Q         | $\overline{Q}$ |       |

|---|---|-----------|----------------|-------|

| 0 | 0 | Q         | $\overline{Q}$ | hold  |

| 0 | 1 | 0         | 1              | reset |

| 1 | 0 | 1         | 0              | set   |

| 1 | 1 | forbidden |                |       |

#### Set-Reset (S-R) Latch

Stores a value Q and its complement

## Takeaway

Set-Reset (SR) Latch can store one bit and we can change the value of the stored bit. But, SR Latch has a forbidden state.

### **Next Goal**

#### How do we avoid the forbidden state of S-R Latch?

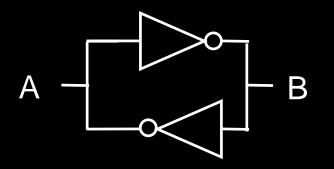

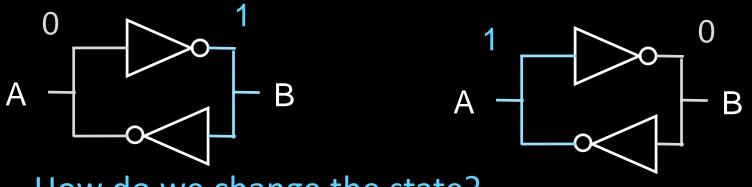

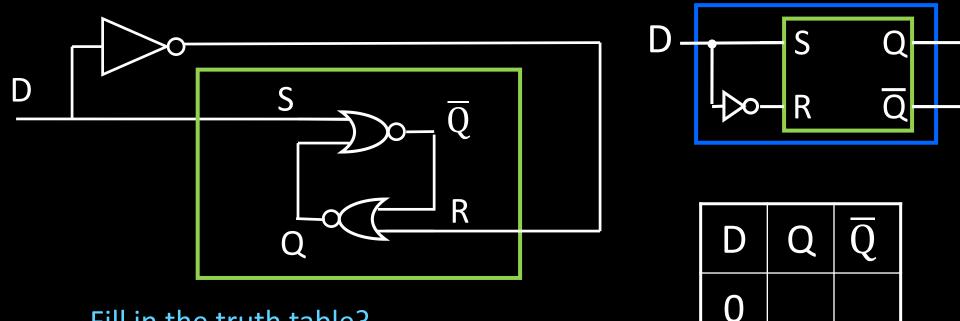

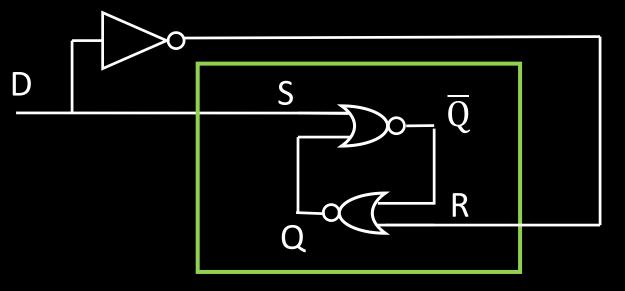

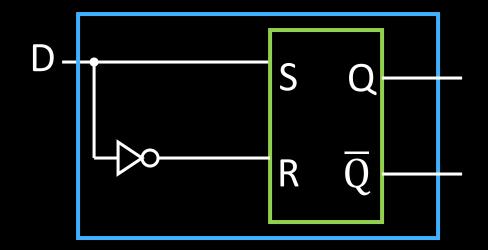

## Fourth Attempt: (Unclocked) D Latch

Fill in the truth table?

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

1

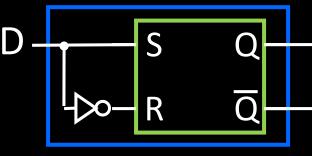

# Fourth Attempt: (Unclocked) D Latch

#### Fill in the truth table?

#### Data (D) Latch

- Easier to use than an SR latch

- No possibility of entering an undefined state

#### When D changes, Q changes

… immediately (…after a delay of 2 Ors and 2 NOTs)

Need to control when the output changes

| D | Q | Q |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

| Α | В | OR | NOR |

|---|---|----|-----|

| 0 | 0 | 0  | 1   |

| 0 | 1 | 1  | 0   |

| 1 | 0 | 1  | 0   |

| 1 | 1 | 1  | 0   |

## Takeaway

Set-Reset (SR) Latch can store one bit and we can change the value of the stored bit. But, SR Latch has a forbidden state.

(Unclocked) D Latch can store and change a bit like an SR Latch while avoiding the forbidden state.

#### **Next Goal**

#### How do we coordinate state changes to a D Latch?

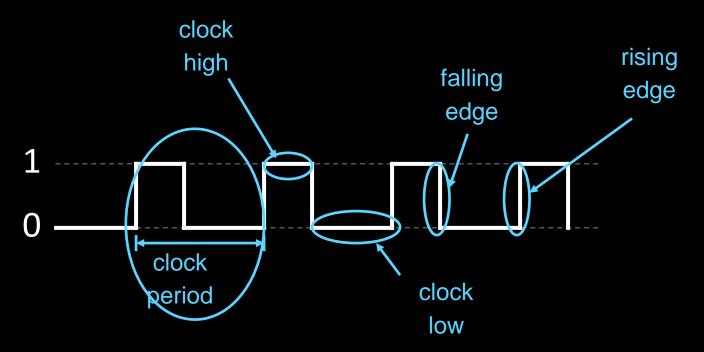

## Clocks

Clock helps coordinate state changes

- Usually generated by an oscillating crystal

- Fixed period; frequency = 1/period

## **Clock Disciplines**

#### Level sensitive

State changes when clock is high (or low)

#### Edge triggered

State changes at clock edge

positive edge-triggered

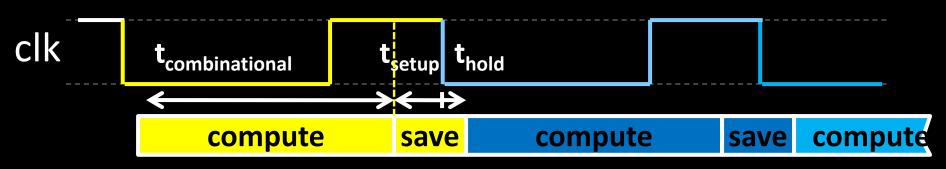

## **Clock Methodology**

Clock Methodology

#### •Negative edge, synchronous

Edge-Triggered: Signals must be stable near falling clock edge

#### Positive edge synchronous

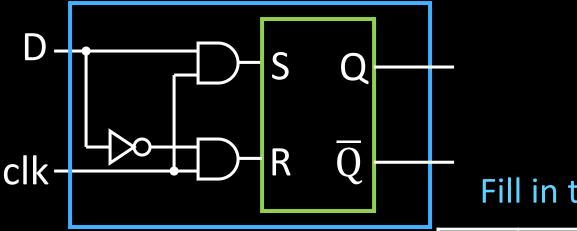

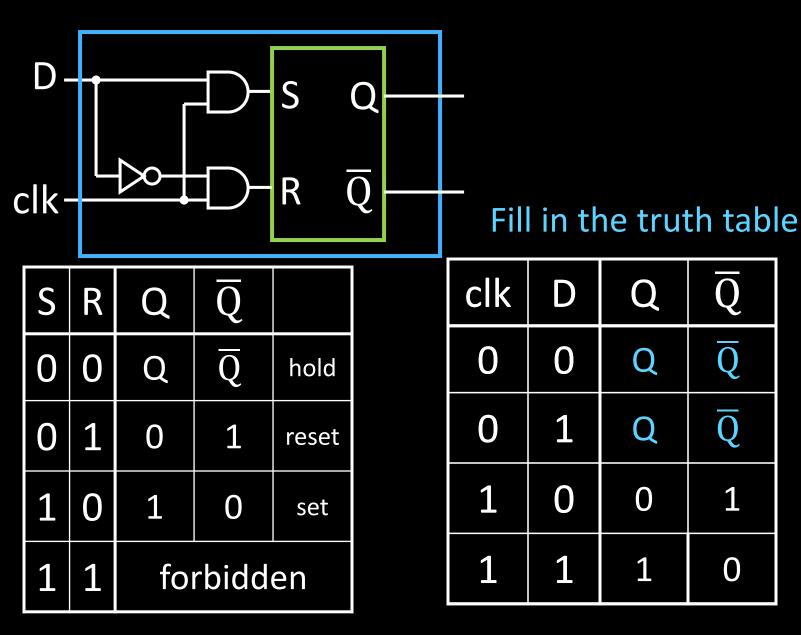

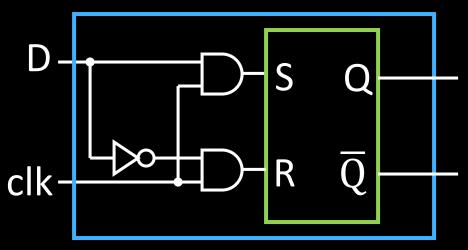

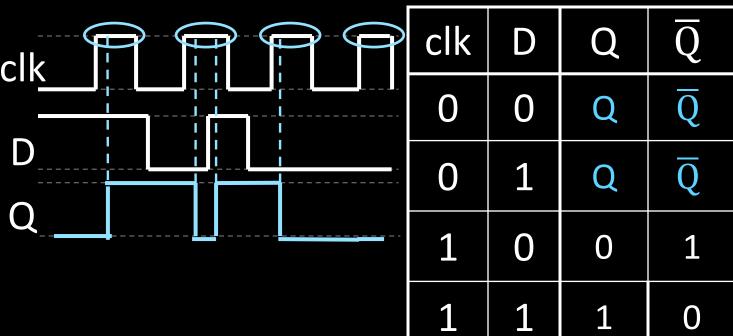

#### Fill in the truth table

| clk | D | Q | $\overline{\mathrm{Q}}$ |

|-----|---|---|-------------------------|

| 0   | 0 |   |                         |

| 0   | 1 |   |                         |

| 1   | 0 |   |                         |

| 1   | 1 |   |                         |

Clock high: set/reset (according to D) Clock low: keep state (ignore D)

## Takeaway

Set-Reset (SR) Latch can store one bit and we can change the value of the stored bit. But, SR Latch has a forbidden state.

(Unclocked) D Latch can store and change a bit like an SR Latch while avoiding a forbidden state.

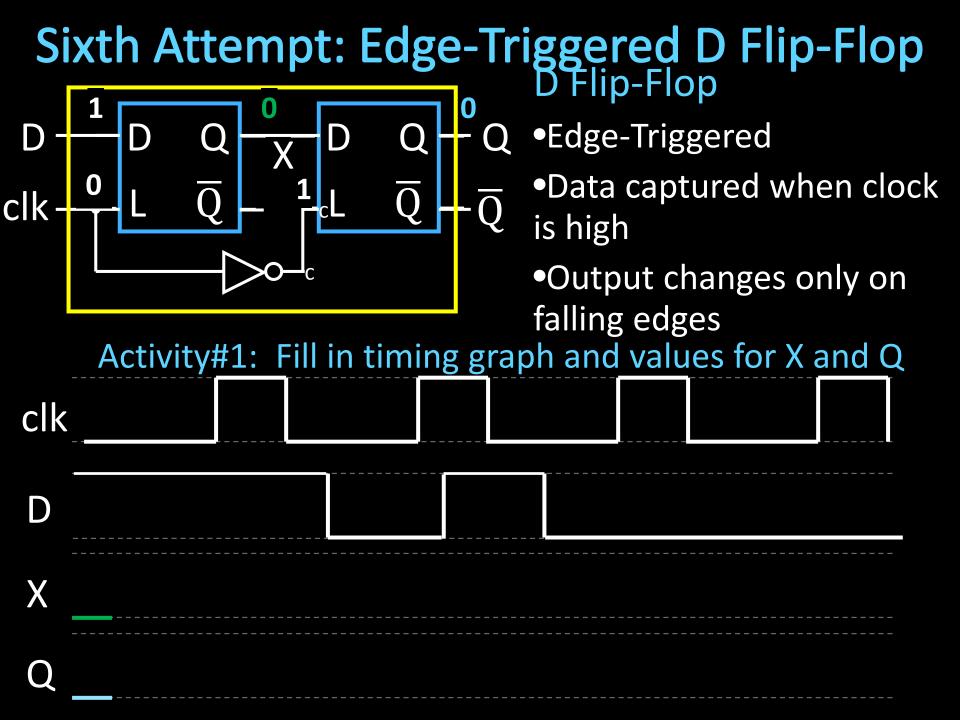

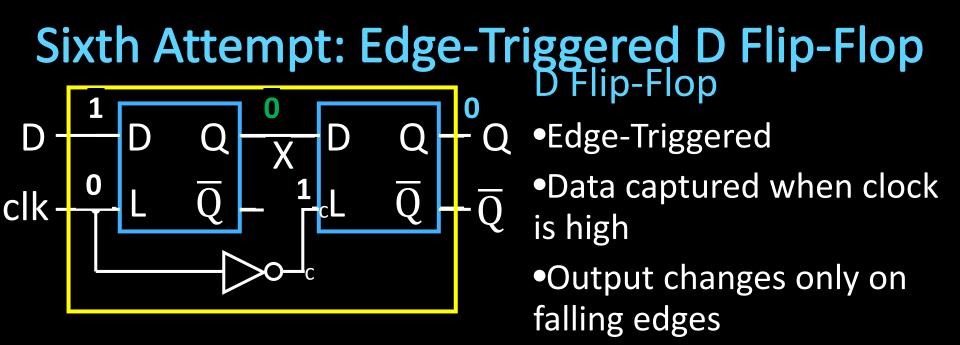

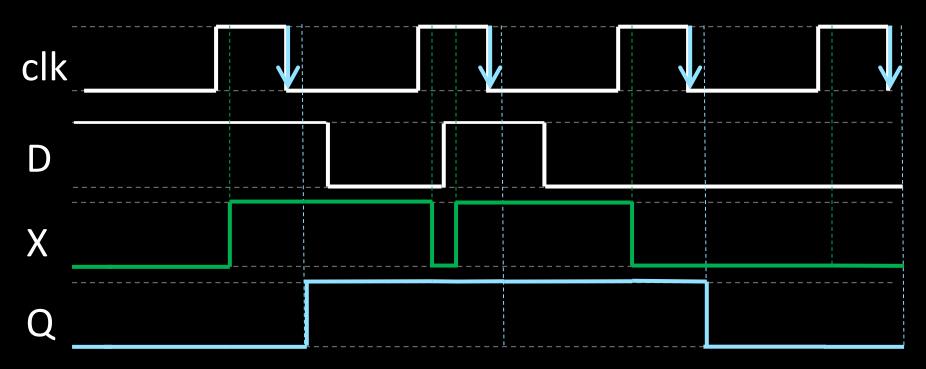

An Edge-Triggered D Flip-Flip (aka Master-Slave D Flip-Flip) stores one bit. The bit can be changed in a synchronized fashion on the edge of a clock signal.

#### **Next Goal**

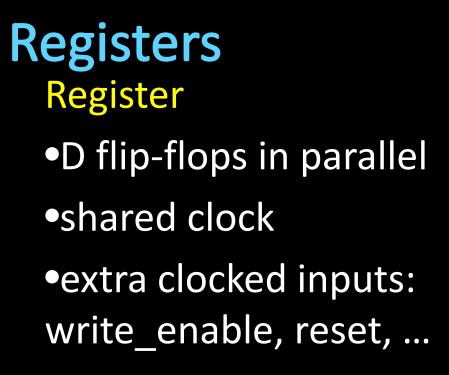

#### How do we store more than one bit, N bits?

## Takeaway

Set-Reset (SR) Latch can store one bit and we can change the value of the stored bit. But, SR Latch has a forbidden state.

(Unclocked) D Latch can store and change a bit like an SR Latch while avoiding a forbidden state.

An Edge-Triggered D Flip-Flip (aka Master-Slave D Flip-Flip) stores one bit. The bit can be changed in a synchronized fashion on the edge of a clock signal. An *N*-bit **register** stores *N*-bits. It is created with *N* D-Flip-Flops in parallel along with a shared clock.

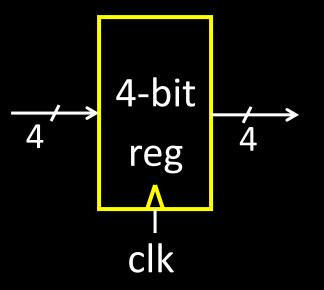

## An Example: What will this circuit do?

#### An Example: What will this circuit do? Reset Run 16 WE R Decoder 4 1 = 0001 = B[4]4 A[4] 4-bit reg Cout +1 S[4] Clk 4

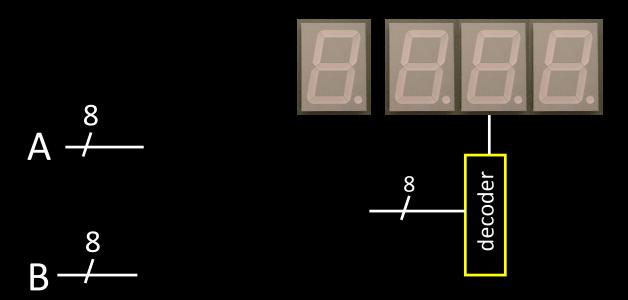

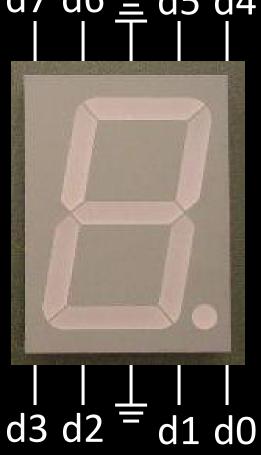

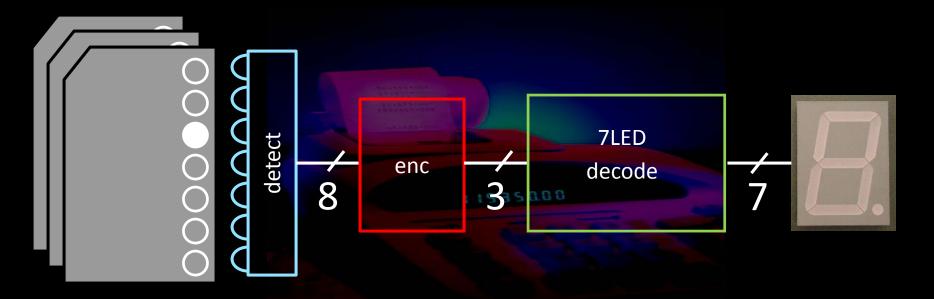

#### Decoder Example: 7-Segment LED 7-Segment LED d7 d6 = d5 d4

photons emitted when electrons fall into holes

#### Decoder Example: 7-Segment LED 7-Segment LED d7 d6 = d5 d4

photons emitted when electrons fall into holes

# $\frac{d0}{5} = \frac{234567}{d3} \frac{1}{d2} = \frac{1}{d1} \frac{1}{d0}$

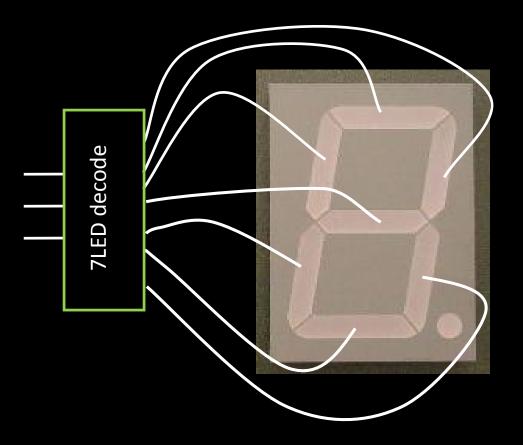

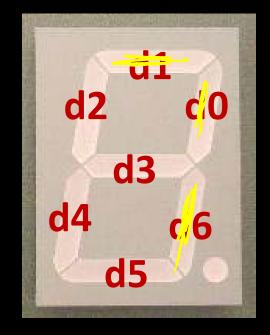

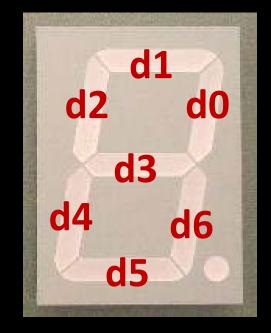

## Decoder Example: 7-Segment LED Decoder

3 inputs

encode 0 – 7 in binary

7 outputs

• one for each LED

## 7 Segment LED Decoder Implementation

| <b>b2</b> | <b>b1</b> | <b>b0</b> | <b>d6</b> | d5 | <b>d4</b> | d3 | d2 | <b>d1</b> | d0 |

|-----------|-----------|-----------|-----------|----|-----------|----|----|-----------|----|

| 0         | 0         | 0         |           |    |           |    |    |           |    |

| 0         | 0         | 1         |           |    |           |    |    |           |    |

| 0         | 1         | 0         |           |    |           |    |    |           |    |

| 0         | 1         | 1         |           |    |           |    |    |           |    |

| 1         | 0         | 0         |           |    |           |    |    |           |    |

| 1         | 0         | 1         |           |    |           |    |    |           |    |

| 1         | 1         | 0         |           |    |           |    |    |           |    |

| 1         | 1         | 1         | 1         | 0  | 0         | 0  | 0  | 1         | 1  |

## 7 Segment LED Decoder Implementation

| b2 | <b>b1</b> | <b>b0</b> | <b>d6</b> | d5 | <b>d4</b> | dЗ | d2 | <b>d1</b> | d0 |

|----|-----------|-----------|-----------|----|-----------|----|----|-----------|----|

| 0  | 0         | 0         | 1         | 1  | 1         | 0  | 1  | 1         | 1  |

| 0  | 0         | 1         | 1         | 0  | 0         | 0  | 0  | 0         | 1  |

| 0  | 1         | 0         | 0         | 1  | 1         | 1  | 0  | 1         | 1  |

| 0  | 1         | 1         | 1         | 1  | 0         | 1  | 0  | 1         | 1  |

| 1  | 0         | 0         | 1         | 0  | 0         | 1  | 1  | 0         | 1  |

| 1  | 0         | 1         | 1         | 1  | 0         | 1  | 1  | 1         | 0  |

| 1  | 1         | 0         | 1         | 1  | 1         | 1  | 1  | 1         | 0  |

| 1  | 1         | 1         | 1         | 0  | 0         | 0  | 0  | 1         | 1  |

## **Basic Building Blocks We have Seen**

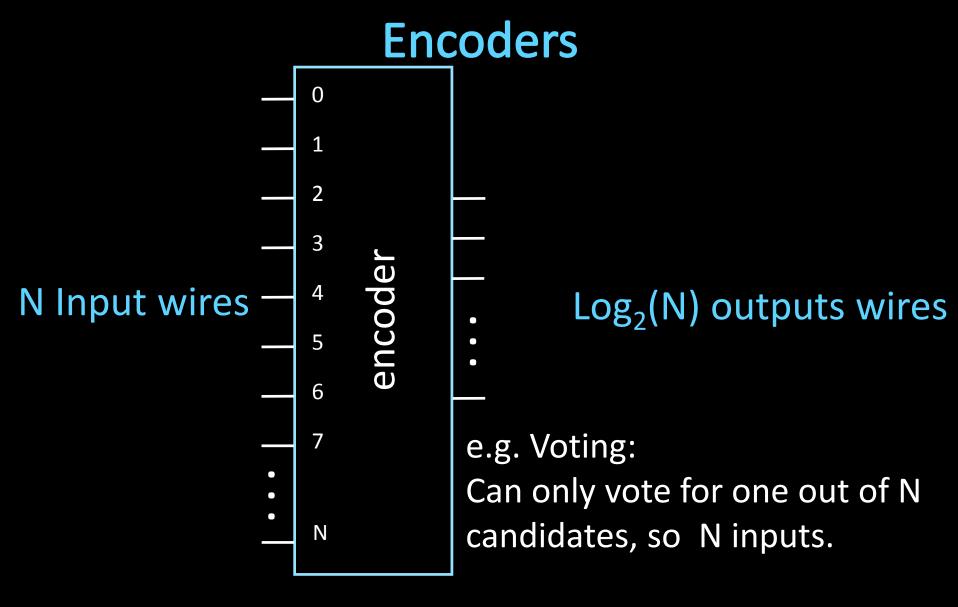

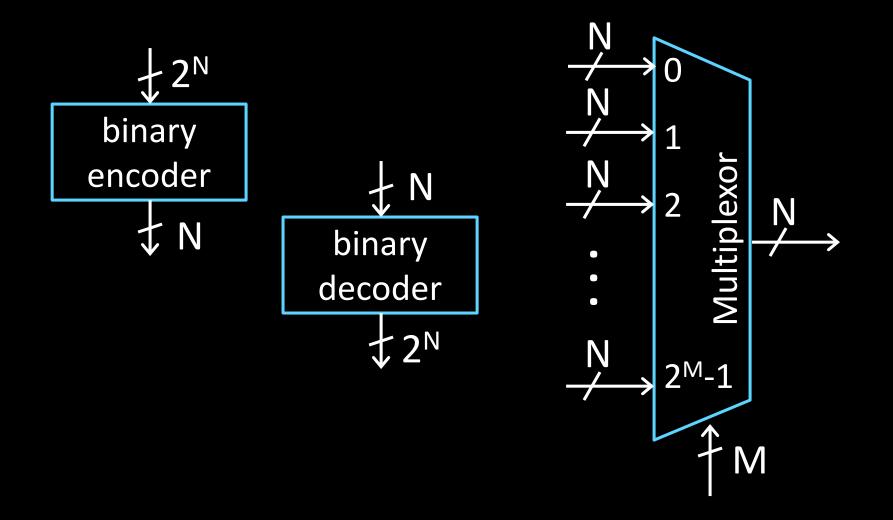

But can encode vote efficiently with binary encoding.

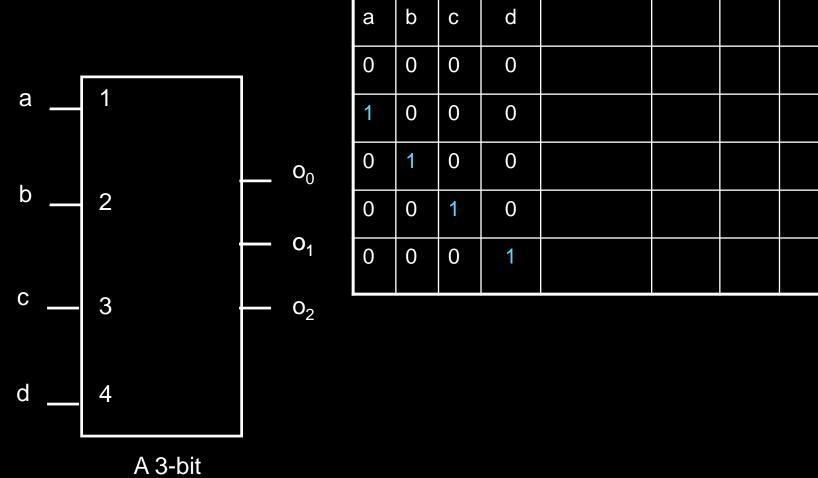

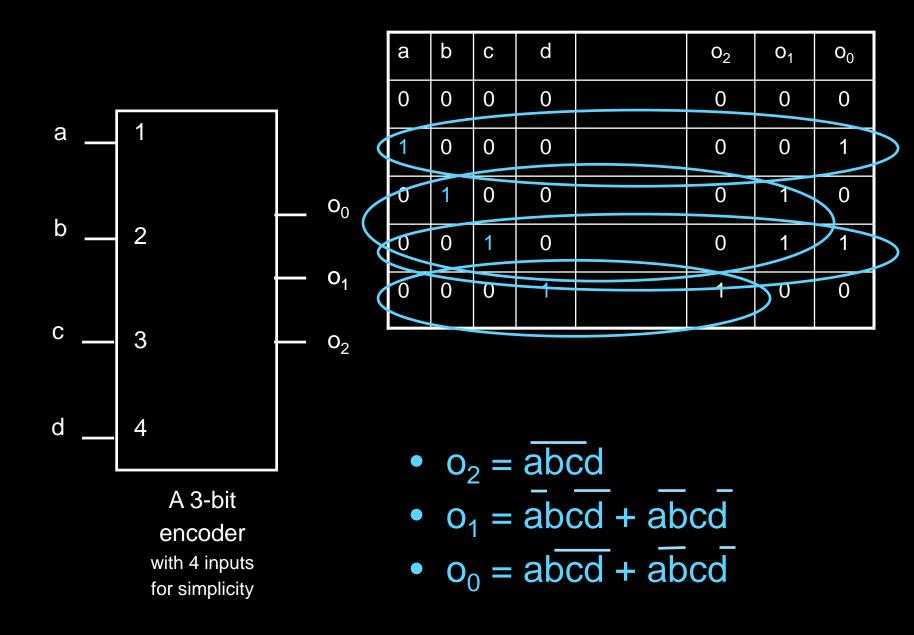

#### Example Encoder Truth Table

encoder with 4 inputs for simplicity

#### Example Encoder Truth Table

## **Basic Building Blocks Example: Voting**

Ballots

The 3410 optical scan vote reader machine

## **Basic Building Blocks We have Seen**

#### Recap

We can now build interesting devices with sensors

Using combinationial logic

We can also store data values (aka Sequential Logic)

- In state-holding elements

- Coupled with clocks

## **Goals for Today**

#### State

- How do we store one bit?

- Attempts at storing (and changing) one bit

- Set-Reset Latch

- D Latch

- D Flip-Flops

- Master-Slave Flip-Flops

- Register: storing more than one bit, N-bits

#### **Basic Building Blocks**

- Decoders and Encoders

- Finite State Machines (FSM)

- How do we design logic circuits with state?

- Types of FSMs: Mealy and Moore Machines

- Examples: Serial Adder and a Digital Door Lock

## **Goals for Today**

#### State

- How do we store one bit?

- Attempts at storing (and changing) one bit

- Set-Reset Latch

- D Latch

- D Flip-Flops

- Master-Slave Flip-Flops

- Register: storing more than one bit, N-bits

- **Basic Building Blocks**

- Decoders and Encoders

#### Finite State Machines (FSM)

- How do we design logic circuits with state?

- Types of FSMs: Mealy and Moore Machines

- Examples: Serial Adder and a Digital Door Lock

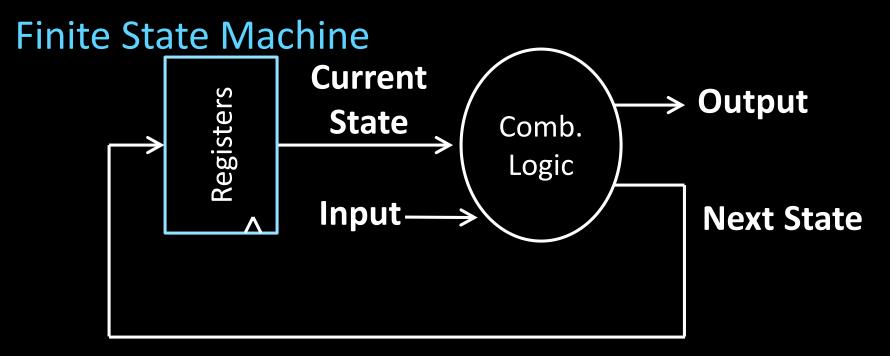

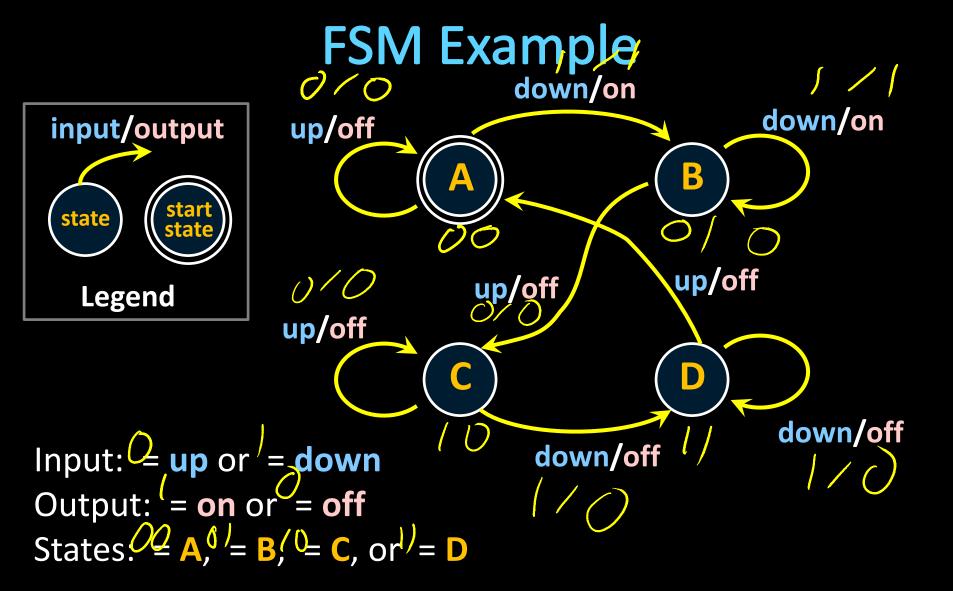

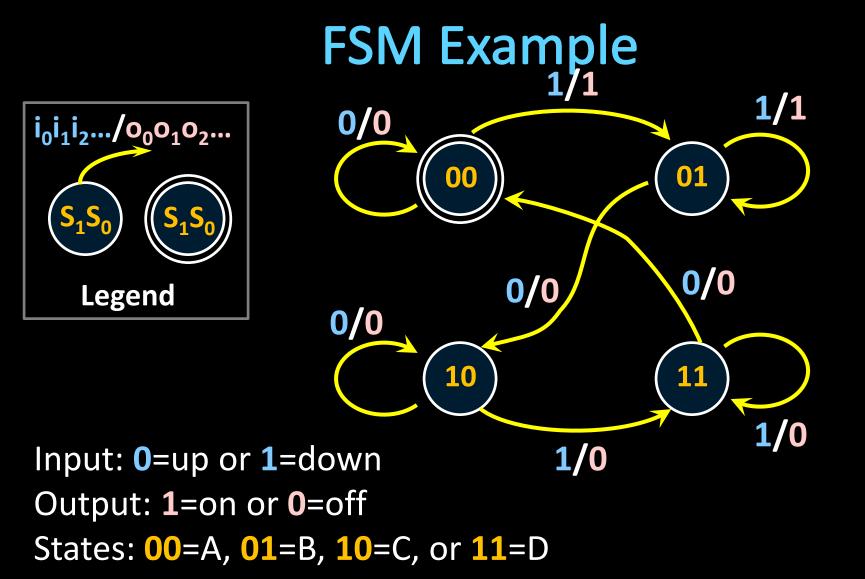

## Finite State Machines

### **Next Goal**

#### How do we design logic circuits with state?

### **Finite State Machines**

#### An electronic machine which has

- external inputs

- externally visible outputs

- internal state

#### Output and next state depend on

- inputs

- current state

## Abstract Model of FSM

#### Machine is

#### $M = (S, I, O, \delta)$

- S: Finite set of states

- *I*: Finite set of inputs

- *O*: Finite set of outputs

- $\delta$ : State transition function

Next state depends on present input and present state

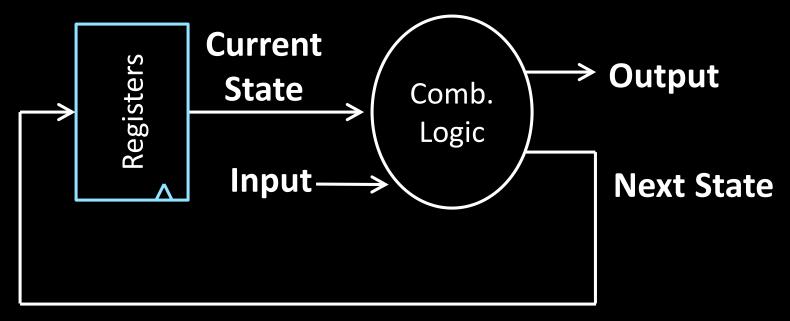

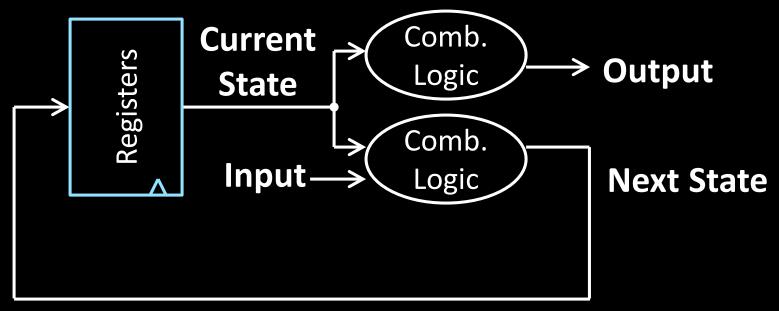

### Automata Model

- inputs from external world

- outputs to external world

- internal state

- combinational logic

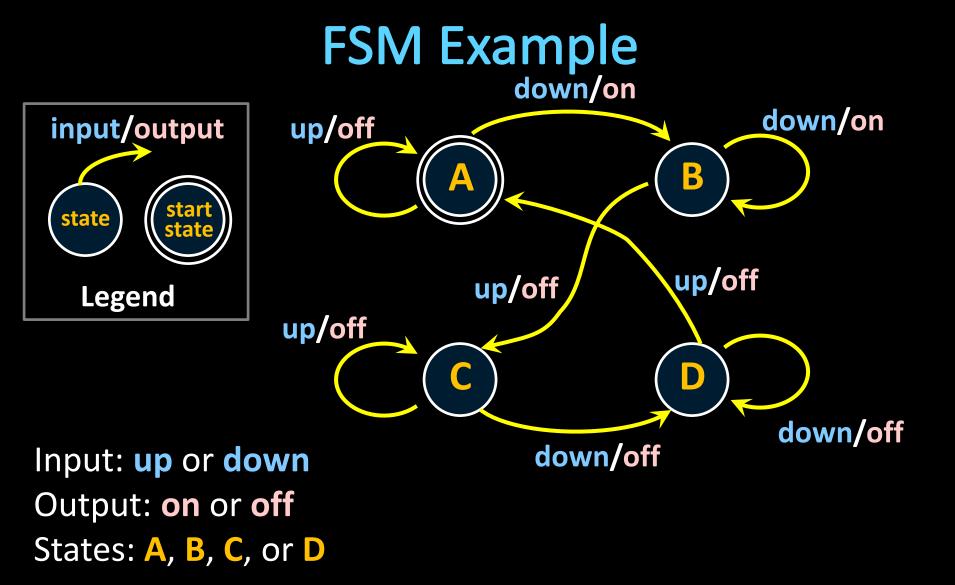

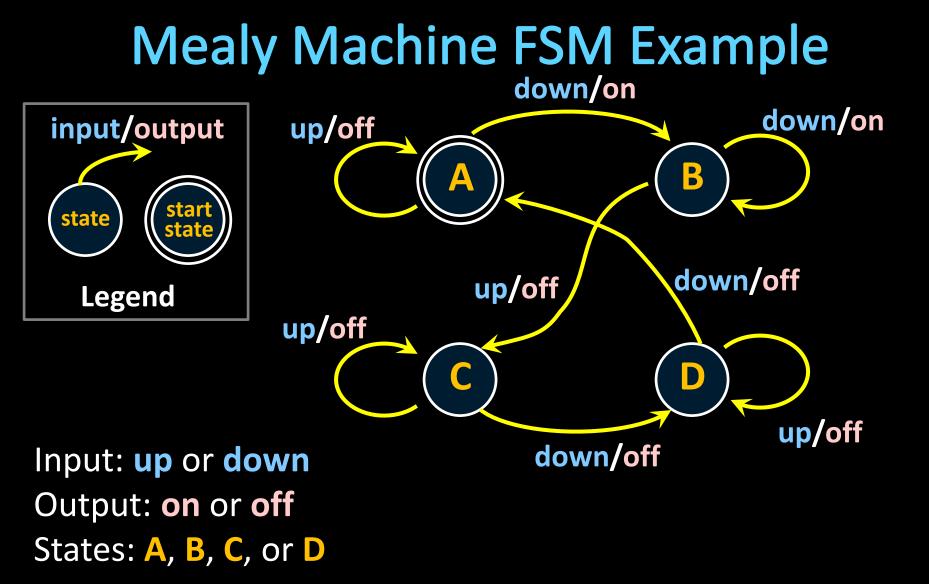

# **Mealy Machine**

**General Case: Mealy Machine**

Outputs and next state depend on both current state and input

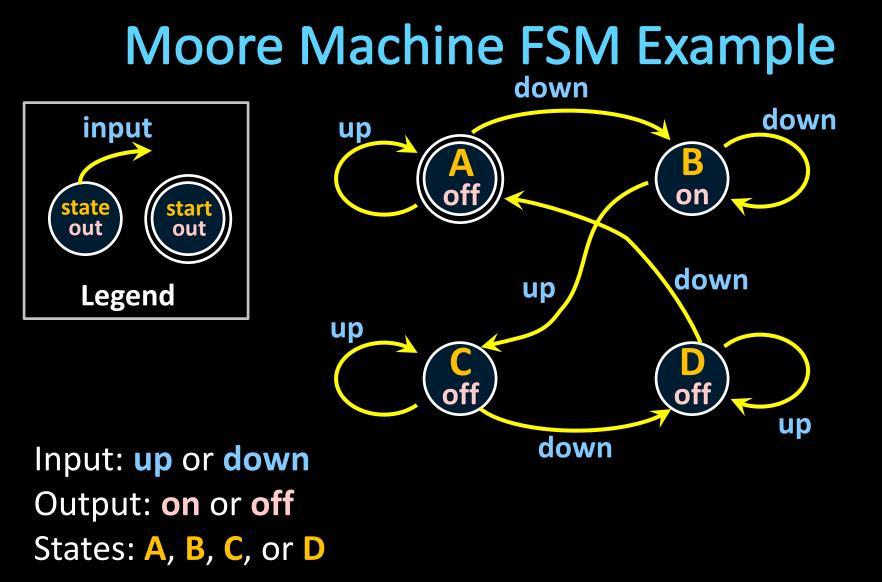

# **Moore Machine**

#### **Special Case: Moore Machine**

#### Outputs depend only on current state

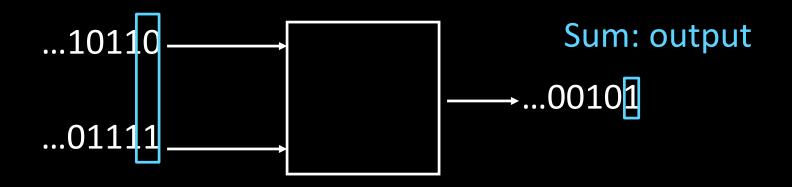

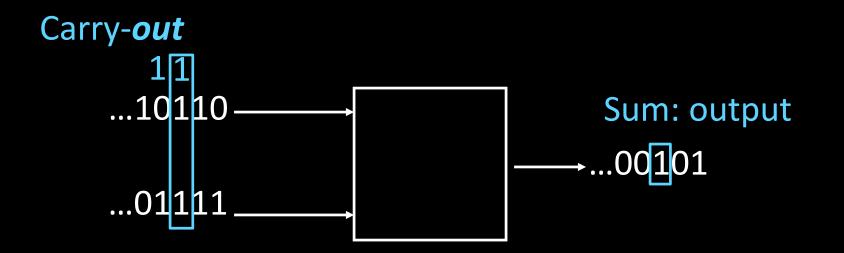

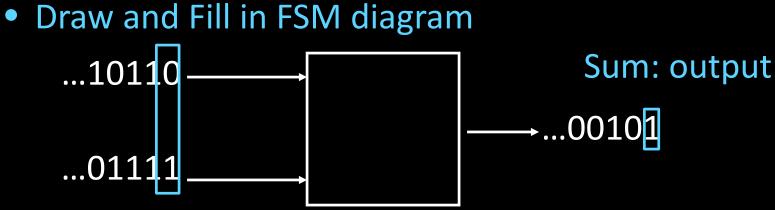

Add two infinite input bit streams

Add two infinite input bit streams

Add two infinite input bit streams

Add two infinite input bit streams

Add two infinite input bit streams

- streams are sent with least-significant-bit (lsb) first

- How many states are needed to represent FSM?

#### Strategy:

- (1) Draw a state diagram (e.g. Mealy Machine)

- (2) Write output and next-state tables

- (3) Encode states, inputs, and outputs as bits

- (4) Determine logic equations for next state and outputs

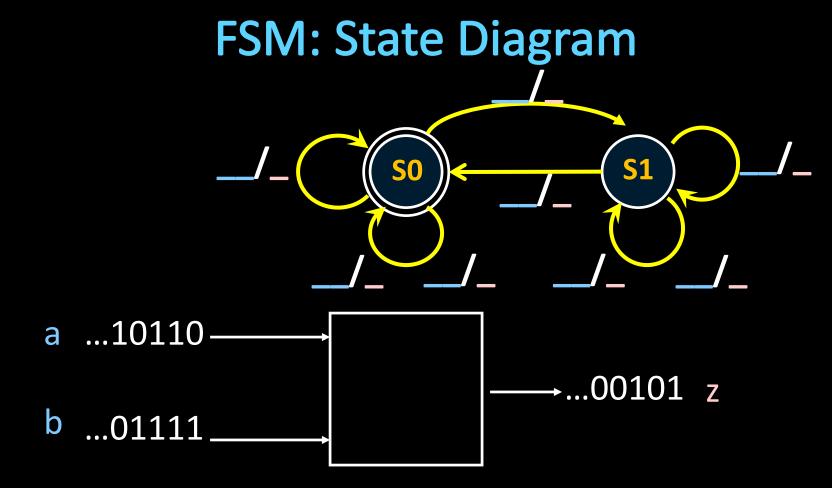

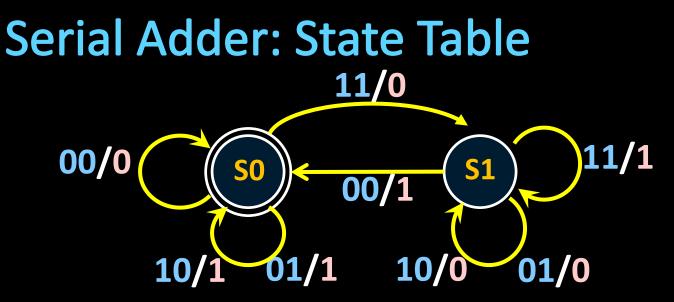

## **FSM: State Diagram**

\_\_\_\_states: Inputs: ??? and ??? Output: ???

## FSM: State Diagram

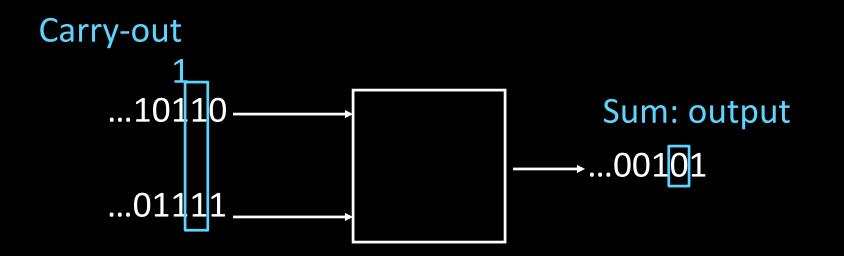

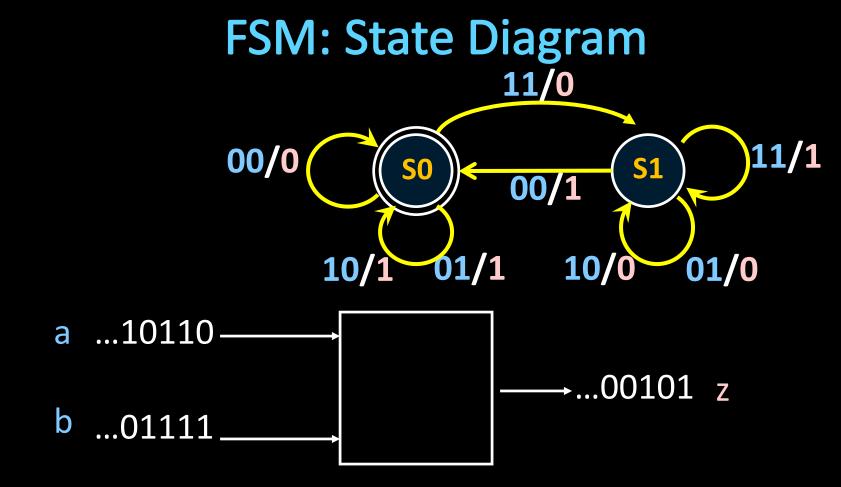

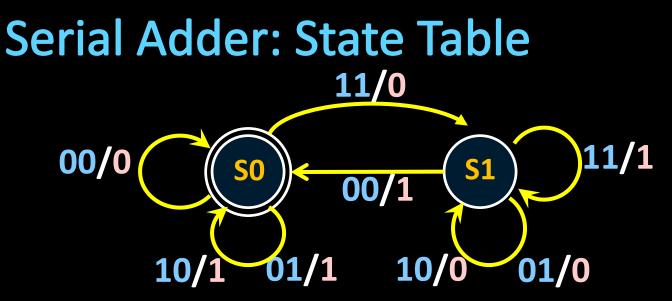

Two states: SO (no carry in), S1 (carry in) Inputs: a and b

- Output: z

- z is the sum of inputs a, b, and carry-in (one bit at a time)

- A carry-out *is* the next carry-in state.

Two states: SO (no carry in), S1 (carry in)

Inputs: a and b

Output: z

- z is the sum of inputs a, b, and carry-in (one bit at a time)

- A carry-out *is* the next carry-in state.

- Arcs labeled with input bits a and b, and output z

Two states: SO (no carry in), S1 (carry in)

Inputs: a and b

Output: z

- z is the sum of inputs a, b, and carry-in (one bit at a time)

- A carry-out *is* the next carry-in state.

- Arcs labeled with input bits a and b, and output z (Mealy Machine)

| а | b | Current<br>state | Ζ | Next<br>state |

|---|---|------------------|---|---------------|

|   |   |                  |   |               |

|   |   |                  |   |               |

|   |   |                  |   |               |

|   |   |                  |   |               |

|   |   |                  |   |               |

|   |   |                  |   |               |

|   |   |                  |   |               |

|   |   |                  |   |               |

# (2) Write down all input and state combinations

| а | b | Current<br>state | Ζ | Next<br>state |

|---|---|------------------|---|---------------|

| 0 | 0 | S0               | 0 | S0            |

| 0 | 1 | S0               | 1 | S0            |

| 1 | 0 | S0               | 1 | S0            |

| 1 | 1 | S0               | 0 | S1            |

| 0 | 0 | S1               | 1 | S0            |

| 0 | 1 | S1               | 0 | S1            |

| 1 | 0 | S1               | 0 | S1            |

| 1 | 1 | S1               | 1 | S1            |

# (2) Write down all input and state combinations

| а | b | S | Ζ | S' |

|---|---|---|---|----|

| 0 | 0 | 0 | 0 | 0  |

| 0 | 1 | 0 | 1 | 0  |

| 1 | 0 | 0 | 1 | 0  |

| 1 | 1 | 0 | 0 | 1  |

| 0 | 0 | 1 | 1 | 0  |

| 0 | 1 | 1 | 0 | 1  |

| 1 | 0 | 1 | 0 | 1  |

| 1 | 1 | 1 | 1 | 1  |

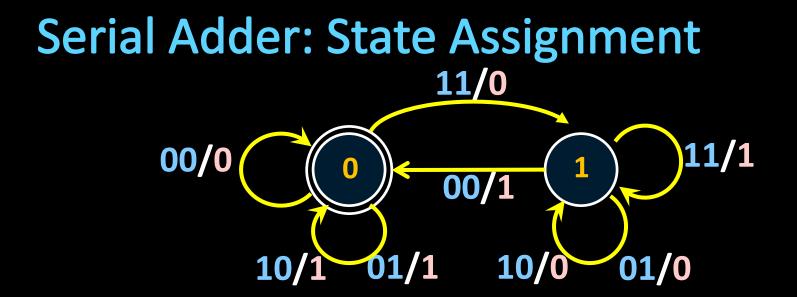

(3) Encode states, inputs, and outputs as bits

Two states, so 1-bit is sufficient

• A single flip-flop will encode the state

| а | b | S | Ζ | S' |

|---|---|---|---|----|

| 0 | 0 | 0 | 0 | 0  |

| 0 | 1 | 0 | 1 | 0  |

| 1 | 0 | 0 | 1 | 0  |

| 1 | 1 | 0 | 0 | 1  |

| 0 | 0 | 1 | 1 | 0  |

| 0 | 1 | 1 | 0 | 1  |

| 1 | 0 | 1 | 0 | 1  |

| 1 | 1 | 1 | 1 | 1  |

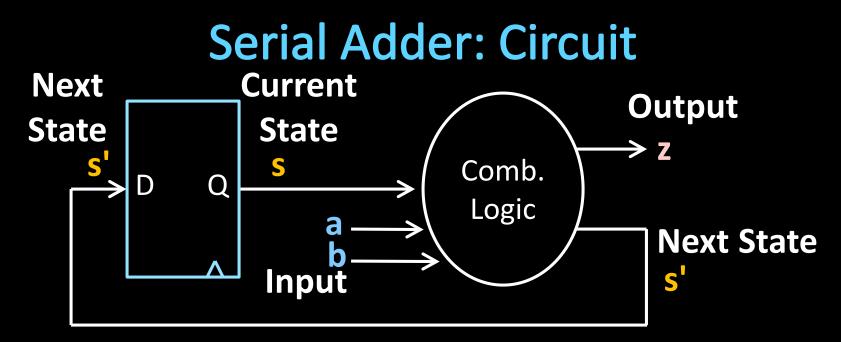

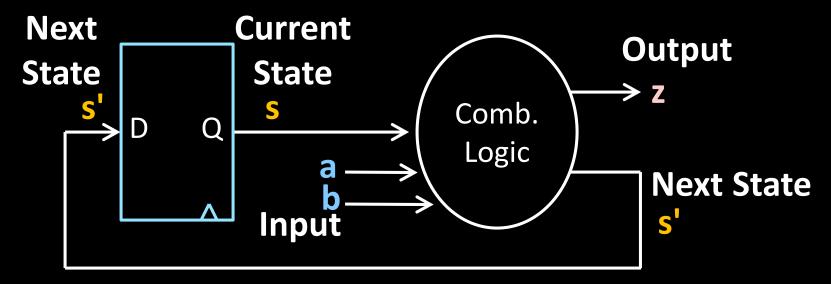

(4) Determine logic equations for next state and outputs

Combinational Logic Equations  $z = \overline{a}b\overline{s} + a\overline{b}\overline{s} + \overline{a}\overline{b}\overline{s} + abs$  $s' = ab\overline{s} + \overline{a}b\overline{s} + a\overline{b}\overline{s} + abs$

# **Sequential Logic Circuits**

$z = \overline{a}b\overline{s} + a\overline{b}s + a\overline{b}s + abs$  $s' = ab\overline{s} + \overline{a}bs + a\overline{b}s + abs$

#### Strategy:

- (1) Draw a state diagram (e.g. Mealy Machine)

- (2) Write output and next-state tables

- (3) Encode states, inputs, and outputs as bits

- (4) Determine logic equations for next state and outputs

# Summary

We can now build interesting devices with sensors

• Using combinational logic

We can also store data values

- Stateful circuit elements (D Flip Flops, Registers, ...)

- Clock to synchronize state changes

- State Machines or Ad-Hoc Circuits