# Gates and Logic: From switches to Transistors, Logic Gates and Logic Circuits

Prof. Kavita Bala and Prof. Hakim Weatherspoon CS 3410, Spring 2014

Computer Science

Cornell University

From Switches to Logic Gates to Logic Circuits

Understanding the foundations of

Computer Systems Organization and Programming

From Switches to Logic Gates to Logic Circuits

Understanding the foundations of

Computer Systems Organization and Programming

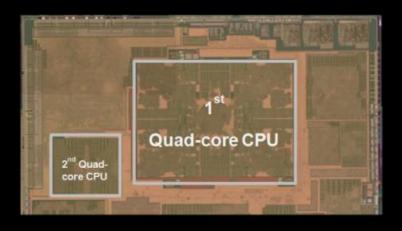

e.g. Galaxy Note 3

From Switches to Logic Gates to Logic Circuits

Understanding the foundations of

Computer Systems Organization and Programming

e.g. Galaxy Note 3

with the big.LITTLE 8-core ARM processor

From Switches to Logic Gates to Logic Circuits Understanding the foundations of

Computer Systems Organization and Programming

e.g. Galaxy Note 3

### with the big.LITTLE 8-core ARM processor

|               | big Quad Core   | LITTLE Quad Core  |

|---------------|-----------------|-------------------|

| Architecture  | ARM v7a         | ARM v7a           |

| Process       | Samsung 28nm    | Samsung 28nm      |

| Frequency     | 200MHz~1.8GHz+  | 200MHz~1.2GHz     |

| Area          | 19mm2           | 3.8mm2            |

| Power-ratio   | 1               | 0.17              |

| L1 Cache Size | 32 KB I/D Cache | 32 KB I/D Cache   |

| L2 Cache Size | 2 MB Data Cache | 512 KB Data Cache |

From Switches to Logic Gates to Logic Circuits

### **Logic Gates**

- From switches

- Truth Tables

### Logic Circuits

- Identity Laws

- From Truth Tables to Circuits (Sum of Products)

### **Logic Circuit Minimization**

- Algebraic Manipulations

- Truth Tables (Karnaugh Maps)

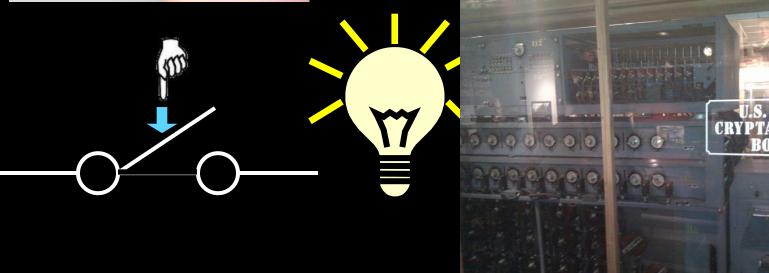

Transistors (electronic switch)

### A switch

- Acts as a conductor or insulator

- Can be used to build amazing things...

The Bombe used to break the German Enigma machine during World War II

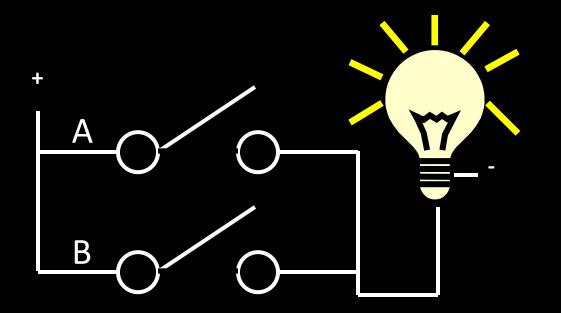

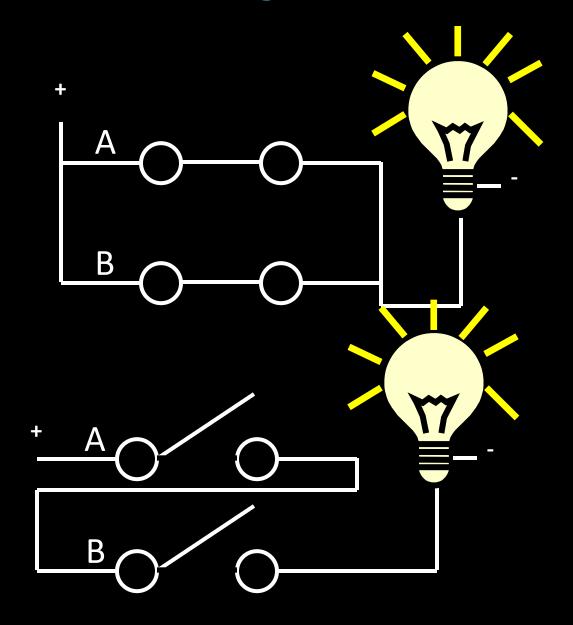

#### Truth Table

| Α   | В   | Light |

|-----|-----|-------|

| OFF | OFF |       |

| OFF | ON  |       |

| ON  | OFF |       |

| ON  | ON  |       |

#### Truth Table

| Α   | В   | Light |

|-----|-----|-------|

| OFF | OFF | OFF   |

| OFF | ON  | ON    |

| ON  | OFF | ON    |

| ON  | ON  | ON    |

| Α   | В   | Light |

|-----|-----|-------|

| OFF | OFF |       |

| OFF | ON  |       |

| ON  | OFF |       |

| ON  | ON  |       |

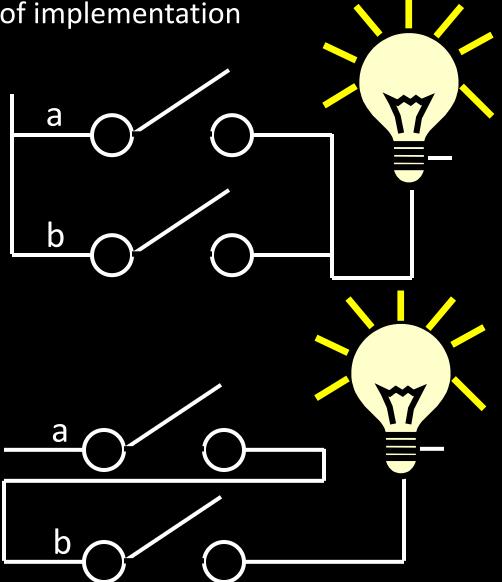

### Either (OR)

Truth Table

| А   | В   | Light |

|-----|-----|-------|

| OFF | OFF | OFF   |

| OFF | ON  | ON    |

| ON  | OFF | ON    |

| ON  | ON  | ON    |

### Both (AND)

| Α   | В   | Light |

|-----|-----|-------|

| OFF | OFF | OFF   |

| OFF | ON  | OFF   |

| ON  | OFF | OFF   |

| ON  | ON  | ON    |

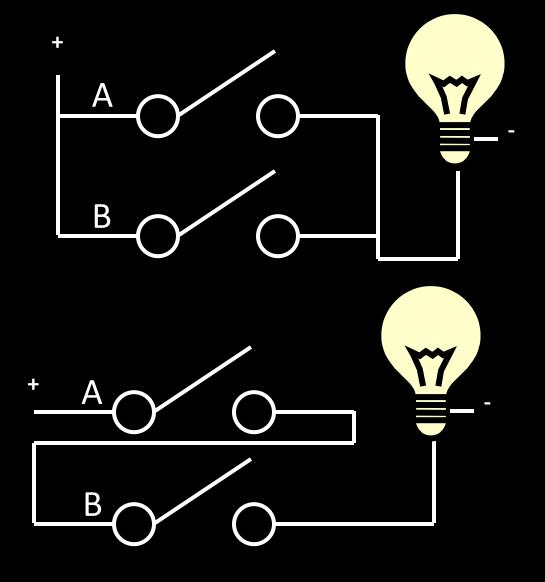

### Either (OR)

Truth Table

| А   | В   | Light |

|-----|-----|-------|

| OFF | OFF | OFF   |

| OFF | ON  | ON    |

| ON  | OFF | ON    |

| ON  | ON  | ON    |

### Both (AND)

| Α   | В   | Light |

|-----|-----|-------|

| OFF | OFF | OFF   |

| OFF | ON  | OFF   |

| ON  | OFF | OFF   |

| ON  | ON  | ON    |

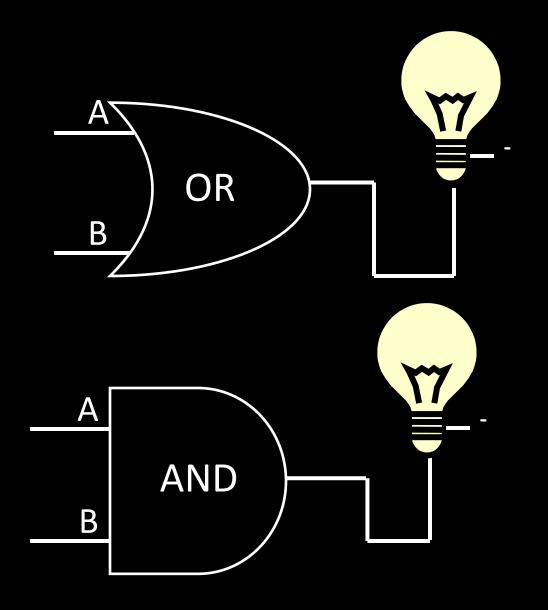

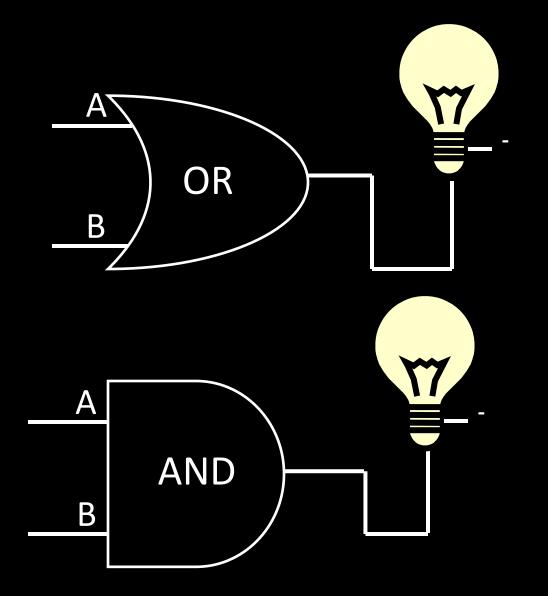

### Either (OR)

Truth Table

| Α | В | Light |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 1     |

0 = OFF 1 = ON

### Both (AND)

| Α | В | Light |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 0     |

| 1 | 0 | 0     |

| 1 | 1 | 1     |

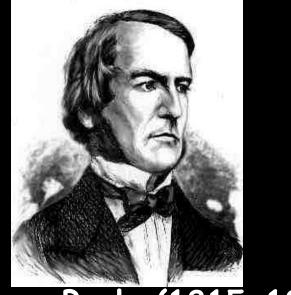

George Boole, (1815-1864)

### Did you know?

George Boole Inventor of the idea of logic gates. He was born in Lincoln, England and he was the son of a shoemaker in a low class family.

## **Takeaway**

Binary (two symbols: true and false) is the basis of Logic Design

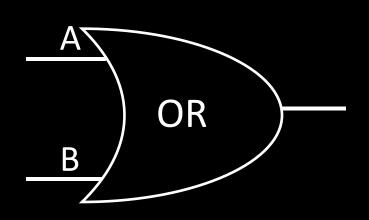

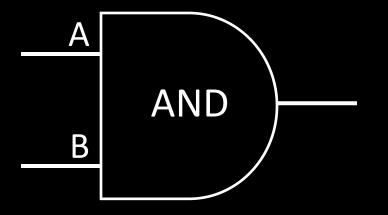

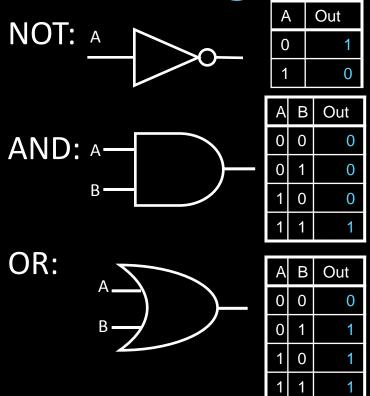

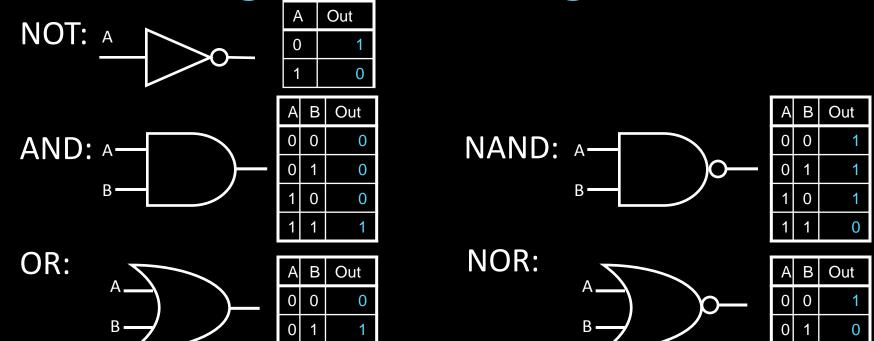

## **Building Functions: Logic Gates**

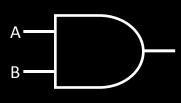

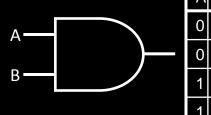

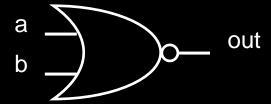

#### **Logic Gates**

- digital circuit that either allows a signal to pass through it or not.

- Used to build logic functions

- There are seven basic logic gates:

AND, OR, **NOT**, NAND (not AND), NOR (not OR), XOR, and XNOR (not XOR) [later]

## **Building Functions: Logic Gates**

#### **Logic Gates**

- digital circuit that either allows a signal to pass through it or not.

- Used to build logic functions

- There are seven basic logic gates:

AND, OR, **NOT**, NAND (not AND), NOR (not OR), XOR, and XNOR (not XOR) [later]

## **Building Functions: Logic Gates**

#### **Logic Gates**

- digital circuit that either allows a signal to pass through it or not.

- Used to build logic functions

- There are seven basic logic gates:

AND, OR, **NOT**, NAND (not AND), NOR (not OR), XOR, and XNOR (not XOR) [later]

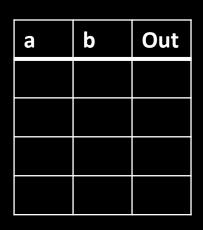

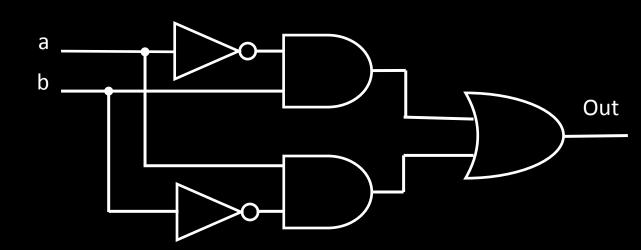

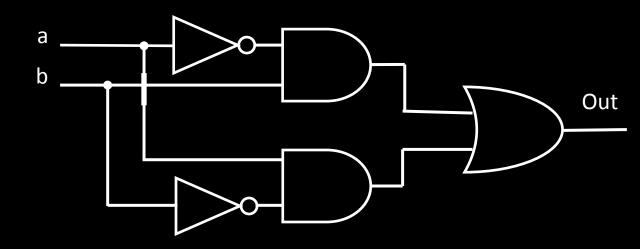

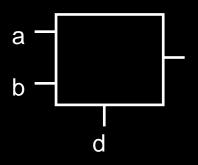

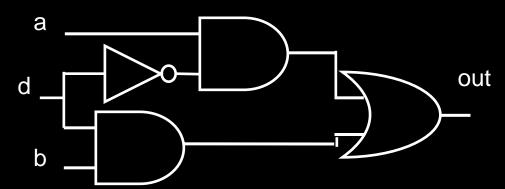

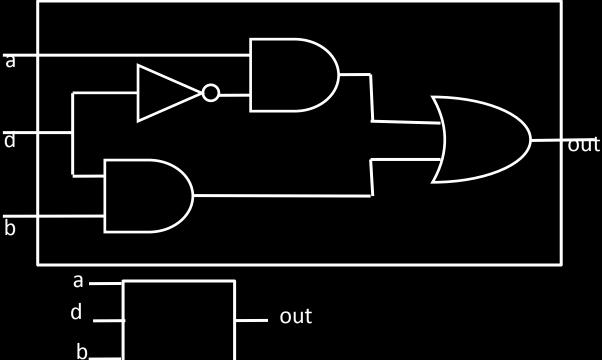

## Activity#1: Logic Gates

Fill in the truth table, given the following Logic Circuit made from Logic AND, OR, and NOT gates. What does the logic circuit do?

## Activity#1: Logic Gates

XOR: out = 1 if a or b is 1, but not both;

out = 0 otherwise.

out = 1, only if

$$a = 1$$

AND  $b = 0$

OR  $a = 0$  AND  $b = 1$

| a | b | Out |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

## Activity#1: Logic Gates

XOR: out = 1 if a or b is 1, but not both; out = 0 otherwise.

out = 1, only if

$$a = 1$$

AND  $b = 0$

OR  $a = 0$  AND  $b = 1$

| а | b | Out |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

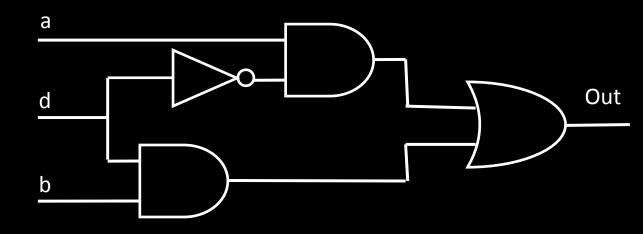

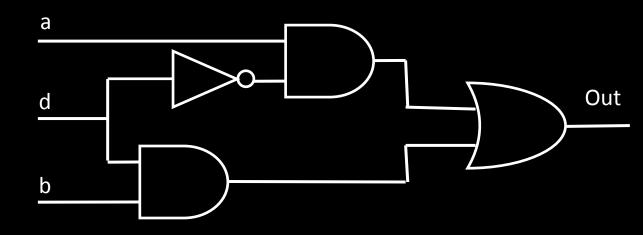

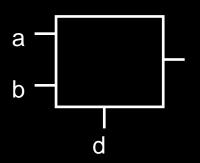

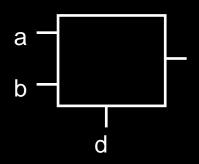

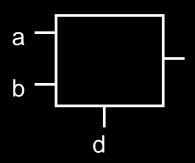

## **Activity#2: Logic Gates**

Fill in the truth table, given the following Logic Circuit made from Logic AND, OR, and NOT gates. What does the logic circuit do?

| а | b | d | Out |

|---|---|---|-----|

| 0 | 0 | 0 |     |

| 0 | 0 | 1 |     |

| 0 | 1 | 0 |     |

| 0 | 1 | 1 |     |

| 1 | 0 | 0 |     |

| 1 | 0 | 1 |     |

| 1 | 1 | 0 |     |

| 1 | 1 | 1 |     |

## Activity#2: Logic Gates

Multiplexor: select (d) between two inputs (a and b) and set one as the output (out)?

| а | b | d | Out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1   |

From Switches to Logic Gates to Logic Circuits

### **Logic Gates**

- From switches

- Truth Tables

### **Logic Circuits**

- Identity Laws

- From Truth Tables to Circuits (Sum of Products)

### **Logic Circuit Minimization**

- Algebraic Manipulations

- Truth Tables (Karnaugh Maps)

Transistors (electronic switch)

### **Next Goal**

Given a Logic function, create a Logic Circuit that implements the Logic Function...

...and, with the minimum number of logic gates

Fewer gates: A cheaper (\$\$\$) circuit!

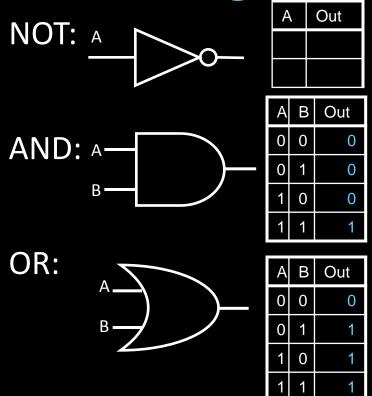

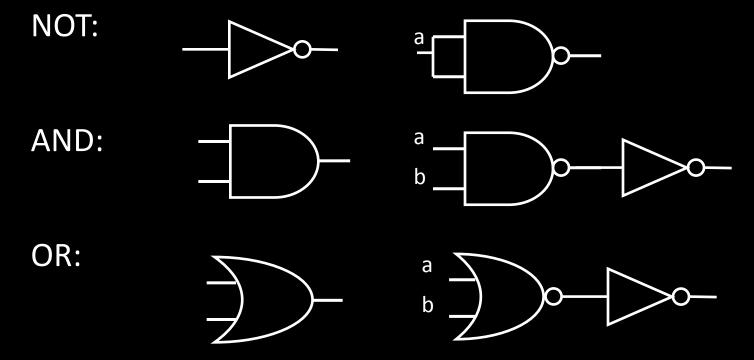

# **Logic Gates**

| Α | Out |  |

|---|-----|--|

| 0 | 1   |  |

| 1 | 0   |  |

AND:

| Α | В | Out |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

OR:

| Α | В | Out |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

XOR:

| Α | В | Out |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

# **Logic Gates**

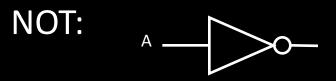

NOT:

| Α | Out |

|---|-----|

| 0 | 1   |

| 1 | 0   |

AND:

| В | Out |  |

|---|-----|--|

| 0 | 0   |  |

| 1 | 0   |  |

| 0 | 0   |  |

| 1 | 1   |  |

| N | A | N | D: |

|---|---|---|----|

|   |   |   |    |

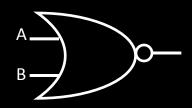

| Α | В | Out |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

OR:

| Α | В | Out |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

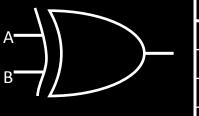

NOR:

| Α | В | Out |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

XOR:

| Α | В | Out |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

XNOR:

| Α | В | Out |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

## **Logic Equations**

#### NOT:

• out =

$$\bar{a}$$

=  $|a|$  =  $-a$

#### AND:

• out = a · b = a & b = a ∧ b

#### OR:

• out =  $a + b = a | b = a \lor b$

#### XOR:

• out =  $a \oplus b = a\overline{b} + \overline{a}b$

#### **Logic Equations**

- Constants: true = 1, false = 0

- Variables: a, b, out, ...

- Operators (above): AND, OR, NOT, etc.

## **Logic Equations**

NOT:

• out =

$$\bar{a}$$

= !a =  $\neg a$

AND:

• out =  $a \cdot b$  =  $a \& b = a \land b$  • out =  $a \cdot b$  = !( $a \& b$ ) =  $\neg (a \land b)$

OR:

• out =  $a + b$  =  $a \mid b = a \lor b$  • out =  $a + b$  = !( $a \mid b$ ) =  $\neg (a \lor b)$

XOR:

• out =  $a \oplus b = a\bar{b} + \bar{a}b$  • out =  $a \oplus b = ab + \bar{a}b$

#### **Logic Equations**

- Constants: true = 1, false = 0

- Variables: a, b, out, ...

- Operators (above): AND, OR, NOT, etc.

### Identities useful for manipulating logic equations

$$a + 0 =$$

$$a + 1 =$$

$$a + \bar{a} =$$

$$a \cdot 0 =$$

$$a \cdot 1 =$$

$$a \cdot \bar{a} =$$

Identities useful for manipulating logic equations

$$a + 0 = a$$

$$a + 1 = 1$$

$$a + \bar{a} = 1$$

$$a \cdot 0 = 0$$

$$a \cdot 1 = a$$

$$a \cdot \bar{a} = 0$$

Identities useful for manipulating logic equations

$$\overline{(a+b)} =$$

$$\overline{(a \cdot b)} =$$

$$a + ab =$$

$$a(b+c) =$$

$$\overline{a(b+c)} =$$

Identities useful for manipulating logic equations

$$\overline{(a+b)} = \overline{a} \cdot \overline{b}$$

$$\overline{(a+b)} = \overline{a} + \overline{b}$$

$$A \longrightarrow A \longrightarrow A$$

$$B \longrightarrow A$$

$$A \longrightarrow A$$

$$B \longrightarrow A$$

$$B \longrightarrow A$$

$$A \longrightarrow A$$

$$B \longrightarrow A$$

$$B \longrightarrow A$$

$$B \longrightarrow A$$

$$A + ab = a$$

$$a(b+c) = ab + ac$$

$$\overline{a(b+c)} = \overline{a} + \overline{b} \cdot \overline{c}$$

## Activity #2: Identities

$$a + 0 = a$$

$a + 1 = 1$

$a + \bar{a} = 1$

$a = 0$

$a = 0$

$a = 0$

$$\overline{(a + b)} = \overline{a} \, \overline{b}$$

$$(a b) = \overline{a} + \overline{b}$$

$$a + a b = a$$

$$\underline{a(b+c)} = \overline{a} + \overline{b} \cdot \overline{c}$$

$$\overline{a(b+c)} = \overline{a} + \overline{b} \cdot \overline{c}$$

Show that the Logic equations below are equivalent.

$$(a+b)(a+c) = a + bc$$

$$(a+b)(a+c) =$$

## Activity #2: Identities

$$a + 0 = a$$

$a + 1 = 1$

$a + \bar{a} = 1$

$a = 0$

$a = 0$

$a = 0$

$a = 0$

$$\frac{\overline{(a + b)}}{\overline{(a b)}} = \overline{a} \, \overline{b}$$

$$a + a b = a$$

$$a(b+c) = ab + ac$$

$$\overline{a(b+c)} = \overline{a} + \overline{bc}$$

Show that the Logic equations below are equivalent.

$$(a+b)(a+c) = a + bc$$

$$(a+b)(a+c) = aa + ab + ac + bc$$

=  $a + a(b+c) + bc$

=  $a(1 + (b+c)) + bc$

=  $a + bc$

Logic Manipulation

functions: gates ←> truth tables ←> equations

Example: (a+b)(a+c) = a + bc

| а | b | С |  |  |  |

|---|---|---|--|--|--|

| 0 | 0 | 0 |  |  |  |

| 0 | 0 | 1 |  |  |  |

| 0 | 1 | 0 |  |  |  |

| 0 | 1 | 1 |  |  |  |

| 1 | 0 | 0 |  |  |  |

| 1 | 0 | 1 |  |  |  |

| 1 | 1 | 0 |  |  |  |

| 1 | 1 | 1 |  |  |  |

Logic Manipulation

functions: gates ↔ truth tables ↔ equations

Example: (a+b)(a+c) = a + bc

| а | b | С | a+b | a+c | LHS | bc | RHS |

|---|---|---|-----|-----|-----|----|-----|

| 0 | 0 | 0 | 0   | 0   | 0   | 0  | 0   |

| 0 | 0 | 1 | 0   | 1   | 0   | 0  | 0   |

| 0 | 1 | 0 | 1   | 0   | 0   | 0  | 0   |

| 0 | 1 | 1 | 1   | 1   | 1   | 1  | 1   |

| 1 | 0 | 0 | 1   | 1   | 1   | 0  | 1   |

| 1 | 0 | 1 | 1   | 1   | 1   | 0  | 1   |

| 1 | 1 | 0 | 1   | 1   | 1   | 0  | 1 / |

| 1 | 1 | 1 | 1   | 1   | 1   | 1  | 1   |

## **Takeaway**

Binary (two symbols: true and false) is the basis of Logic Design

More than one Logic Circuit can implement same Logic function. Use Algebra (Identities) or Truth Tables to show equivalence.

## **Goals for Today**

From Switches to Logic Gates to Logic Circuits

#### Logic Gates

- From switches

- Truth Tables

#### Logic Circuits

- Identity Laws

- From Truth Tables to Circuits (Sum of Products)

#### **Logic Circuit Minimization**

- Algebraic Manipulations

- Truth Tables (Karnaugh Maps)

Transistors (electronic switch)

## **Next Goal**

How to standardize minimizing logic circuits?

## Logic Minimization

How to implement a desired logic function?

| а | b | С | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 1   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 0   |

| 1 | 0 | 1 | 1   |

| 1 | 1 | 0 | 0   |

| 1 | 1 | 1 | 0   |

## **Logic Minimization**

How to implement a desired logic function?

| а | b | С | out | minterm            |

|---|---|---|-----|--------------------|

| 0 | 0 | 0 | 0   | ā b c              |

| 0 | 0 | 1 | 1   | ā b c              |

| 0 | 1 | 0 | 0   | <u>a</u> b c       |

| 0 | 1 | 1 | 1   | a b c              |

| 1 | 0 | 0 | 0   | a <u>b c</u>       |

| 1 | 0 | 1 | 1   | a $\overline{b}$ c |

| 1 | 1 | 0 | 0   | a b $\overline{c}$ |

| 1 | 1 | 1 | 0   | a b c              |

- 1) Write minterms

- 2) sum of products:

- OR of all minterms where out=1

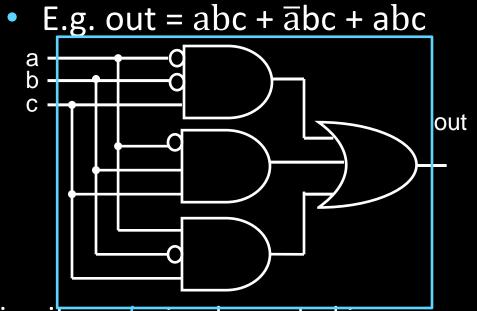

## **Logic Minimization**

How to implement a desired logic function?

| а | b | С | out | minterm            | 1  |

|---|---|---|-----|--------------------|----|

| 0 | 0 | 0 | 0   | ā b c              | 2, |

| 0 | 0 | 1 | 1   | a b c              |    |

| 0 | 1 | 0 | 0   | a b c              |    |

| 0 | 1 | 1 | 1   | a b c              |    |

| 1 | 0 | 0 | 0   | a b c              |    |

| 1 | 0 | 1 | 1   | a b c              |    |

| 1 | 1 | 0 | 0   | a b $\overline{c}$ |    |

| 1 | 1 | 1 | 0   | a b c              |    |

- 1) Write minterms

- 2) sum of products:

OR of all minterms where out=1

corollary: *any* combinational circuit *can be* implemented in two levels of logic (ignoring inverters)

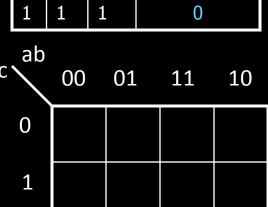

## Karnaugh Maps

#### How does one find the most efficient equation?

- Manipulate algebraically until...?

- Use Karnaugh maps (optimize visually)

- Use a software optimizer

#### For large circuits

Decomposition & reuse of building blocks

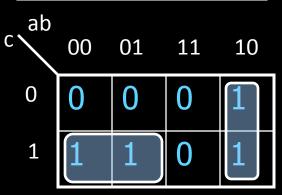

## Minimization with Karnaugh maps (1)

■ out =

| а | b | С | out |  |

|---|---|---|-----|--|

| 0 | 0 | 0 | 0   |  |

| 0 | 0 | 1 | 1   |  |

| 0 | 1 | 0 | 0   |  |

| 0 | 1 | 1 | 1   |  |

| 1 | 0 | 0 | 1   |  |

| J | 0 | 1 | 1   |  |

| 1 | 1 | 0 | 0   |  |

| 1 | 1 | 1 | 0   |  |

|   |   |   |     |  |

## Minimization with Karnaugh maps (2)

| а | b | С | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 1   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 1   |

| 1 | 1 | 0 | 0   |

| 1 | 1 | 1 | 0   |

- Sum of minterms yields

- out =  $\overline{abc}$  +  $\overline{abc}$  +  $\overline{abc}$  +  $\overline{abc}$

Karnaugh maps identify which inputs are (ir)relevant to the output

## Minimization with Karnaugh maps (2)

| а | b | С | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 1   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 1   |

| 1 | 1 | 0 | 0   |

| 1 | 1 | 1 | 0   |

• out =

$$\overline{abc}$$

+  $\overline{abc}$  +  $\overline{abc}$  +  $\overline{abc}$

Karnaugh maps identify which inputs are (ir)relevant to the output

## Minimization with Karnaugh maps (2)

| а | b | С | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 1   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 1   |

| 1 | 1 | 0 | 0   |

| 1 | 1 | 1 | 0   |

- Sum of minterms yields

- out =  $\overline{abc}$  +  $\overline{abc}$  +  $\overline{abc}$  +  $\overline{abc}$

- Karnaugh map minimization

- Cover all 1's

- Group adjacent blocks of 2<sup>n</sup>

1's that yield a rectangular shape

- Encode the common features of the rectangle

- out =

# Karnaugh Minimization Tricks (1)

- Minterms can overlap

- out =

- Minterms can span 2, 4, 8 or more cells

- out =

# Karnaugh Minimization Tricks (1)

• out =

$$b\overline{c} + a\overline{c} + ab$$

- Minterms can span 2, 4, 8 or more cells

- out =  $\overline{c}$  + ab

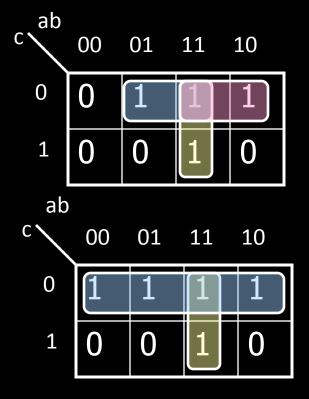

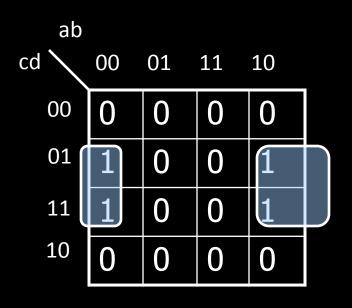

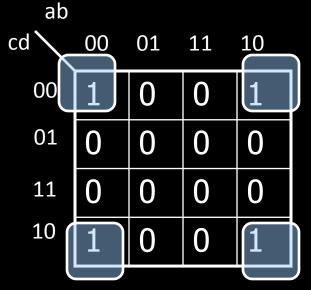

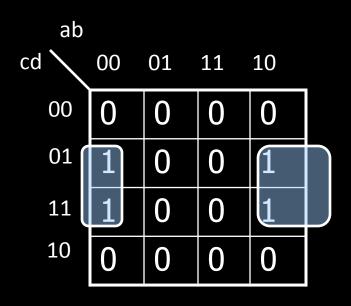

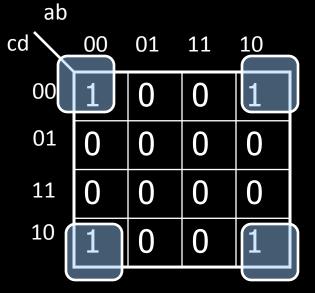

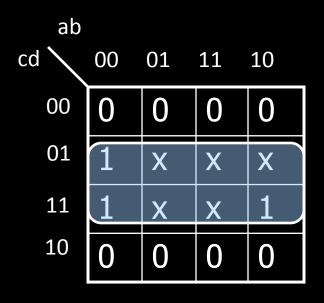

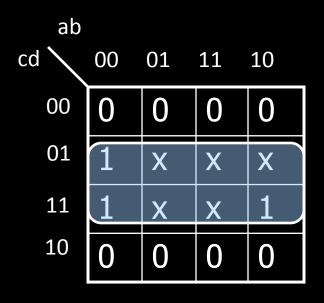

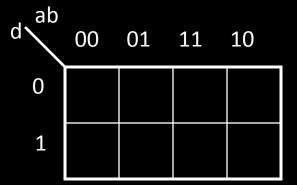

## **Karnaugh Minimization Tricks (2)**

The map wraps around

• out =

## Karnaugh Minimization Tricks (2)

The map wraps around

• out =  $\overline{b}d$

• out =  $\overline{b}$   $\overline{d}$

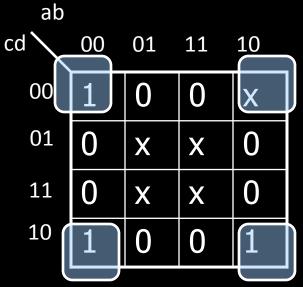

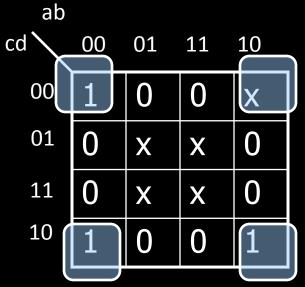

## Karnaugh Minimization Tricks (3)

"Don't care" values can be interpreted individually in whatever way is convenient

- assume all x's = 1

- out =

- assume middle x's = 0

- assume 4<sup>th</sup> column x = 1

- out =

## Karnaugh Minimization Tricks (3)

"Don't care" values can be interpreted individually in whatever way is convenient

- assume all x's = 1

- out = d

- assume middle x's = 0

- assume 4<sup>th</sup> column x = 1

- out =  $\overline{b}$   $\overline{d}$

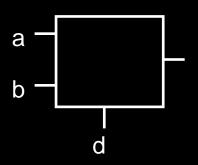

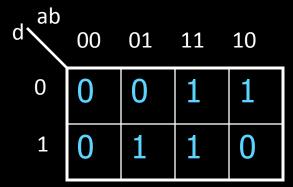

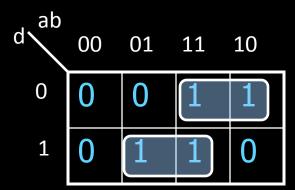

## Multiplexer

| а | b | d | out |

|---|---|---|-----|

| 0 | 0 | 0 |     |

| 0 | 0 | 1 |     |

| 0 | 1 | 0 |     |

| 0 | 1 | 1 |     |

| 1 | 0 | 0 |     |

| 1 | 0 | 1 |     |

| 1 | 1 | 0 |     |

| 1 | 1 | 1 |     |

A multiplexer selects between multiple inputs

- out = a, if d = 0

- out = b, if d = 1

Build truth table

Minimize diagram

Derive logic diagram

| а | b | d | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1   |

• Build a truth table out =  $\overline{a}bd + a\overline{b}\overline{d} + ab\overline{d} + abd$

| a | b | d | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1   |

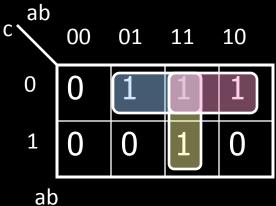

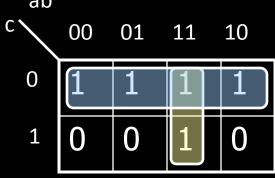

Build the Karnaugh map

| a | b | d | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1   |

Build the Karnaugh map

| а | b | d | out |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1   |

Derive Minimal Logic Equation

• out =  $a\bar{d}$  + bd

## **Takeaway**

Binary (two symbols: true and false) is the basis of Logic Design

More than one Logic Circuit can implement same Logic function. Use Algebra (Identities) or Truth Tables to show equivalence.

Any logic function can be implemented as "sum of products". Karnaugh Maps minimize number of gates.

#### **Administrivia**

#### **Dates to keep in Mind**

- Prelims: Tue Mar 4<sup>th</sup> and Thur May 1<sup>st</sup>

- Lab 1: Due Fri Feb 14<sup>th</sup> before Winter break

- Proj2: Due Fri Mar 28<sup>th</sup> before Spring break

- Final Project: Due when final would be (not known until Feb 14<sup>th</sup>)

#### Lab Sections (start *this week; today*)

| T | 2:55 – 4:10pm     | Carpenter Hall 104 (Blue Room) |

|---|-------------------|--------------------------------|

| W | 8:40—9:55am       | Carpenter Hall 104 (Blue Room) |

| W | 11:40am – 12:55pm | Carpenter Hall 104 (BlueRoom)  |

| W | 3:35 – 4:50pm     | Carpenter Hall 104 (Blue Room) |

| W | 7:30—8:45pm       | Carpenter Hall 235 (Red Room)  |

| R | 8:40 – 9:55pm     | Carpenter Hall 104 (Blue Room) |

| R | 11:40 – 12:55pm   | Carpenter Hall 104 (Blue Room) |

| R | 2:55 – 4:10pm     | Carpenter Hall 104 (Blue Room) |

| F | 8:40 – 9:55am     | Carpenter Hall 104 (Blue Room) |

| F | 11:40am – 12:55pm | Upson B7                       |

| F | 2:55 – 4:10pm     | Carpenter Hall 104 (Blue Room) |

- Labs are separate than lecture and homework

- Bring laptop to Labs

- This week: intro to logisim and building an adder

## iClicker

Attempt to balance the iClicker graph

#### Register iClicker

- http://atcsupport.cit.cornell.edu/pollsrvc/

- iClicker GO

http://pollinghelp.cit.cornell.edu/iclicker-go/#students

## **Goals for Today**

#### From Transistors to Gates to Logic Circuits

#### **Logic Gates**

- From transistors

- Truth Tables

#### Logic Circuits

- Identity Laws

- From Truth Tables to Circuits (Sum of Products)

#### Logic Circuit Minimization

- Algebraic Manipulations

- Truth Tables (Karnaugh Maps)

#### Transistors (electronic switch)

# Activity#1 How do we build *electronic* switches?

#### **Transistors:**

- 6:10 minutes (watch from from 41s to 7:00)

- http://www.youtube.com/watch?v=QO5FgM7MLGg

Fill our Transistor Worksheet with info from Video

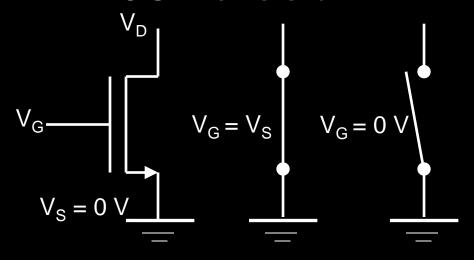

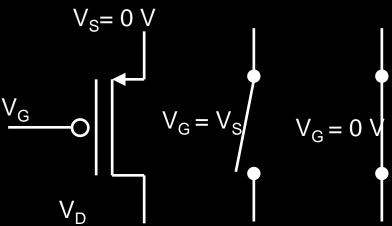

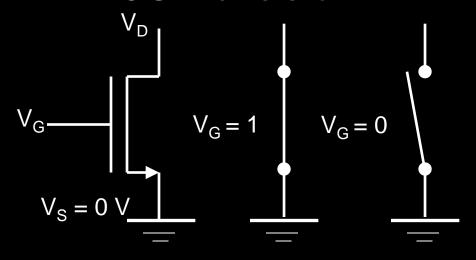

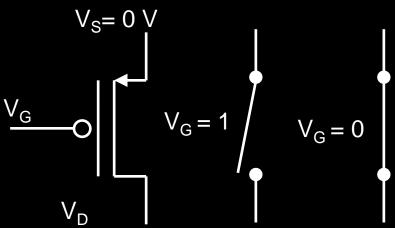

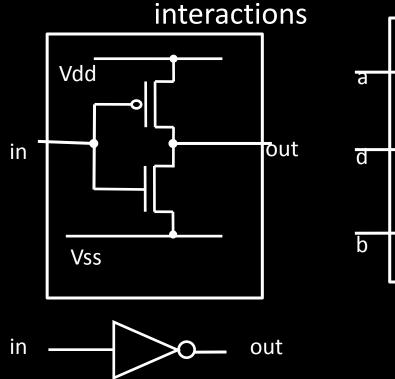

## **NMOS and PMOS Transistors**

NMOS Transistor

**PMOS Transistor**

- Connect source to drain when gate = 1

- N-channel

Connect source to drain when gate = 0

P-channel

## **NMOS and PMOS Transistors**

NMOS Transistor

**PMOS Transistor**

- Connect source to drain when gate = 1

- N-channel

Connect source to drain when gate = 0

P-channel

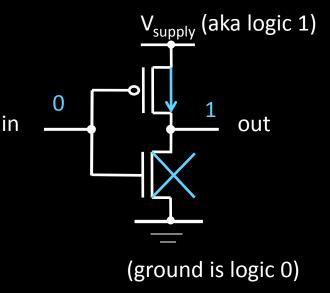

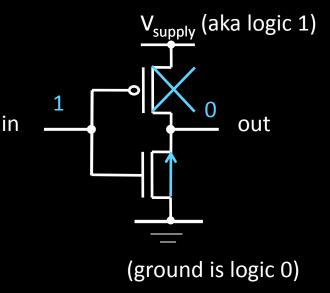

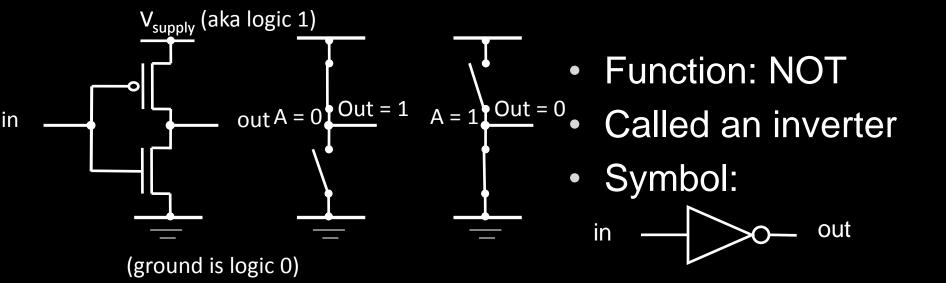

#### Inverter

- Function: NOT

- Called an inverter

- Symbol:

- Useful for taking the inverse of an input

- CMOS: complementary-symmetry metal-oxidesemiconductor

#### Inverter

- Function: NOT

- Called an inverter

- Symbol:

- Useful for taking the inverse of an input

- CMOS: complementary-symmetry metal-oxidesemiconductor

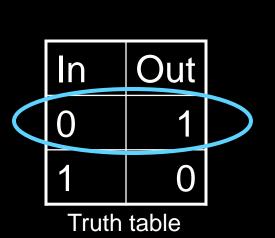

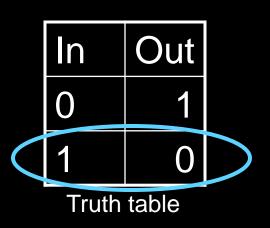

#### Inverter

| Α | Out |

|---|-----|

| 0 | 1   |

| 1 | 0   |

|   |     |

Truth table

- Useful for taking the inverse of an input

- CMOS: complementary-symmetry metal-oxidesemiconductor

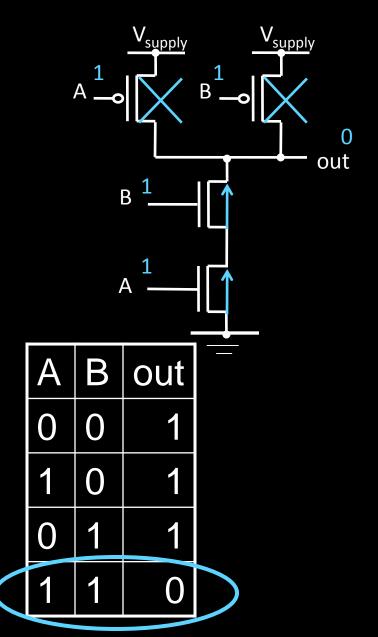

## **NAND** Gate

- Function: NAND

- Symbol:

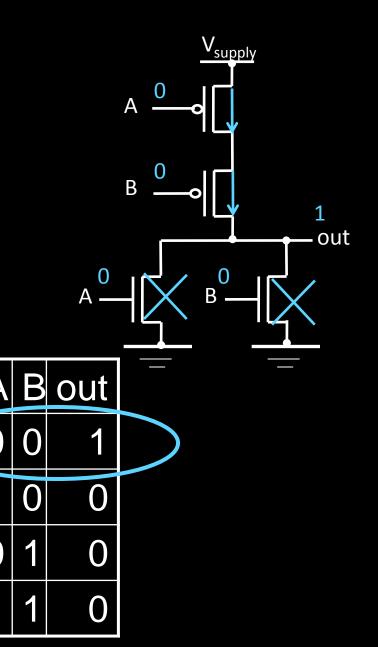

## **NOR Gate**

- Function: NOR

- Symbol:

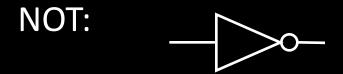

## **Building Functions (Revisited)**

AND:

OR:

#### NAND and NOR are universal

- Can implement any function with NAND or just NOR gates

- useful for manufacturing

## **Building Functions (Revisited)**

#### NAND and NOR are universal

- Can implement any function with NAND or just NOR gates

- useful for manufacturing

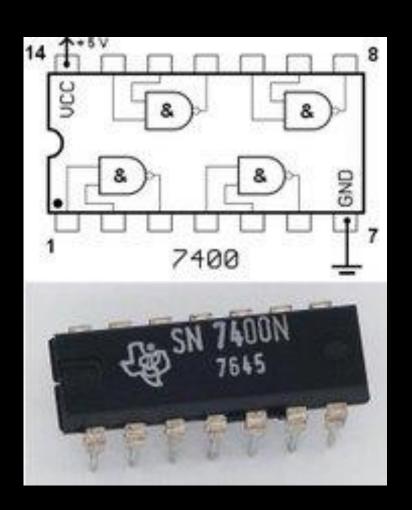

## **Logic Gates**

One can buy gates separately

- ex. 74xxx series of integrated circuits

- cost ~\$1 per chip, mostly for packaging and testing

Cumbersome, but possible to build devices using gates put together manually

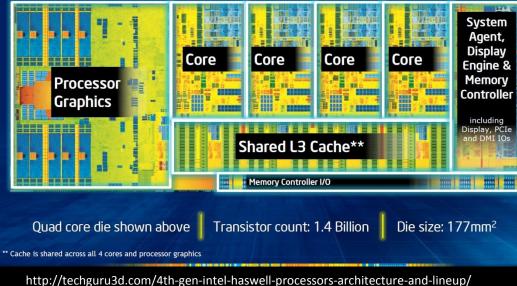

#### Then and Now

**4th Generation Intel® Core™ Processor Die Map**22nm Tri-Gate 3-D Transistors

#### The first transistor

- on a workbench at AT&T Bell Labs in 1947

- Bardeen, Brattain, and Shockley

#### An Intel Haswell

- 1.4 billion transistors

- 177 square millimeters

- Four processing cores

## Big Picture: Abstraction

Hide complexity through simple abstractions

- Simplicity

- Box diagram represents inputs and outputs

- Complexity

- Hides underlying NMOS- and PMOS-transistors and atomic

## Summary

# Most modern devices are made from billions of on /off switches called transistors

- We will build a processor in this course!

- Transistors made from semiconductor materials:

- MOSFET Metal Oxide Semiconductor Field Effect Transistor

- NMOS, PMOS Negative MOS and Positive MOS

- CMOS complementary MOS made from PMOS and NMOS transistors

- Transistors used to make logic gates and logic circuits

#### We can now implement any logic circuit

- Can do it efficiently, using Karnaugh maps to find the minimal terms required

- Can use either NAND or NOR gates to implement the logic circuit

- Can use P- and N-transistors to implement NAND or NOR gates